高精度直流電能表測(cè)試系統(tǒng)的研制

肖鵬, 侯瓊

(1.中國(guó)測(cè)試技術(shù)研究院電子研究所, 成都 610051; 2.成都理工大學(xué)核技術(shù)與自動(dòng)化工程學(xué)院, 成都 610051)

碳達(dá)峰、碳中和是一場(chǎng)極其廣泛深刻的綠色工業(yè)革命,具有極其重大的意義。中國(guó)許多行業(yè)如交通、建筑和冶金等領(lǐng)域在實(shí)施碳減排中一個(gè)重要的手段就是電氣化,使得這些行業(yè)的能效消耗由傳統(tǒng)的油氣煤轉(zhuǎn)換為電力消耗,電力行業(yè)的碳排放壓力陡然增加。在碳減排的背景下,直流電因其在傳輸、儲(chǔ)能和用電等方面的優(yōu)點(diǎn),催生了大量應(yīng)用,從源頭的清潔能源光伏發(fā)電,到特高壓直流輸電,以及末端的直流城軌鐵路交通供電系統(tǒng)、電動(dòng)汽車快充系統(tǒng)等,每一個(gè)環(huán)節(jié)無(wú)不大量使用了直流電,因此直流電對(duì)整個(gè)國(guó)家的節(jié)能減排、降碳增效具有重大意義。

直流電的廣泛應(yīng)用也帶動(dòng)了直流系統(tǒng)準(zhǔn)確計(jì)量測(cè)試需求,根據(jù)最新發(fā)布的直流電能表國(guó)際電工委員會(huì)(IEC)標(biāo)準(zhǔn),電壓等級(jí)在1 500 V以下的直流電能表準(zhǔn)確度分為0.5級(jí)和1級(jí),特定領(lǐng)域會(huì)用到更高準(zhǔn)確度的直流電能表,所以要求標(biāo)準(zhǔn)表測(cè)試準(zhǔn)確度達(dá)到0.02級(jí)才能滿足檢定標(biāo)準(zhǔn)。

目前國(guó)內(nèi)在該量級(jí)的直流電能表測(cè)試系統(tǒng)基本被國(guó)外的設(shè)備所壟斷,所以迫切需要研制國(guó)產(chǎn)化的計(jì)量標(biāo)準(zhǔn)表,滿足逐漸增加的直流電能表校準(zhǔn)需求。針對(duì)此現(xiàn)狀,現(xiàn)設(shè)計(jì)一套準(zhǔn)確度達(dá)到0.02級(jí),電壓測(cè)試范圍0~100 0 V,電流測(cè)試范圍0~200 A的直流電能表測(cè)試系統(tǒng)。作為計(jì)量標(biāo)準(zhǔn)用于直流電能參數(shù)的量值溯源,以期完善中國(guó)直流系統(tǒng)測(cè)量的量傳體系,實(shí)現(xiàn)高準(zhǔn)確度直流電能表測(cè)試系統(tǒng)的國(guó)產(chǎn)化。

1 總體設(shè)計(jì)

目前,國(guó)內(nèi)直流電能表測(cè)試方法主要分為兩種,一種方法是直接采用特定電能計(jì)量芯片,模數(shù)轉(zhuǎn)換器(analog-to-digital converter, ADC)和后級(jí)信號(hào)處理單元等全部集成于計(jì)量芯片內(nèi)部[1]。典型的電能計(jì)量芯片如亞德諾半導(dǎo)體公司推出的ADE7755,鉅泉公司推出的ATT7021,其準(zhǔn)確度均為0.1級(jí)。該方法具有低功耗、使用便捷、穩(wěn)定性好等優(yōu)點(diǎn),但其準(zhǔn)確度不夠高。另一種方法則是用高精度ADC完成信號(hào)采集,自主設(shè)計(jì)信號(hào)調(diào)理、采集以及參數(shù)計(jì)算等模塊。通過(guò)合理設(shè)計(jì),該方法具有準(zhǔn)確度高、自主可控等優(yōu)點(diǎn)。綜合考量后采用第二種方法。

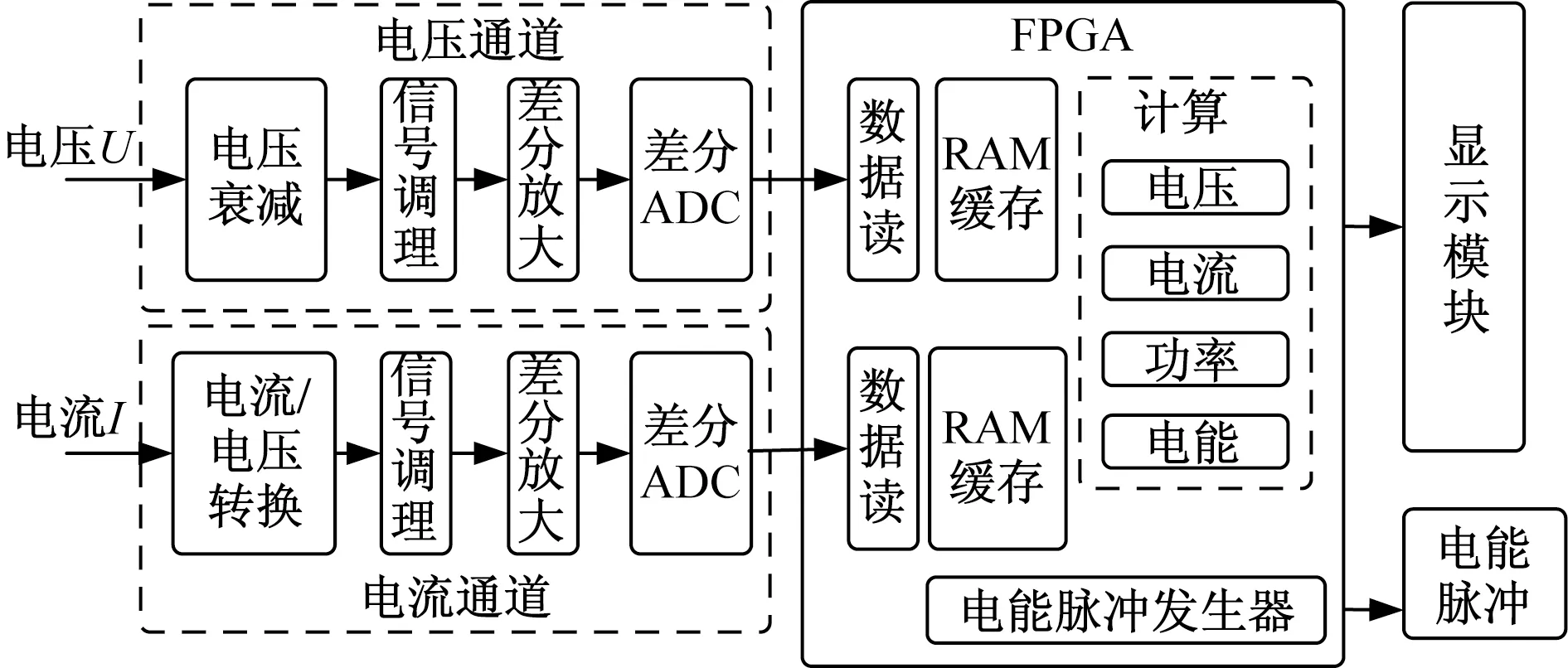

高精度直流電能測(cè)試系統(tǒng)設(shè)計(jì)了電壓、電流兩個(gè)獨(dú)立的采集通道分別進(jìn)行模擬信號(hào)采集[2]。在輸入端運(yùn)用多個(gè)精密采樣電阻及零磁通電流傳感器完成大電壓到小電壓,大電流到小電壓的轉(zhuǎn)換,使其技術(shù)指標(biāo)達(dá)到電壓測(cè)試量程0~1 000 V,電流測(cè)試量程0~200 A。轉(zhuǎn)換后的小電壓在電壓通道和電流通道內(nèi)分別進(jìn)行信號(hào)調(diào)理、差分放大和模數(shù)轉(zhuǎn)換;其中電壓、電流兩個(gè)通道分別采用兩個(gè)獨(dú)立的20位差分ADC采集來(lái)保證其高準(zhǔn)確度,并在現(xiàn)場(chǎng)可編程門(mén)陣列(field program gate way,FPGA)中完成電壓、電流、功率以及電能的計(jì)算,通過(guò)顯示模塊實(shí)時(shí)顯示測(cè)量后的參數(shù)結(jié)果,電能通過(guò)脈沖的形式輸出。總體設(shè)計(jì)如圖1所示。

圖1 總體設(shè)計(jì)Fig.1 Overall design

2 關(guān)鍵電路設(shè)計(jì)

2.1 電壓檢測(cè)

電壓檢測(cè)部分由分壓控制電路和模數(shù)轉(zhuǎn)換電路兩部分組成。

2.1.1 分壓控制電路

輸入電壓通過(guò)6個(gè)精密分壓電阻將輸入分成四檔,分別為1 V檔、10 V檔、100 V檔、和1 000 V檔,對(duì)應(yīng)其分壓比分別為1∶1、1∶10、1∶100、1∶1 000。分壓控制電路如圖2所示。

圖2 分壓控制電路Fig.2 Voltage dividing control circuit

為實(shí)現(xiàn)準(zhǔn)確且穩(wěn)定的分壓比,6個(gè)電阻均采用金箔電阻[3],該電阻阻值準(zhǔn)確度為±0.02%,保證了分壓比的準(zhǔn)確性;電阻溫漂非常低,僅有5×10-6℃-1,可以大大降低電阻發(fā)熱對(duì)分壓比穩(wěn)定性的影響。同時(shí)設(shè)計(jì)了3個(gè)300 kΩ的電阻代替一個(gè)大電阻,減小單獨(dú)電阻的分壓值,從而降低電阻電壓系數(shù)對(duì)分壓比的影響。

該裝置設(shè)計(jì)了自動(dòng)換檔功能,當(dāng)控制電路根據(jù)ADC檢測(cè)到輸入電壓溢出時(shí),換檔控制電路會(huì)將繼電器切換到最大量程;當(dāng)控制電路根據(jù)ADC檢測(cè)到輸入電壓小于總量程的10%時(shí),換檔控制電路會(huì)控制繼電器降低一個(gè)量程的檔位。

考慮到低電壓檔輸入高電壓時(shí),可能對(duì)芯片及電路產(chǎn)生不可逆的危害,因此設(shè)計(jì)了過(guò)壓保護(hù)電路。保護(hù)電路前端采用大功率氣體放電管,對(duì)整個(gè)裝置進(jìn)行防雷浪涌保護(hù);同時(shí)在保護(hù)電路后端設(shè)計(jì)了壓敏電阻和瞬態(tài)二極管(transient voltage suppressor,TVS)以及鉗位二極管電路[4],將輸入電壓始終鉗位在±5 V的安全范圍內(nèi)。

2.1.2 模數(shù)轉(zhuǎn)換

經(jīng)繼電器換擋衰減后的電壓范圍為0~1 V,由于差分ADC驅(qū)動(dòng)器輸入信號(hào)范圍在-3.28~+3.28 V,所以在信號(hào)調(diào)理部分通過(guò)一個(gè)精密運(yùn)算放大器LT1991將信號(hào)放大3.25倍,如圖3所示。由于該放大器內(nèi)部電阻溫度系數(shù)小于3×10-6℃-1,且電阻匹配度高,電壓放大倍數(shù)呈極線性,其增益非線性小于10×10-6℃-1,保證了信號(hào)準(zhǔn)確放大。

VIN為輸入電壓;VOUT為輸出電壓;VCC、VEE分別為正電壓和負(fù)電壓供電端;GAIN為增益倍數(shù);M9為9倍增益反相輸入端;M3為3倍增益反相輸入端;P9為9倍增益正相輸入端圖3 信號(hào)調(diào)理電路Fig.3 Signal conditioning circuit

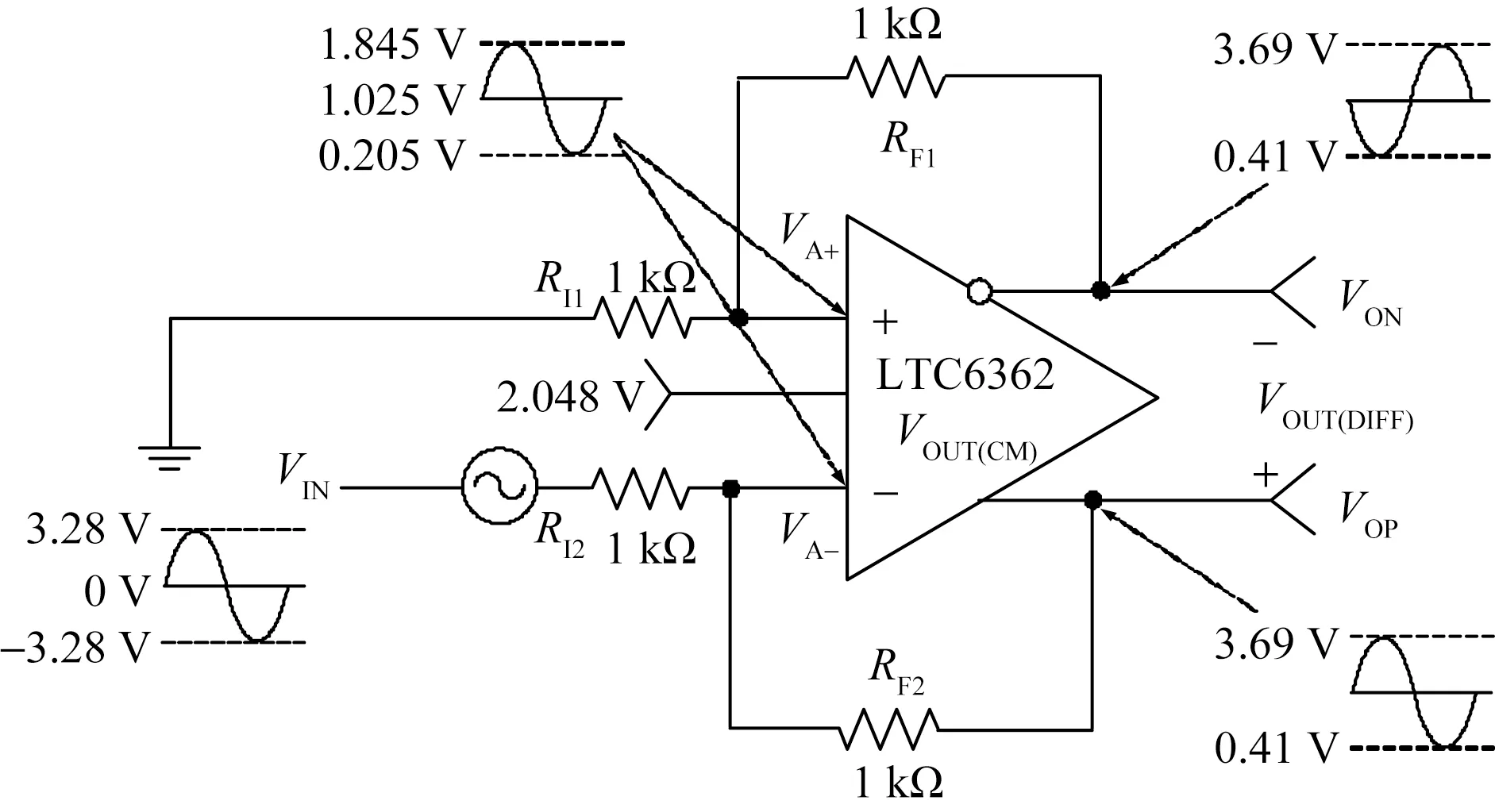

為了改善系統(tǒng)的總體性能,有效提高電路共模抑制比和抗干擾能力,采用差分ADC驅(qū)動(dòng)器LTC6362搭配差分模數(shù)轉(zhuǎn)換器使用,將單端電壓信號(hào)轉(zhuǎn)換為一對(duì)差分信號(hào)[5],且用一個(gè)四電阻網(wǎng)絡(luò)保證電阻匹配度。如圖4所示,輸入電壓范圍為-3.28~+3.28 V,輸出差分電壓范圍為0.41~3.69 V。

VIN為單端輸入電壓;VOUT(DIFF)為差模輸出;VOUT(CM)為共模輸出;VOCM為輸入?yún)⒖茧妷?RF1和RF2為兩個(gè)反饋電阻;RI1為驅(qū)動(dòng)器正相電阻;RI2為輸入端負(fù)載電阻;VOP和VON為輸出正負(fù)差分電壓圖4 差分ADC驅(qū)動(dòng)器Fig.4 Differential ADC driver

為簡(jiǎn)化表達(dá)式,定義兩個(gè)反饋因子β1、β2,如式(1)和式(2)所示。差模輸出和共模輸出如式(3)和式(4)所示。

(1)

(2)

VOUT(DIFF)=VOP-VON

(3)

(4)

差模輸出關(guān)系公式為

VIP(1-β1)-VIN(1-β2)]×

{1+2/[AS(β1+β2)]}-1

(5)

當(dāng)電阻對(duì)匹配度不高時(shí),β1≠β2,輸出差模電壓值受VOCM影響較大,在輸出信號(hào)中產(chǎn)生有害的共模分量和噪聲[6]。因此LTC6362的反饋電阻對(duì)采用了一個(gè)精確匹配的四電阻網(wǎng)絡(luò)LT5400,其最大0.01%的匹配誤差,0.2×10-6℃-1的溫漂性能足以保證反饋電阻的一致性。當(dāng)β1=β2,開(kāi)環(huán)電壓增益AS為無(wú)限大時(shí),式(5)可簡(jiǎn)化為式(6)。

(6)

此時(shí),內(nèi)部共模反饋環(huán)路迫使VOUT(CM)等于輸入端VOCM,差分ADC驅(qū)動(dòng)器輸出平衡,使得輸出的差分信號(hào)相位差為180°。

模數(shù)轉(zhuǎn)換器的性能決定了整個(gè)裝置的準(zhǔn)確度,因此為了計(jì)量性能達(dá)到0.02級(jí),保證足夠的分辨率,系統(tǒng)采用20位高精度模數(shù)轉(zhuǎn)換器LTC237620,模數(shù)轉(zhuǎn)換電路如圖5所示。

圖5 模數(shù)轉(zhuǎn)換電路圖Fig.5 A/D conversion circuit diagram

該ADC具有最高250 Ksps采樣率,其中Ksps表示每秒轉(zhuǎn)換次數(shù),即采樣千次每秒。同時(shí)其擁有極小的積分線性誤差±0.5×10-6℃-1。與模數(shù)轉(zhuǎn)換器配合使用的基準(zhǔn)電壓芯片是LTC6655,該芯片的低頻噪聲、溫漂都非常小,其長(zhǎng)期穩(wěn)定性也非常優(yōu)秀。整個(gè)模數(shù)轉(zhuǎn)換電路單元保證了整個(gè)系統(tǒng)的準(zhǔn)確度的要求[7]。

2.2 電流檢測(cè)

電流檢測(cè)分為電流采樣、過(guò)流保護(hù)、模數(shù)轉(zhuǎn)換3個(gè)部分,其中模數(shù)轉(zhuǎn)換部分與電壓檢測(cè)部分相同。

2.2.1 電流采樣

大電流采樣方法大致分為直接采樣和間接采樣兩種[8]。直接采樣為傳統(tǒng)的基于歐姆定律原理采樣,此方法由于采樣電阻在大電流下產(chǎn)生的高溫會(huì)導(dǎo)致不可避免的溫漂,影響采樣準(zhǔn)確度,所以測(cè)試系統(tǒng)采用間接采樣。

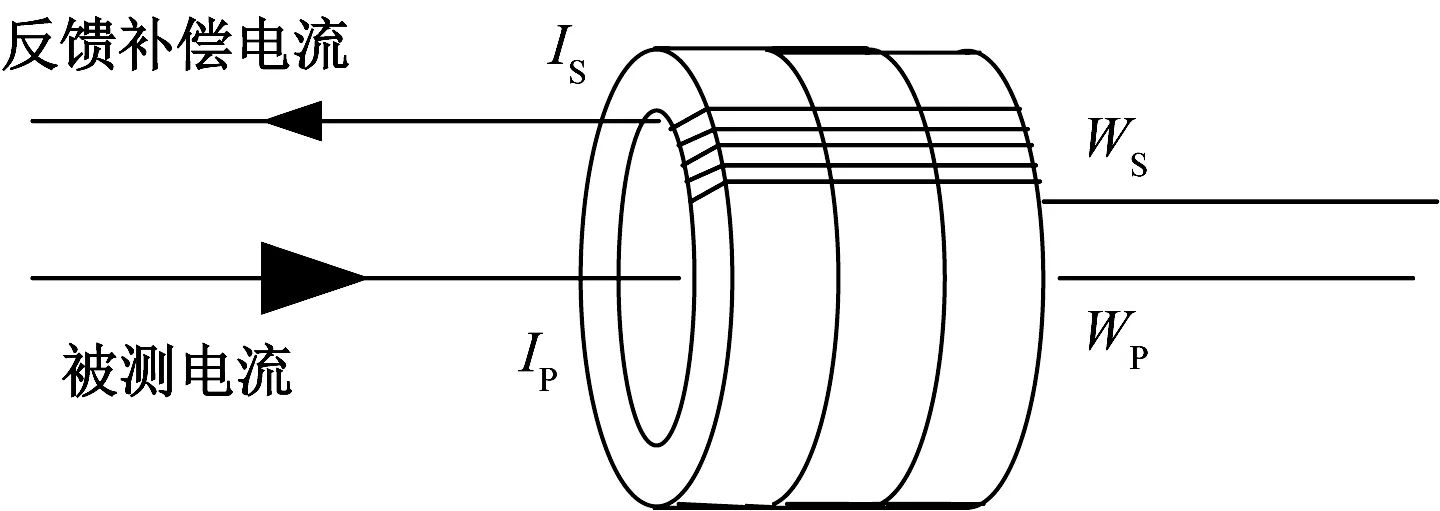

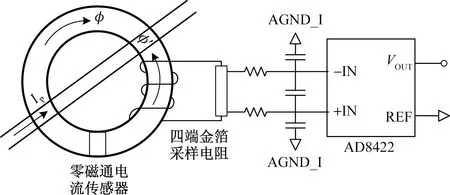

系統(tǒng)采用基于閉環(huán)反饋原理的自平衡式零磁通電流傳感器間接采樣,原理如圖6所示。

IS為反饋補(bǔ)償電流;IP為被測(cè)電流;WS為補(bǔ)償繞組匝數(shù);WS為被測(cè)電流的匝數(shù)圖6 測(cè)量原理Fig.6 Measuring principle

其基本原理是利用反饋回路使磁芯中磁通量自動(dòng)實(shí)時(shí)調(diào)零,即

IPWP=ISWS

(7)

根據(jù)反饋繞組的匝數(shù)比測(cè)電流值,取WP=1,公式為

(8)

傳統(tǒng)雙磁環(huán)結(jié)構(gòu)在解調(diào)二次諧波時(shí),采用“峰差”解調(diào)方式,在交流紋波過(guò)大時(shí),極易誘發(fā)系統(tǒng)振蕩,不穩(wěn)定。針對(duì)上述缺點(diǎn)。設(shè)計(jì)增加一個(gè)用于交流信號(hào)補(bǔ)償?shù)拇怒h(huán),構(gòu)成三磁環(huán)結(jié)構(gòu),及時(shí)響應(yīng)系統(tǒng)中交流紋波的影響,進(jìn)行自平衡電流補(bǔ)償,具體示意圖如圖7所示。

N1、N2、N3為3個(gè)坡莫合金磁環(huán);D1、D2、D3為3個(gè)磁環(huán)繞組;S為反饋繞組圖7 零磁通傳感器工作原理Fig.7 Working principle of zero flux sensor

在幾何尺寸和磁導(dǎo)率相同的兩個(gè)磁芯上繞上相同匝數(shù)的繞組,通過(guò)激勵(lì)電路使其處于深度飽和狀態(tài),將小的輸入直流信號(hào)調(diào)制為二次諧波信號(hào),通過(guò)相敏檢波電路轉(zhuǎn)換為放大的直流信號(hào)送入誤差放大電路,然后通過(guò)功率放大器在反饋繞組S處產(chǎn)生與被測(cè)電流IP相反的磁通,當(dāng)與IP產(chǎn)生的磁通大小相等,方向相反時(shí),磁環(huán)處于零磁通狀態(tài),此時(shí)通過(guò)測(cè)量流過(guò)標(biāo)準(zhǔn)電阻上的電壓就可獲得Is的大小,從而根據(jù)初級(jí)和次級(jí)的匝數(shù)比得出被測(cè)電流大小[9]。

經(jīng)傳感器衰減一千倍后的電流值范圍為0~200 mA,然后經(jīng)一個(gè)5 Ω四端金屬箔采樣電阻轉(zhuǎn)換為電壓值,范圍為0 ~1 V,最后通過(guò)模數(shù)轉(zhuǎn)換電路采集到FPGA中。電流采樣過(guò)程如圖8所示。

IP為待測(cè)原邊電流;φ′、φ分別為原邊電流感應(yīng)磁通以及反饋電流感生磁通;VOUT為輸出電壓;REF為參考電壓輸入端圖8 電流采樣過(guò)程Fig.8 Current sampling process

2.2.2 過(guò)流保護(hù)

過(guò)流保護(hù)電路由LM324和其外圍電路組成,LM324包含4個(gè)獨(dú)立運(yùn)算放大器。電路圖如圖9所示。

圖9中,輸入輸出關(guān)系公式為

VO=-VI1-2VI2

(9)

經(jīng)采樣電阻后的電壓信號(hào)VIN首先經(jīng)過(guò)電壓跟隨器U21A,當(dāng)VIN>0 V時(shí),U21D構(gòu)成一個(gè)電壓反向器,此時(shí)VI2=-VI1,U21B輸出VO=VI1;當(dāng)VIN<0 V時(shí),二極管D3導(dǎo)通,又由虛短知U21D的負(fù)輸入端電壓為0 V,則VI2=0 V,U21B輸出VO=-VI1。這樣3個(gè)運(yùn)算放大器U21A、U21B、U21D構(gòu)成一個(gè)絕對(duì)值電路。

由分壓電路得VF=1.2 V,所以當(dāng)輸入電流大于±240 A時(shí),電流衰減分壓后得到的|VIN|>1.2 V,VO>1.2 V,U21C從高電平變?yōu)榈碗娖?通過(guò)光耦高速控制器,從而控制繼電器動(dòng)作,阻止電壓輸出到后級(jí)電路,達(dá)到保護(hù)電路的目的。

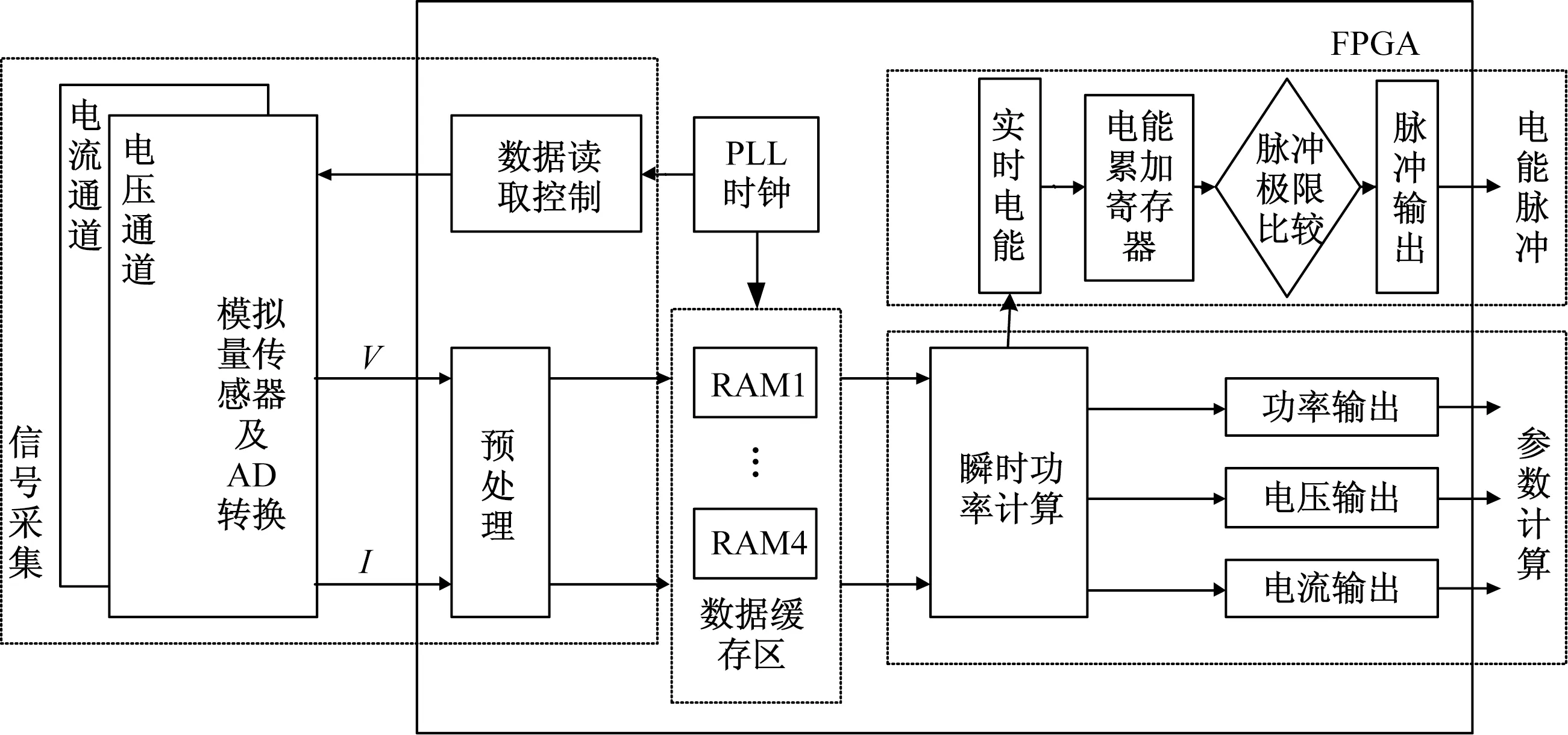

2.3 FPGA邏輯設(shè)計(jì)

為了提高參數(shù)計(jì)算的速度和設(shè)計(jì)靈活性。測(cè)試系統(tǒng)采用可編程門(mén)陣列FPGA來(lái)處理ADC輸出數(shù)據(jù),充分利用FPGA并行執(zhí)行指令和硬件可編程重構(gòu)的優(yōu)勢(shì)進(jìn)行實(shí)時(shí)參數(shù)計(jì)算和電能脈沖輸出[10]。FPGA邏輯設(shè)計(jì)分為數(shù)據(jù)讀取、數(shù)據(jù)緩存、參數(shù)計(jì)算、電能脈沖4個(gè)部分。總體邏輯設(shè)計(jì)框圖如圖10所示。

圖10 總體邏輯設(shè)計(jì)框圖Fig.10 Overall logic design block diagram

2.3.1 數(shù)據(jù)讀取

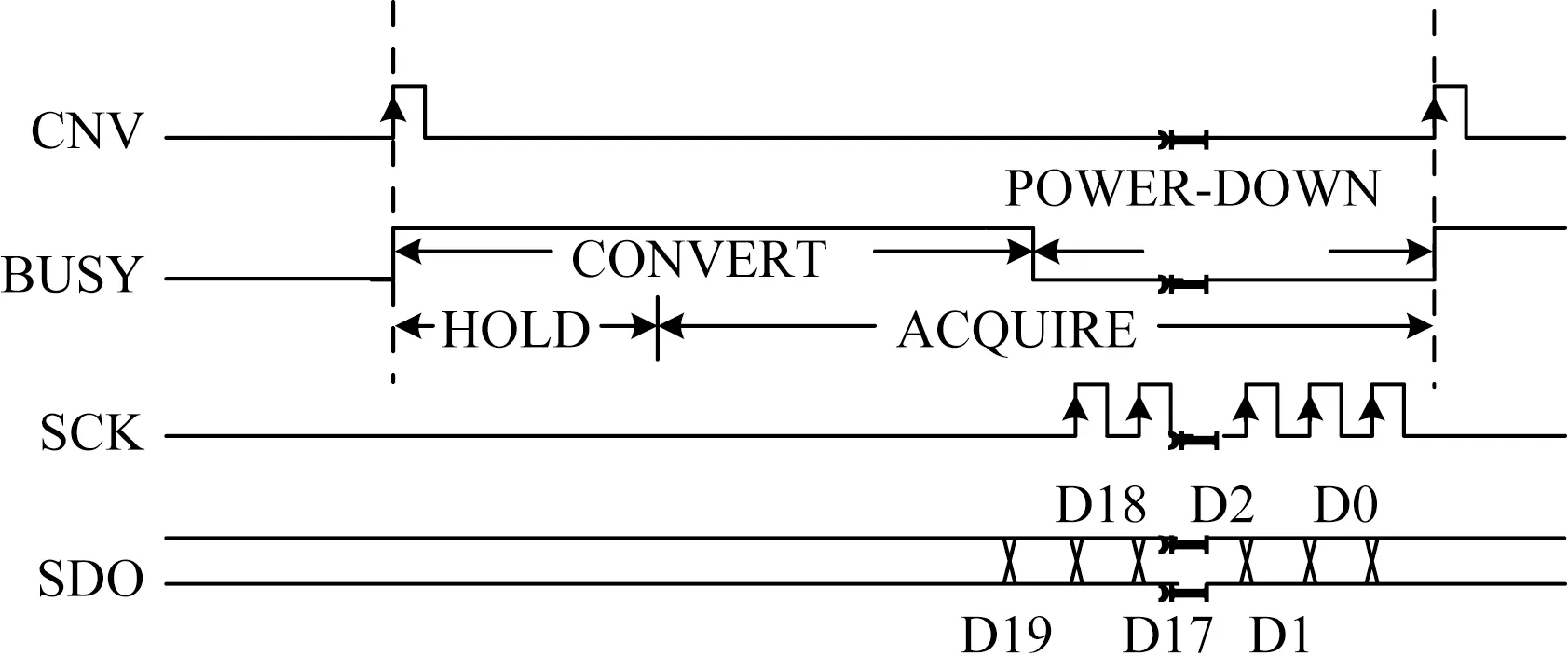

模數(shù)轉(zhuǎn)換器LTC237620兼容SPI(Serial Perripheral Interface,串行外圍設(shè)備接口)高速全雙工串行接口,ADC工作時(shí)序如圖11所示。

圖11 ADC工作時(shí)序圖Fig.11 ADC working time sequence diagram

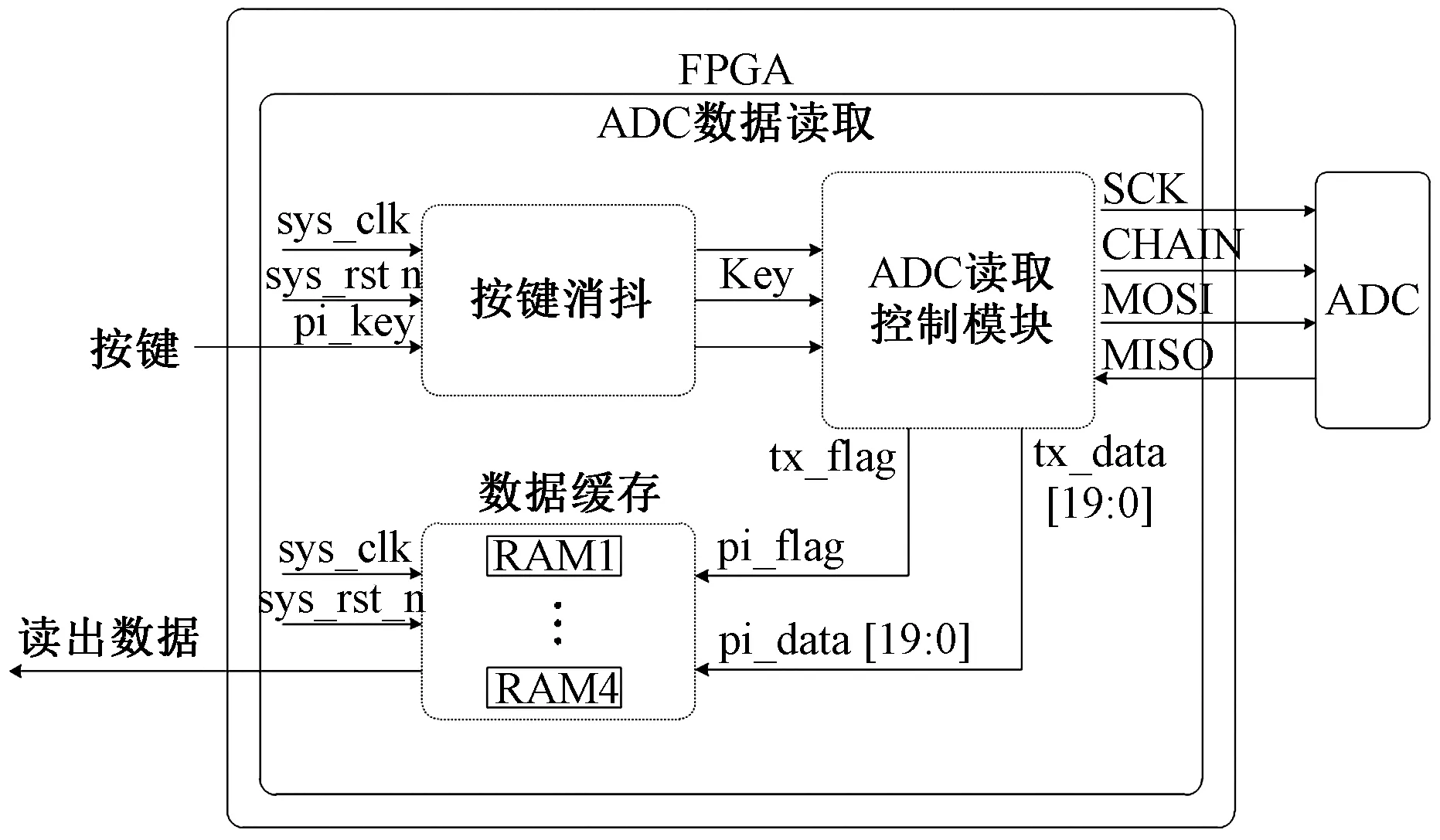

外部按鍵控制開(kāi)始采集后FPGA輸出一個(gè)時(shí)鐘周期高電平的轉(zhuǎn)換啟動(dòng)標(biāo)志信號(hào)CNV,然后ADC發(fā)出應(yīng)答信號(hào)并開(kāi)始模數(shù)轉(zhuǎn)換,在模數(shù)轉(zhuǎn)換完成后轉(zhuǎn)換忙碌信號(hào)BUSY和模式選擇信號(hào)CHAIN信號(hào)拉低,開(kāi)始數(shù)據(jù)讀操作,數(shù)據(jù)輸出端口MISO在時(shí)鐘SCK控制下輸出20位串行數(shù)據(jù)。由于系統(tǒng)ADC采樣率設(shè)定為100 Ksps,即采樣周期T為10 μs,所以數(shù)據(jù)讀取模塊每10 μs向ADC讀一次值。FPGA數(shù)據(jù)讀取模塊從機(jī)連接圖如圖12所示。

圖12 數(shù)據(jù)讀取從機(jī)連接圖Fig.12 Data reading slave connection diagram

為了保證在每一位數(shù)據(jù)穩(wěn)定時(shí)讀出,SPI通信協(xié)議根據(jù)時(shí)鐘極性和時(shí)鐘相位定義區(qū)分了4種通信模式來(lái)規(guī)定數(shù)據(jù)讀取和數(shù)據(jù)更新的時(shí)序,系統(tǒng)采用模式0,即空閑狀態(tài)時(shí)串行時(shí)鐘SCK為低電平,數(shù)據(jù)在 SCK時(shí)鐘的奇數(shù)邊沿進(jìn)行讀取,在 SCK 時(shí)鐘的偶數(shù)邊沿進(jìn)行更新。當(dāng)20位數(shù)據(jù)讀取完畢后進(jìn)行串轉(zhuǎn)并操作,至此一個(gè)完整數(shù)據(jù)讀取完成,系統(tǒng)進(jìn)入等待狀態(tài)直到下一次轉(zhuǎn)換啟動(dòng)標(biāo)志拉高。兩次讀取間隔時(shí)間為10 μs。數(shù)據(jù)讀取模塊劃分如圖13所示。

圖13 數(shù)據(jù)讀取模塊劃分Fig.13 Division of data reading module

頂層文件下實(shí)例化3個(gè)子模塊,分別為按鍵消抖模塊、讀取控制模塊、數(shù)據(jù)緩存模塊。所有的時(shí)序邏輯控制在讀取控制模塊內(nèi)完成。

2.3.2 數(shù)據(jù)緩存

為了防止可能出現(xiàn)的電流電壓輸出不同步的問(wèn)題,并為大量采集信號(hào)提供一個(gè)暫存區(qū)便于后級(jí)模塊有序處理[11]。采用乒乓操作緩存讀出數(shù)據(jù),4個(gè)雙口隨機(jī)存取存儲(chǔ)器(random access memory,RAM)分為兩組存儲(chǔ)單元分別緩存電壓和電流信號(hào)。通過(guò)兩個(gè)存儲(chǔ)單元按節(jié)拍,相互配合的切換可以保證數(shù)據(jù)連續(xù)不斷的輸出到參數(shù)計(jì)算模塊,乒乓操作示意圖如圖14所示。

圖14 乒乓操作示意圖Fig.14 Ping pong operation diagram

以電壓數(shù)據(jù)緩存為例,選擇位寬20位,存儲(chǔ)深度128的雙口RAM。乒乓操作流程可分為4個(gè)狀態(tài),IDLE為初始狀態(tài),在寫(xiě)數(shù)據(jù)使能打開(kāi)時(shí)切換到RAM1寫(xiě)狀態(tài)WRAM1,在該狀態(tài)下將第一個(gè)含128個(gè)電壓值的數(shù)據(jù)包寫(xiě)入RAM1中。第一個(gè)數(shù)據(jù)包寫(xiě)入完成時(shí)程序跳轉(zhuǎn)到寫(xiě)RAM2讀RAM1狀態(tài),在RAM2寫(xiě)完成時(shí)RAM1數(shù)據(jù)剛好讀出,隨后跳轉(zhuǎn)到寫(xiě)RAM1讀RAM2狀態(tài),如此循環(huán)直至采集停止信號(hào)拉高跳轉(zhuǎn)到初始狀態(tài)待命。如圖15所示為數(shù)據(jù)緩存模塊劃分。

圖15 數(shù)據(jù)緩存模塊劃分Fig.15 Division of data cache module

頂層文件中實(shí)例化5個(gè)子模塊。由緩存單元控制模塊產(chǎn)生的讀寫(xiě)使能信號(hào)和地址信號(hào)、時(shí)鐘控制模塊產(chǎn)生的讀寫(xiě)時(shí)鐘共同作用使得RAM0和RAM1有條不紊地工作,源源不斷地為后級(jí)處理模塊提供電壓電流數(shù)據(jù)。

程序設(shè)計(jì)中,由于RAM在讀數(shù)據(jù)或?qū)憯?shù)據(jù)操作都是在時(shí)鐘上升沿進(jìn)行,因此為保證讀和寫(xiě)數(shù)據(jù)的穩(wěn)定性,使用時(shí)鐘下降沿來(lái)產(chǎn)生使能、地址等控制信號(hào)。

利用modelsim仿真驗(yàn)證數(shù)據(jù)緩存模塊,激勵(lì)測(cè)試文件產(chǎn)生一組8位的輸入數(shù)據(jù),并觀察狀態(tài)機(jī)各狀態(tài)時(shí)序都能達(dá)到設(shè)計(jì)要求。乒乓操作輸出數(shù)據(jù)仿真波形圖如圖16所示。

圖16 乒乓操作輸出數(shù)據(jù)仿真波形圖Fig.16 Ping pong operation output data simulation waveform

圖16中紅色方框中為乒乓操作輸出的數(shù)據(jù),程序下載后使用Quartus軟件的SignalTap在線邏輯分析儀實(shí)時(shí)抓取輸出數(shù)據(jù)如圖17所示。

圖17 Signal Tap實(shí)時(shí)抓取數(shù)據(jù)波形圖Fig.17 Waveform of signal tap real time capture data

實(shí)時(shí)抓取的輸出數(shù)據(jù)與仿真輸出數(shù)據(jù)對(duì)比一致,至此乒乓操作時(shí)序驗(yàn)證完成。

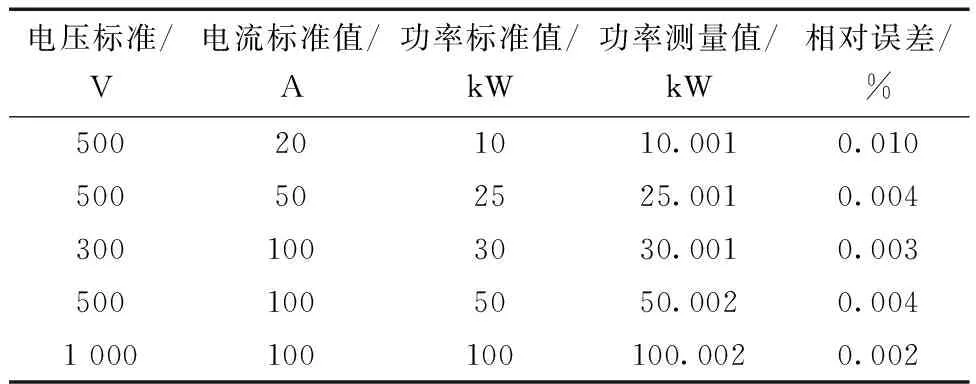

2.3.3 參數(shù)計(jì)算

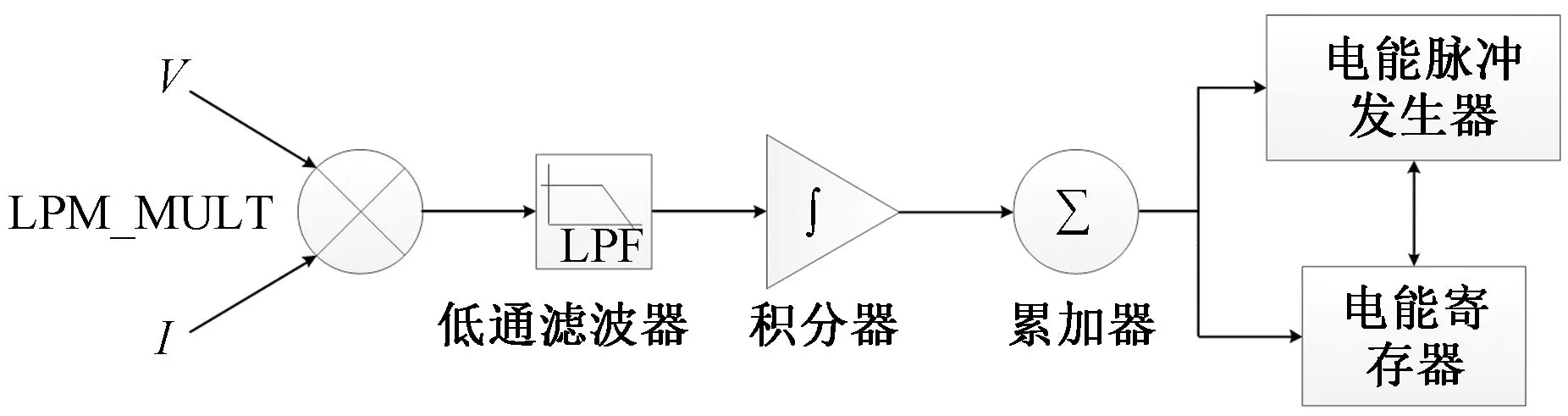

緩存模塊每10 μs輸出的電壓和電流值進(jìn)入?yún)?shù)計(jì)算模塊進(jìn)行功率、電能的計(jì)算,如圖18所示。

圖18 參數(shù)計(jì)算Fig.18 Parameter calculation

2.3.4 電能脈沖

電能脈沖模塊會(huì)先獲取手動(dòng)設(shè)置好的電能脈沖極限值Em,即每產(chǎn)生一次脈沖信號(hào)所代表的電能值。隨后累加器在每送入一次電能值時(shí)將累加值與脈沖極限值進(jìn)行比較,若大于脈沖極限值則輸出一個(gè)脈沖,其脈寬和占空比隨脈沖極限值和功率變化而變化,同時(shí)從累加器中減掉一個(gè)脈沖極限值,剩余部分∑E-Em作為下一次的累加初值,如圖19所示。

圖19 電能脈沖產(chǎn)生Fig.19 Electric energy pulse generation

產(chǎn)生的電能脈沖頻率表征當(dāng)前功率的大小,脈沖計(jì)數(shù)器的值表征累積電能的大小[12]。

圖20為直流電能表測(cè)試系統(tǒng)實(shí)物圖,圖21為實(shí)驗(yàn)室環(huán)境現(xiàn)場(chǎng)測(cè)試圖。

圖20 直流電能表測(cè)試系統(tǒng)實(shí)物圖Fig.20 Physical picture of DC energy meter test system

圖21 實(shí)驗(yàn)室環(huán)境現(xiàn)場(chǎng)測(cè)試圖Fig.21 Field test picture of laboratory environment

3 驗(yàn)證測(cè)試

系統(tǒng)的準(zhǔn)確度驗(yàn)證測(cè)試采用已溯源受控的直流電能表檢定標(biāo)準(zhǔn)源,該裝置具有最大1 150 V電壓輸出和600 A電流輸出,電壓、電流、電能準(zhǔn)確度達(dá)到0.01級(jí)。

3.1 電壓電流測(cè)試結(jié)果

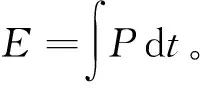

高精度直流電能表測(cè)試系統(tǒng)電壓測(cè)試結(jié)果如表1所示。

表1 電壓測(cè)試結(jié)果Table 1 Voltage test results

由表1可以看到,在不同標(biāo)準(zhǔn)電壓輸入時(shí),測(cè)試值相對(duì)誤差在0.01%以內(nèi),這是因?yàn)檫x擇了合適的分壓比,且采用溫漂極低的金箔電阻,最大限度地減少了電阻溫度升高對(duì)測(cè)量準(zhǔn)確度的影響。

高精度直流電能表測(cè)試系統(tǒng)電流測(cè)試結(jié)果如表2所示。

表2 電流測(cè)試結(jié)果Table 2 Current test results

由于使用了高準(zhǔn)確度的零磁通電流采樣技術(shù),所以表2中電流測(cè)試相對(duì)誤差均保持在0.01%以內(nèi)。測(cè)試10 A電流較其他電流相對(duì)誤差要大一些,這是因?yàn)榱愦磐娏鱾鞲衅鞯牧砍淌?00 A,10 A點(diǎn)在整個(gè)量程的低端,因此在該點(diǎn)的電流準(zhǔn)確度較其他點(diǎn)較差。

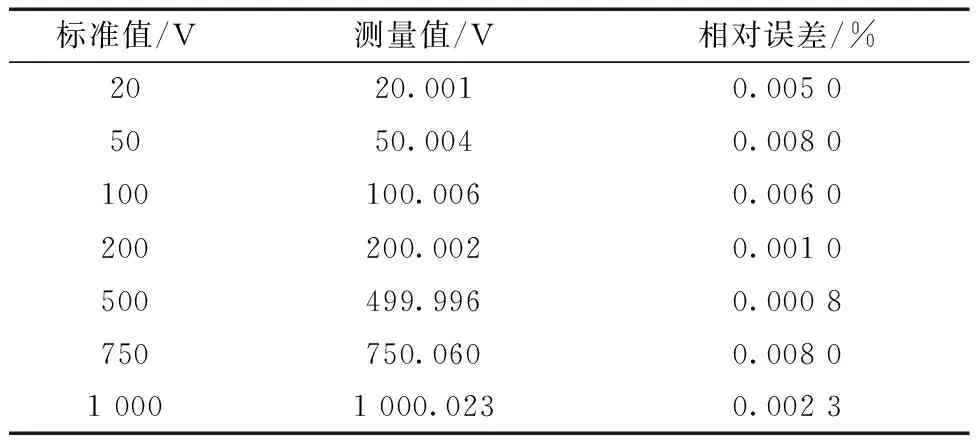

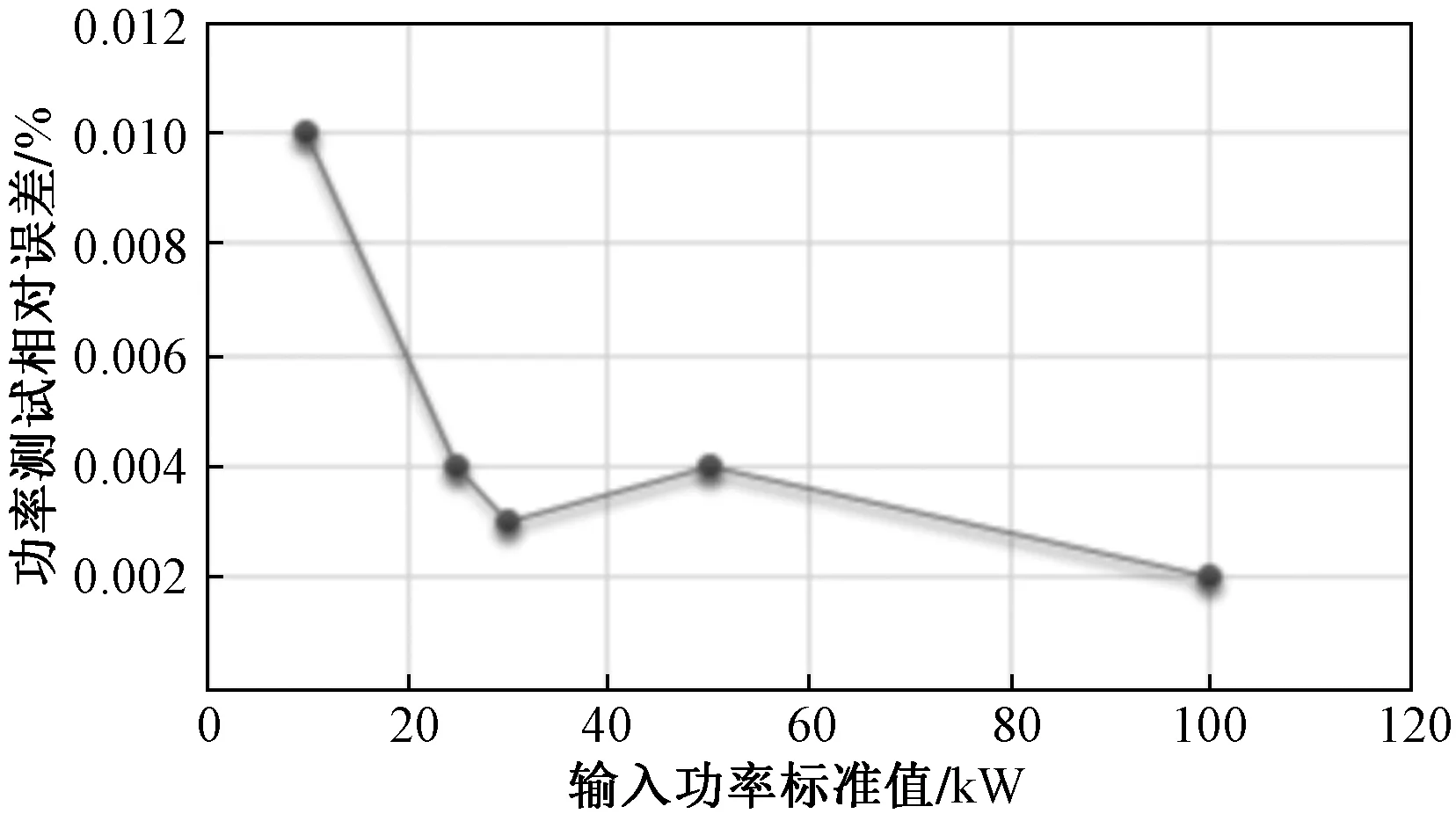

3.2 功率測(cè)試結(jié)果

高精度直流電能表測(cè)試系統(tǒng)功率測(cè)試結(jié)果如表3所示,功率測(cè)試相對(duì)誤差如圖22所示。

表3 功率測(cè)試結(jié)果Table 3 Power test results

圖22 功率測(cè)試相對(duì)誤差Fig.22 Relative error of power test

功率值由電流電壓測(cè)試值相乘得到,因?yàn)殡娏麟妷簻y(cè)試相對(duì)誤差均在0.01%以內(nèi),所以表3測(cè)試結(jié)果中,功率相對(duì)誤差也在0.01%以下。

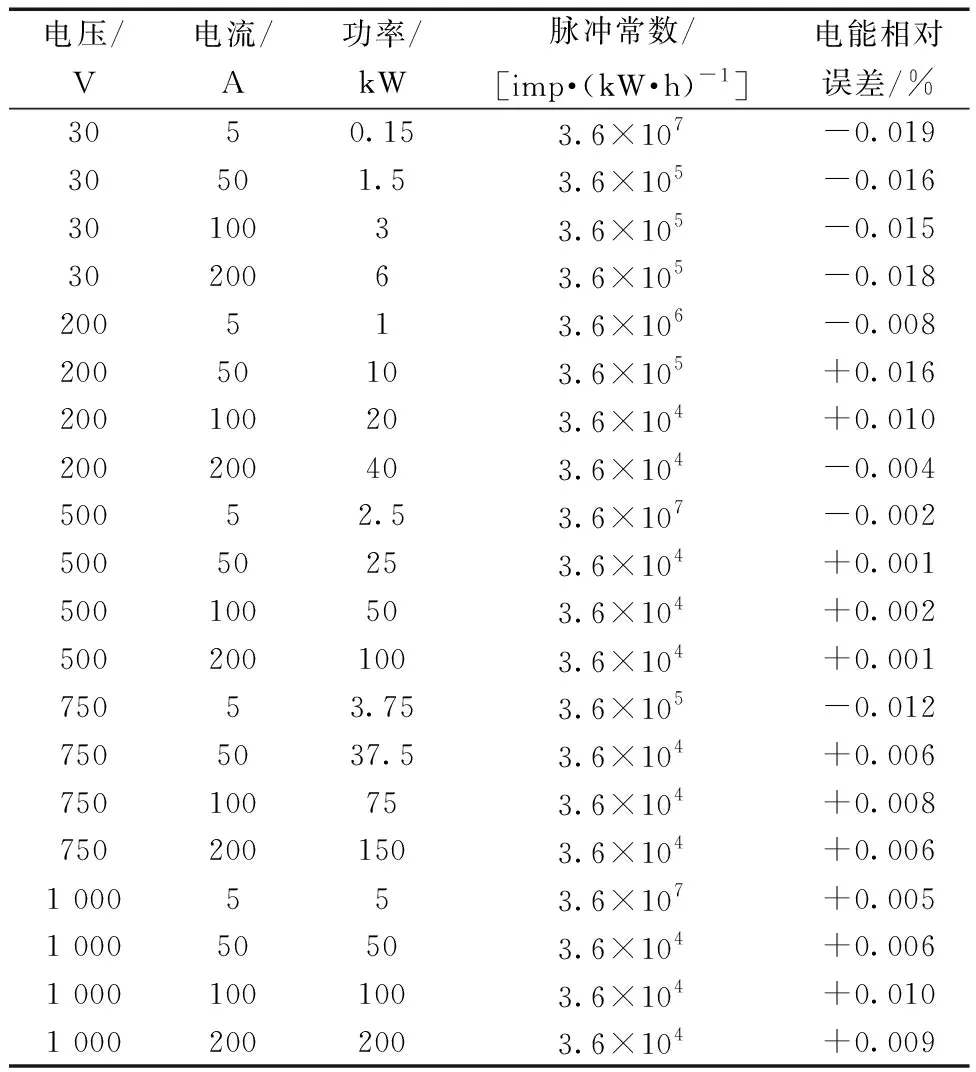

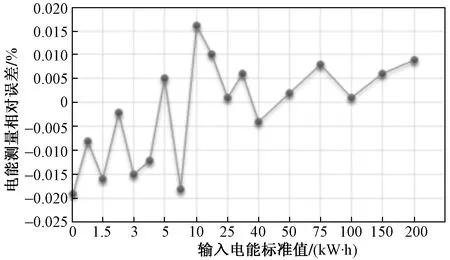

3.3 電能測(cè)試結(jié)果

高精度直流電能表測(cè)試系統(tǒng)電能測(cè)試結(jié)果如表4所示,電能相對(duì)誤差如圖23所示。

表4 電能測(cè)試結(jié)果Table 4 Electric energy test results

圖23 電能測(cè)試相對(duì)誤差Fig.23 Relative error of electric energy test

表4中,脈沖常數(shù)為消耗1 kW·h電能發(fā)出的脈沖數(shù),其值根據(jù)功率大小設(shè)定,功率越小,脈沖常數(shù)值越大,以保證發(fā)出的脈沖頻率在檢測(cè)范圍內(nèi)。由圖18中數(shù)據(jù)可以發(fā)現(xiàn),在不同輸入功率下,電能相對(duì)誤差均控制在±0.02%以內(nèi),滿足電能測(cè)試0.02級(jí)的標(biāo)準(zhǔn)要求。

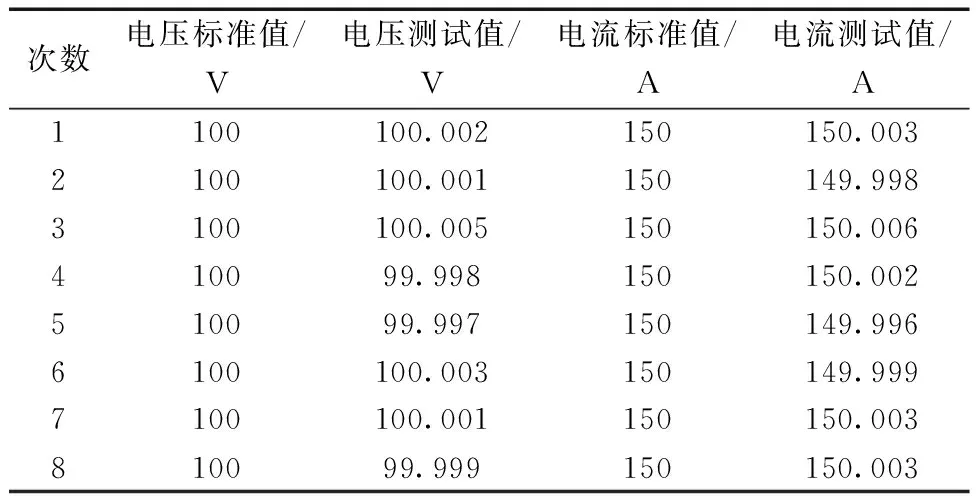

3.4 系統(tǒng)穩(wěn)定性測(cè)試

測(cè)試系統(tǒng)的重復(fù)測(cè)量穩(wěn)定性也是衡量一個(gè)設(shè)備性能的重要因素,以輸入標(biāo)準(zhǔn)電壓100 V和標(biāo)準(zhǔn)電流150 A為測(cè)試條件,重復(fù)測(cè)試8次的結(jié)果如表5所示。

表5 重復(fù)測(cè)試穩(wěn)定性Table 5 Repeated test stability

標(biāo)準(zhǔn)差可以反映一個(gè)數(shù)據(jù)集相對(duì)于平均值的離散程度,用σu和σi分別表示電壓測(cè)試值和電流測(cè)試值的標(biāo)準(zhǔn)差,根據(jù)式(10)可得到σu=0.007,σi=0.003。充分說(shuō)明測(cè)試系統(tǒng)的高重復(fù)測(cè)試穩(wěn)定性。

(10)

3.5 系統(tǒng)具體應(yīng)用及優(yōu)勢(shì)

標(biāo)準(zhǔn)表法也是直流電能表檢定中常用的一種方法,系統(tǒng)即用標(biāo)準(zhǔn)表法完成對(duì)直流電能表的檢定。其基本原理是通過(guò)比較待檢電能表和標(biāo)準(zhǔn)電能表輸出的電能,計(jì)算出待檢電能表的誤差,從而判斷待檢電能表的準(zhǔn)確度是否符合要求。被檢表相對(duì)誤差ε計(jì)算公式為

(11)

式(11)中:m為實(shí)測(cè)脈沖數(shù);m0為算定(或預(yù)置)的脈沖數(shù),m0計(jì)算公式為

(12)

式(12)中:N為被檢表電能脈沖數(shù);C0為標(biāo)準(zhǔn)表的脈沖常數(shù),imp/(kW·h);CL為被檢表的電能脈沖常數(shù);KI和KU為標(biāo)準(zhǔn)表外接的電流電壓傳感器變化值,當(dāng)沒(méi)有外接電流、電壓傳感器時(shí),KI和KU都為1。

以直流充電樁檢定場(chǎng)景為例,各部分連接如圖24所示。

圖24 直流充電樁的檢定Fig.24 Verification of DC charging station

將直流電能表測(cè)試儀設(shè)置在充電樁和負(fù)載箱的充電線路中,配合電能脈沖計(jì)算出工作誤差或顯示誤差。

相對(duì)于市場(chǎng)上其他直流測(cè)試系統(tǒng),該系統(tǒng)優(yōu)勢(shì)主要體現(xiàn)在其高準(zhǔn)確度、寬量程、自動(dòng)切換測(cè)量檔位上。可以適應(yīng)多種有高準(zhǔn)確性需求的直流電場(chǎng)景,且使用方便,操作簡(jiǎn)便。同時(shí),系統(tǒng)采用的分模塊自主設(shè)計(jì)還提高了設(shè)備的開(kāi)發(fā)靈活性和維護(hù)便捷性。

4 結(jié)論

為響應(yīng)直流電測(cè)領(lǐng)域?qū)Ω咝阅軝z定儀表的迫切需求,研制了一種用于直流電參數(shù)檢定的高精度、寬量程直入式標(biāo)準(zhǔn)表。系統(tǒng)以FPGA作為主控芯片,自主設(shè)計(jì)了電源部分、信號(hào)采集、信號(hào)調(diào)理電路等分立模塊,使得系統(tǒng)具備快捷靈活的后期維護(hù)和擴(kuò)展能力,從而適應(yīng)紛繁的應(yīng)用場(chǎng)景,比如系統(tǒng)可擴(kuò)展通信接口實(shí)現(xiàn)數(shù)據(jù)的遠(yuǎn)程傳輸;還可通過(guò)細(xì)化測(cè)試檔位、調(diào)整分壓比來(lái)提高小信號(hào)測(cè)試準(zhǔn)確度等。經(jīng)驗(yàn)證,高精度直流電能表測(cè)試系統(tǒng)滿足0.02級(jí)測(cè)試準(zhǔn)確度要求,在直流電測(cè)領(lǐng)域有著廣闊的應(yīng)用前景。