基于FPGA 的高速串行收發(fā)器TLK2711全雙工通信協(xié)議設(shè)計(jì)

杜建鵬

(甘肅電器科學(xué)研究院,甘肅蘭州 730900)

隨著計(jì)算機(jī)技術(shù)和通信技術(shù)的發(fā)展,系統(tǒng)級(jí)的互聯(lián)已達(dá)到Gbps 的傳輸速率。并行傳輸技術(shù)可以提高芯片與芯片之間、背板與背板之間的數(shù)據(jù)吞吐量,但總線數(shù)呈的增多及傳輸速率的加快會(huì)使PCB 布線的難度提高,并且增加了信號(hào)的延時(shí)和偏移[1-2]。而串行傳輸技術(shù)充分利用傳輸媒體的信道容量,可減少所需的連接器引腳數(shù)目、降低芯片外圍引腳數(shù)、設(shè)備及電纜布線更為簡(jiǎn)單、系統(tǒng)抗干擾能力更強(qiáng)[3],因此串行傳輸技術(shù)重新返回到高速傳輸領(lǐng)域并迅速取代了傳統(tǒng)的并行傳輸技術(shù)[4]。8b/10b編碼SerDes 是目前許多高速串行總線采用的編碼機(jī)制和結(jié)構(gòu),如PCI Express、光纖通道、TLK2711等。其中TLK2711 作為高速串行總線的物理層,被廣泛用于空間遙感以及衛(wèi)星圖像的數(shù)據(jù)傳輸系統(tǒng)中[5-7]。系統(tǒng)之間的數(shù)據(jù)傳輸必須制定相應(yīng)的協(xié)議。雖然符合規(guī)范的標(biāo)準(zhǔn)協(xié)議(如XILINX 公司為自己FPGA 內(nèi)嵌的Rocket IO 制定的AURORA 協(xié)議)傳輸速度和精度非常高,但是這些標(biāo)準(zhǔn)協(xié)議具有大量通信冗余數(shù)據(jù)和格式定義弊端,會(huì)導(dǎo)致通信延時(shí)和系統(tǒng)資源浪費(fèi)。因此,為了提高系統(tǒng)的可靠性和節(jié)約系統(tǒng)資源,本文基于FPGA+TLK2711 平臺(tái)設(shè)計(jì)了一種輕量級(jí)的高速串行全雙工通信協(xié)議,該協(xié)議為點(diǎn)對(duì)點(diǎn)鏈路層串行協(xié)議,經(jīng)測(cè)試可實(shí)現(xiàn)1.6Gbps~2.7Gbps 的可靠串行數(shù)據(jù)傳輸。

1 TLK2711 芯片簡(jiǎn)介

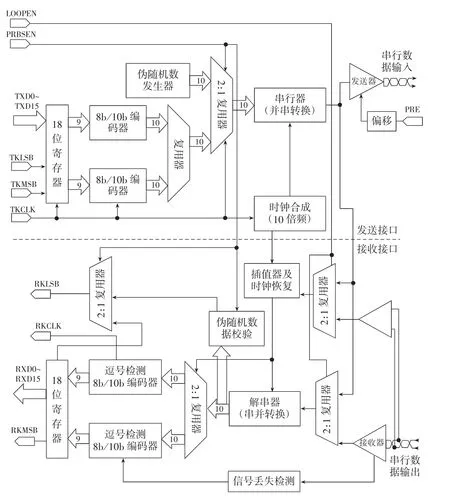

TLK2711 是千兆高速收發(fā)器,可用于高速點(diǎn)對(duì)點(diǎn)的雙向數(shù)據(jù)傳輸系統(tǒng)。TLK2711 在發(fā)送端將并行信號(hào)轉(zhuǎn)換為高速串行信號(hào),在接收端高速串行信號(hào)被轉(zhuǎn)換為并行信號(hào),也被稱為SerDes(SERializer/DESerializer)收發(fā)器,其工作原理如圖1 所示。在發(fā)送端,TLK2711 將輸入的16 位數(shù)據(jù)(TXD0~TXD15)分為兩個(gè)字節(jié),在TKLSB 和TKMSB 信號(hào)的配合下送入兩個(gè)8b/10b 編碼器進(jìn)行編碼,產(chǎn)生的10 位數(shù)據(jù)經(jīng)多路復(fù)用器進(jìn)入串行器,最后通過(guò)具有預(yù)加重功能的發(fā)送器以差分信號(hào)的方式輸出。在接收端,TLK2711 接收到串行差分信號(hào),首先通過(guò)恢復(fù)時(shí)鐘對(duì)數(shù)據(jù)進(jìn)行同步,其次通過(guò)解串器進(jìn)行串并轉(zhuǎn)換,利用兩個(gè)獨(dú)立的逗點(diǎn)檢測(cè)(Comma Detect)和8b/10b 解碼器完成數(shù)據(jù)解碼和字對(duì)齊,最后輸出16 位并行數(shù)據(jù)(RXD0~RXD15)以及RKLSB 和RKMSB 信號(hào)。圖中LOOPEN為環(huán)回使能信號(hào),使能后可以進(jìn)行環(huán)回測(cè)試;PRBSEN 為偽隨機(jī)測(cè)試使能信號(hào),可利用芯片中的偽隨機(jī)數(shù)發(fā)生器產(chǎn)生偽隨機(jī)信號(hào),進(jìn)行測(cè)試;PRE 為預(yù)加重使能信號(hào)。

圖1 TLK2711 原理框圖

2 高速串行數(shù)據(jù)傳輸接口設(shè)計(jì)

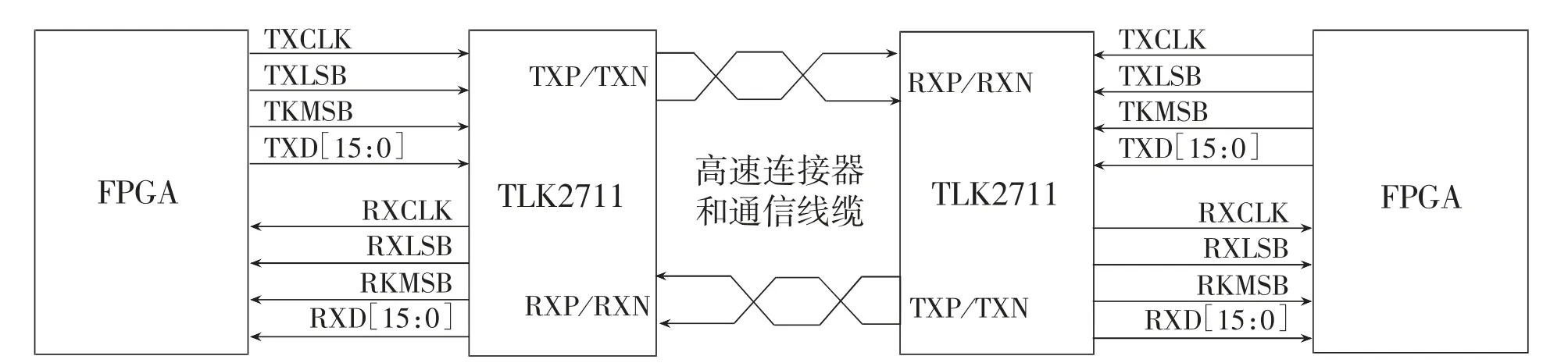

高速串行數(shù)據(jù)傳輸接口如圖2 所示,TLK2711與高速連接器構(gòu)成通信協(xié)議的物理層,實(shí)現(xiàn)收發(fā)數(shù)據(jù)的編解碼與串并轉(zhuǎn)換。FPGA 則實(shí)現(xiàn)數(shù)據(jù)鏈路層功能,完成通道的初始化、發(fā)送數(shù)據(jù)的幀封裝、接收數(shù)據(jù)的解封裝,同時(shí)為上層用戶提供簡(jiǎn)單的通信接口。

圖2 高速串行數(shù)據(jù)傳輸接口

3 全雙工通信協(xié)議設(shè)計(jì)

3.1 高速串行通信協(xié)議模型

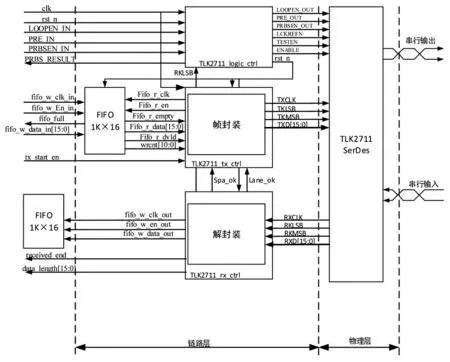

本文設(shè)計(jì)的是在FPGA 中實(shí)現(xiàn)的全雙工點(diǎn)對(duì)點(diǎn)鏈路層串行通信協(xié)議,不存在尋址交換和復(fù)雜的上層應(yīng)用,主要功能為鏈路初始化和同步、數(shù)據(jù)幀傳輸和鏈路管理。圖3 為高速串行通信協(xié)議的模型。模型包括TLK2711_logic_ctrl 模塊、TLK2711_tx_ctrl模塊、TLK2711_rx_ctrl 模塊和FIFO 數(shù)據(jù)緩存模塊。TLK2711_logic_ctrl 模塊主要為上層用戶提供環(huán)回測(cè)試、偽隨機(jī)測(cè)試及預(yù)加重功能接口,為了簡(jiǎn)化應(yīng)用,可將這些信號(hào)設(shè)置為芯片正常工作時(shí)的狀態(tài)。數(shù)據(jù)發(fā)送功能主要由TLK2711_tx_ctrl 模塊和發(fā)送端FIFO 實(shí)現(xiàn),上層應(yīng)用將發(fā)送數(shù)據(jù)寫入FIFO,當(dāng)寫完一幀數(shù)據(jù)后,使能tx_start_en 信號(hào),TLK2711_tx_ctrl模塊將FIFO 中的數(shù)據(jù)讀出組幀后發(fā)送出去,數(shù)據(jù)幀長(zhǎng)由wrcnt[10:0]信號(hào)給定。數(shù)據(jù)接收功能主要由TLK2711_rx_ctrl 模塊實(shí)現(xiàn),當(dāng)接收到有效數(shù)據(jù),TLK2711_rx_ctrl 模塊對(duì)數(shù)據(jù)進(jìn)行解幀,將解幀后的數(shù)據(jù)寫入接收端FIFO,供上層應(yīng)用讀取,每當(dāng)接收完一個(gè)完整的數(shù)據(jù)幀,TLK2711_rx_ctrl 模塊給出數(shù)據(jù)幀接收完畢信號(hào)(received_end 信號(hào))通知上層應(yīng)用,并給出接收數(shù)據(jù)幀長(zhǎng)。

圖3 高速串行通信協(xié)議模型

3.2 協(xié)議原語(yǔ)及狀態(tài)切換

3.2.1 協(xié)議原語(yǔ)

為了保證數(shù)據(jù)的正確傳輸,需要傳輸一些控制信息,這些定義的控制信息稱為協(xié)議原語(yǔ)。本協(xié)議采用8b/10b 中的K 字符和D 字符組合實(shí)現(xiàn)數(shù)據(jù)發(fā)送與接收的控制功能。SerDes 通過(guò)掃描搜尋cmoma 字符序列實(shí)現(xiàn)數(shù)據(jù)對(duì)齊功能。根據(jù)技術(shù)手冊(cè),TLK2711僅識(shí)別包含字符特征序列b0011111 或b1100000的控制字符作為識(shí)別數(shù)據(jù)邊界的comma 碼。在8b/10b中僅有K28.1、K28.5 和K28.7 包含這些字符特征序列,因此定義D5.6/K28.5 為同步字符,D12.1/K28.5 為同 步應(yīng) 答 字 符,D10.2/K28.5 為 空 閑 字 符,K28.2/K27.7 為幀頭標(biāo)識(shí),K29.7/K30.7 為幀尾標(biāo)識(shí)。

3.2.2 狀態(tài)切換

系統(tǒng)上電后需要對(duì)SerDes 進(jìn)行初始化和同步來(lái)建立一個(gè)有效鏈路,這樣SerDes 才能進(jìn)行正確的數(shù)據(jù)收發(fā)。鏈路同步由TLK2711_tx_ctrl 模塊和TLK2711_rx_ctrl 模塊共同完成,最終鏈路應(yīng)答標(biāo)志Spa_ok 和鏈路同步標(biāo)志Lane_ok 均為高電平,表示鏈路同步, 可以進(jìn)行數(shù)據(jù)的收發(fā)。TLK2711_tx_ctrl 模塊和TLK2711_rx_ctrl 模塊功能均由狀態(tài)機(jī)實(shí)現(xiàn),具體的狀態(tài)切換如下:

(1)鏈路初始化狀態(tài)

系統(tǒng)上電、復(fù)位或數(shù)據(jù)在傳輸過(guò)程中發(fā)生鏈路中斷都會(huì)使鏈路重新初始化。首先發(fā)送端會(huì)不斷發(fā)送同步字符D5.6/K28.5,當(dāng)接收端連續(xù)收到32 個(gè)同步字符時(shí),會(huì)置鏈路應(yīng)答標(biāo)志位Spa_OK為高。

(2)鏈路同步狀態(tài)

發(fā)送端再次發(fā)送80 個(gè)連續(xù)的同步應(yīng)答字符D12.1/K28.5 與176 個(gè) 連 續(xù) 的 同 步 字 符D5.6/K28.5,以保證接收端能夠有效的收到32 個(gè)同步字符D5.6/K28.5 或16 個(gè)同步應(yīng)答字符D12.1/K28.5。當(dāng) 接收端在應(yīng)答狀態(tài)下收到了連續(xù)的16個(gè)同步應(yīng)答字符D12.1/K28.5,則鏈路同步標(biāo)志Lane_OK 置高,鏈路進(jìn)入同步狀態(tài)。

(3)收發(fā)數(shù)據(jù)狀態(tài)

在同步狀態(tài)下,發(fā)送數(shù)據(jù)首先發(fā)送幀頭K28.2/K27.7,接下來(lái)發(fā)送數(shù)據(jù),發(fā)送數(shù)據(jù)結(jié)束后發(fā)送幀尾K29.7/K30.7,之后進(jìn)入空閑(IDEL)狀態(tài)。

(4)空閑狀態(tài)

在空閑狀態(tài)下,發(fā)送端不斷發(fā)送空閑字符D10.2/K28.5,以保持鏈路的建立。 當(dāng)需要發(fā)送數(shù)據(jù)時(shí),轉(zhuǎn)入收發(fā)數(shù)據(jù)狀態(tài)。

(5)鏈路檢測(cè)狀態(tài)

如果鏈路在一定時(shí)間內(nèi)沒(méi)有收到幀頭、幀尾、空閑字符、同步字符和同步應(yīng)答字符,說(shuō)明收發(fā)鏈路必有一條沒(méi)有建立,重新進(jìn)入鏈路初始化狀態(tài)。如果鏈路收到無(wú)效字符k0.0 和K31.7(即0x0000或0xFFFF),且RKLSB 與RKMSB 均為高,連續(xù)三次,鏈路即重新進(jìn)入初始化狀態(tài)。

3.3 全雙工串行通信協(xié)議實(shí)現(xiàn)

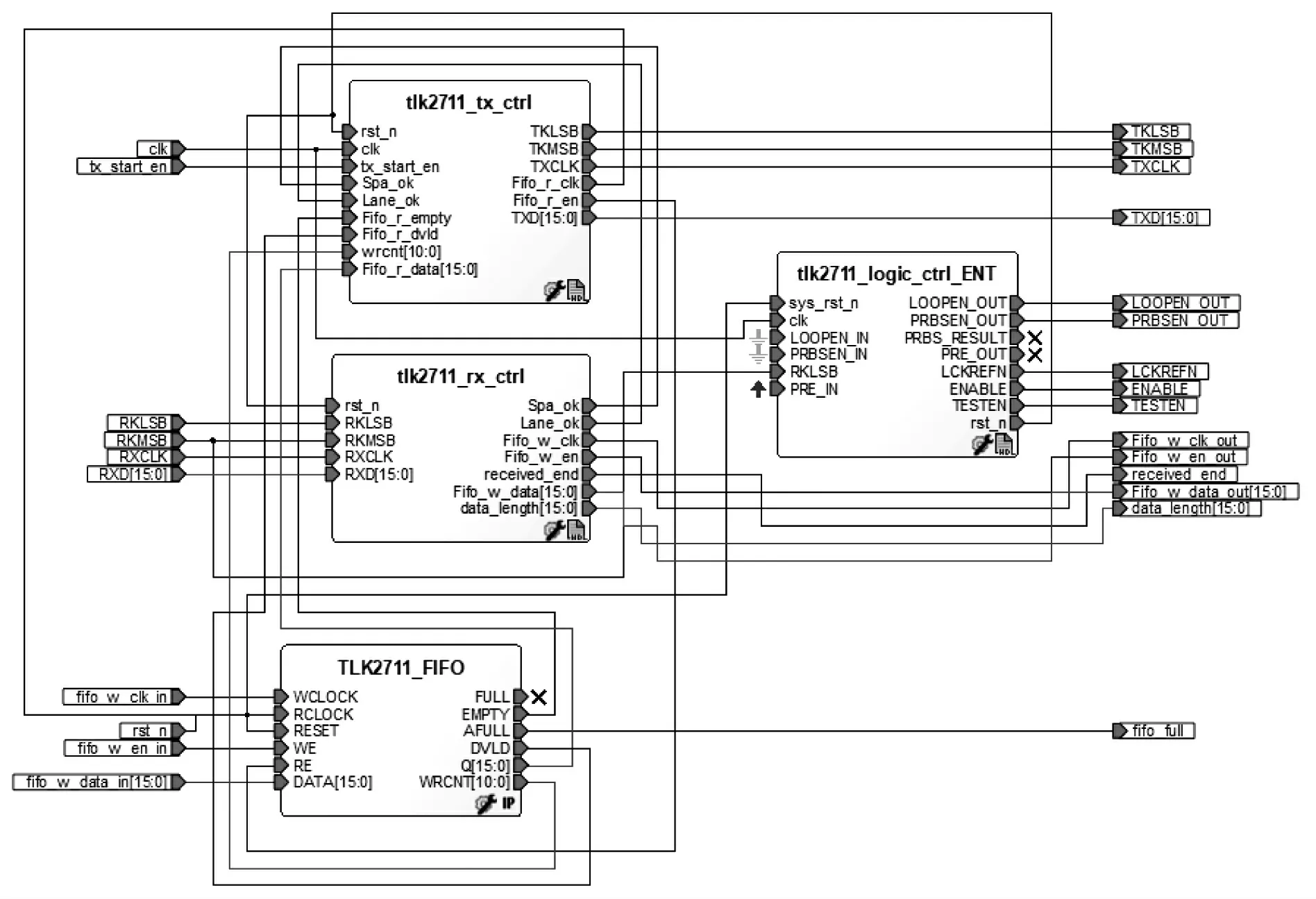

協(xié)議的FPGA 邏輯實(shí)現(xiàn)采用VHDL 硬件描述語(yǔ)言,由tlk2711_logic_ctrl_ENT 模塊、tlk2711_tx_ctrl模塊、tlk2711_rx_ctrl 模塊和內(nèi)置發(fā)送端TLK2711_FIFO組成,如圖4 所示。

圖4 全雙工串行通信協(xié)議

tlk2711_logic_ctrl_ENT 模塊主要對(duì)TLK2711的控制信號(hào)進(jìn)行了統(tǒng)一管理,包括LCKREFN 信號(hào)、TESTEN 信號(hào)、LOOPEN 信號(hào)、PRBSEN 信號(hào)和PRE 信號(hào)。該模塊接收系統(tǒng)復(fù)位信號(hào)(rst_n),并產(chǎn)生整個(gè)邏輯的復(fù)位信號(hào)(rst_n),同時(shí)將ENABLE置為低電平,延時(shí)100ms,使TLK2711 芯片復(fù)位。

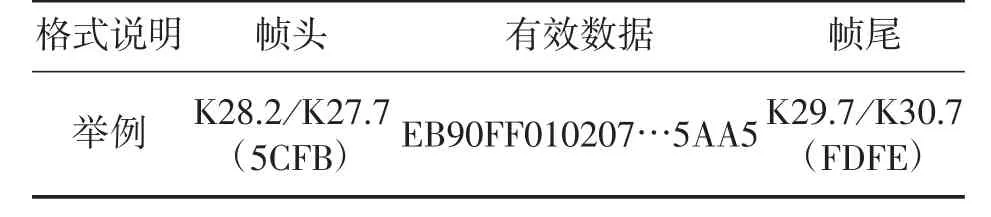

tlk2711_tx_ctrl 模塊主要實(shí)現(xiàn)數(shù)據(jù)的發(fā)送和對(duì)TLK2711 芯片發(fā)送端口的控制。當(dāng)接收到tx_start_en信號(hào)的上升沿,只要發(fā)送FIFO 不為空,就讀取FIFO 中的數(shù)據(jù)組幀后進(jìn)行發(fā)送,發(fā)送數(shù)據(jù)長(zhǎng)度由tx_start_en 信號(hào)的上升沿時(shí),wrcnt[10:0]的值決定。發(fā)送數(shù)據(jù)必須保證鏈路在初始化后同步的狀態(tài)下進(jìn)行,數(shù)據(jù)幀格式如表1 所示。可以看到幀頭和幀尾只占用整個(gè)數(shù)據(jù)幀中的4 個(gè)字節(jié),因此該協(xié)議屬于輕量級(jí)的串行數(shù)據(jù)傳輸協(xié)議。

表1 數(shù)據(jù)幀格式

tlk2711_rx_ctrl 模塊主要實(shí)現(xiàn)數(shù)據(jù)的接收和解幀,將解幀后的數(shù)據(jù)寫入外置接收FIFO。接收數(shù)據(jù)前需進(jìn)行鏈路的初始化和同步。同時(shí),接收端實(shí)現(xiàn)鏈路的檢測(cè)功能,當(dāng)判斷鏈路失效后,重新進(jìn)入復(fù)位模式,進(jìn)行鏈路的初始化和同步。Spa_ok和Lane_ok 為鏈路應(yīng)答標(biāo)志和鏈路同步標(biāo)志,傳輸至tlk2711_tx_ctrl 模塊,作為鏈路初始化和同步的標(biāo)志信號(hào)。

4 測(cè)試與驗(yàn)證

4.1 仿真測(cè)試

利用ModelSim 工具對(duì)高速串行通信協(xié)議進(jìn)行仿真測(cè)試,上電后發(fā)送端通過(guò)先后發(fā)送同步字符和同步應(yīng)答字符,接收端連續(xù)收到相應(yīng)字符后,最終置鏈路應(yīng)答標(biāo)志位Spa_OK 和鏈路同步標(biāo)志Lane_OK 為高電平,鏈路進(jìn)入同步狀態(tài)。

在鏈路同步狀態(tài)下,當(dāng)接收到tx_start_en 信號(hào),發(fā)送模塊將FIFO 中的數(shù)據(jù)讀出,并增加幀頭0x5CFB 和幀尾0xFCFE 后進(jìn)行發(fā)送。

當(dāng)接收到幀頭0x5CFB,將后續(xù)接收數(shù)據(jù)寫入FIFO,直到接收到幀尾0xFCFE,發(fā)出接收完畢信號(hào)received_end 信號(hào)。接收數(shù)據(jù)期間計(jì)數(shù)接收到的數(shù)據(jù)個(gè)數(shù),接收數(shù)據(jù)完畢將數(shù)據(jù)長(zhǎng)度通過(guò)data_length輸出。

4.2 實(shí)物測(cè)試

利用Microsemi 公司的SmartFusion2 SOC 平臺(tái)構(gòu)建多通道數(shù)據(jù)獲取系統(tǒng),采集到的數(shù)據(jù)通過(guò)由TLK2711 構(gòu)建的串行數(shù)據(jù)通道輸出。系統(tǒng)有兩路TLK2711 構(gòu)建的串行數(shù)據(jù)通道和一路千兆以太網(wǎng)接口,測(cè)試時(shí)將兩路串行數(shù)據(jù)通道的收發(fā)接口通過(guò)同軸線纜互聯(lián),即采集數(shù)據(jù)由一路串行數(shù)據(jù)通道發(fā)送,再由另一路串行數(shù)據(jù)通道接收,最后數(shù)據(jù)通過(guò)千兆以太網(wǎng)上傳至上位機(jī)。通過(guò)測(cè)試系統(tǒng)能夠?qū)崿F(xiàn)高速可靠數(shù)據(jù)全雙工傳輸,設(shè)置系統(tǒng)時(shí)鐘為80MHz~135MHz 的范圍,系統(tǒng)數(shù)據(jù)傳輸速率能夠達(dá)到1.6Gbps~2.7Gbps。在FPGA 中進(jìn)行了誤碼計(jì)數(shù)設(shè)計(jì),通過(guò)接收端進(jìn)行監(jiān)控收到的數(shù)據(jù)是否為所發(fā)送的數(shù)據(jù)。測(cè)試時(shí)發(fā)送時(shí)鐘為135MHz,串行數(shù)據(jù)率為2.7Gbps,發(fā)送數(shù)據(jù)量為1000Gb,將數(shù)據(jù)分為10000 個(gè)數(shù)據(jù)幀,發(fā)送完畢沒(méi)有出現(xiàn)誤碼。所以誤碼率BER=出錯(cuò)位數(shù)/總傳輸位數(shù)<1/1012=10-12。

5 結(jié)論

本文以SerDes 器件TLK2711 作為串行數(shù)據(jù)傳輸?shù)奈锢韺樱贔PGA 中設(shè)計(jì)串行數(shù)據(jù)通信協(xié)議的鏈路層,實(shí)現(xiàn)了一種輕量級(jí)的高速高可靠串行數(shù)據(jù)通信協(xié)議。進(jìn)行了功能仿真和實(shí)物測(cè)試,經(jīng)測(cè)試該通信協(xié)議在TLK2711 硬件的基礎(chǔ)上能夠?qū)崿F(xiàn)最高2.7Gbps 的數(shù)據(jù)傳輸速率,誤碼率小于10-12。本設(shè)計(jì)將為高速數(shù)據(jù)系統(tǒng)的設(shè)計(jì)和驗(yàn)證提供重要參考。