垂直電壓增益自動比例控制電路設計

余 甜,王志斌,景 寧

(1.中北大學 儀器與電子學院,山西太原 030051;2.中北大學微系統集成研究中心,山西太原 030051;3.中北大學信息與通信工程學院,山西太原 030051)

該文提出的垂直放大系統采用運算放大器、數模轉換器和高精度電阻設計了數字程控垂直增益放大電路[1],由FPGA接收上位機指令或者分析ADC采集數據的大小控制LTC2600 輸出不同的電壓來實現對垂直系統0.5、1、2、5、10、20、50倍放大倍數的調節[2],對應于上位機垂直系統調節范圍1~100 mV/div 中的七個檔位[3],相鄰的放大倍數調節按照1、2、5倍放大倍數互相變換[4],具有更全面的覆蓋范圍,以保證ADC位數盡量多的被使用,使得上位機恢復的波形更加精確[5]。

1 垂直增益放大電路工作原理

1.1 順序等效取樣原理

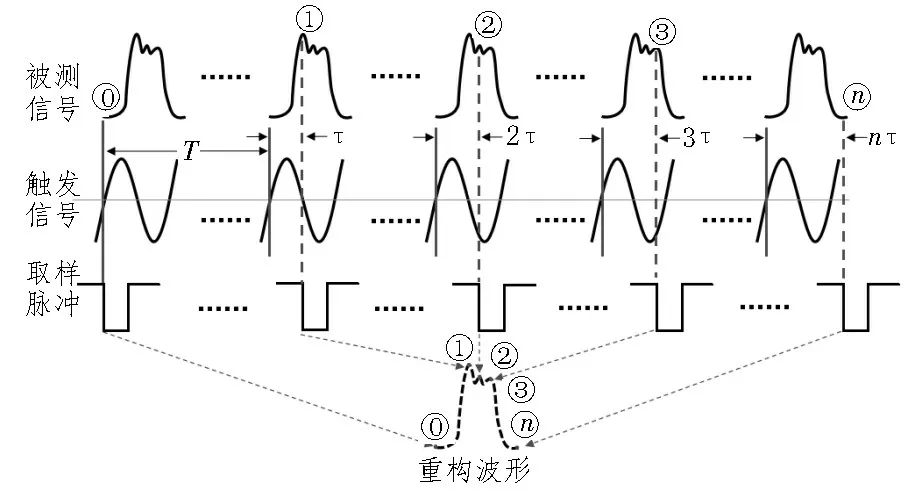

垂直增益放大電路作為取樣示波器波形重構的重要組成部分,其工作原理如圖1 所示。在被測信號與觸發信號同步的基礎上,精密時基模塊在觸發信號的驅動下每次觸發都會延時相同的時間產生取樣脈沖對被測信號進行取樣處理[6],同時產生同步采樣時鐘驅動垂直增益放大電路的模數轉換模塊進行取樣采集[7],每個取樣點分別取自被測信號波形的不同位置上,若干取樣點組成一個周期,就可以在上位機直接重構出被測信號,重構信號的頻率計算如式(1)所示:

圖1 順序等效取樣原理

1.2 同相比例運算電路

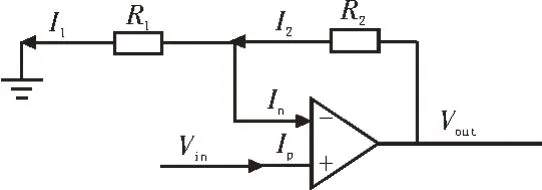

該設計的垂直增益放大電路基于同相比例運算電路的原理進行設計[8],電路如圖2 所示,輸入信號Vin加在運算放大器的同相輸入端,輸出信號Vout經過一個電阻R2加在運算放大器的反向輸入端,形成負反饋。由于理想的運算放大器的凈輸入電流為0,所以Ip=In=0,I1=I2。同時由于運算放大器的同相和反相輸入端虛短路,同相輸入端的電壓與反相輸入端的電壓相同,即可以計算出輸出電壓Vout與輸入電壓Vin的運算關系:

圖2 同相比例運算電路

由式(2)可知,同相比例運算電路的電壓增益放大倍數取決于R1+R2和R2之比,通過選擇不同大小的高精度的電阻搭建同相比例運算電路,就可以實現信號的放大、縮小或者保持不變[9]。

2 垂直增益放大電路設計

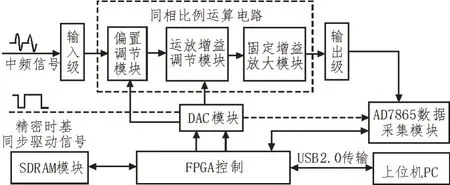

文中硬件系統包括五部分:數字控制垂直增益放大電路、數模轉換電路、數據采集電路、數據存儲電路和USB2.0 數據傳輸電路。硬件系統設計框圖如圖3 所示。

圖3 硬件系統設計

2.1 數字控制垂直增益放大電路

數字控制垂直增益放大電路設計由集成運放AD8512、AD8672、可變增益放大器AD603 和精度為0.1%的貼片電阻搭建而成。FPGA 采用Alter 公司的EP4CE22FC8N 芯片,用于通過控制數模轉換LTC2600 輸出電壓來改變垂直增益放大電路的放大倍數,同時控制數據的采集和存儲并使用USB2.0 將處理后的數據傳給上位機[10]。

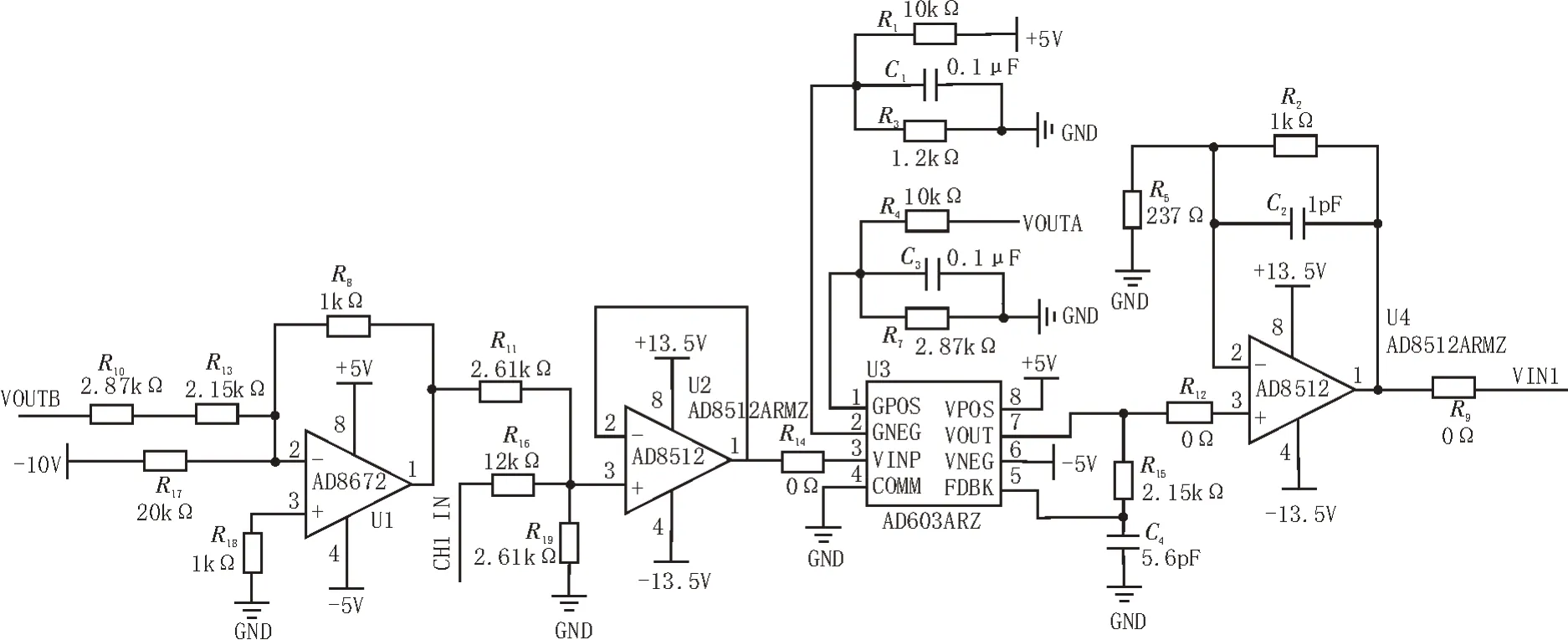

圖4 所示為數字控制垂直增益放大電路原理,U1、U2 與R8、R10、R11、R13、R14、R16、R17、R18構成輸入級同相比例運算電路,取樣器輸出中頻信號為CH1_IN,VOUTB 與數模轉換芯片LTC2600 輸出相連,由FPGA 控制LTC2600 對中頻信號的偏置進行調節,并將輸入信號的幅度衰減10 倍以滿足AD603 的輸入范圍[11]。U3 與R1、R3、R4、R7、R15、C1、C3、C4構成第二級同相運放增益調節電路,VOUTA 與數模轉換芯片LTC2600 輸出相連,通過改變VOUTA 的電壓來改變GPOS 和GNEG 的引腳電壓差,即可改變可變增益放大器AD603 的增益。輸出級由U4 與R2、R5、R9、R12、C2構成同相固定增益放大電路,負責將AD603輸出的信號放大5 倍,并輸出給AD7367 數據采集模塊[12]。

圖4 數字控制垂直增益放大電路

可變增益放大器AD603 的增益為0~40 dB,通過FPGA 控制LTC2600 調節AD603 的增益,鑒于該設計垂直增益放大電路采用125 比例放大,故采用其中的七種增益放大倍數。前級中頻電路取樣器每20 μs 取樣一次,取樣后的信號經高阻積分電路、加法器和三級濾波電路的固定增益放大后輸出幅值范圍為-10~10 V,頻率為50 kHz 的中頻信號輸入垂直增益放大電路[13],該設計電路增益帶寬為8 MHz,輸入幅值范圍為-12~12 V,滿足應用要求。

2.2 數模轉換電路模塊

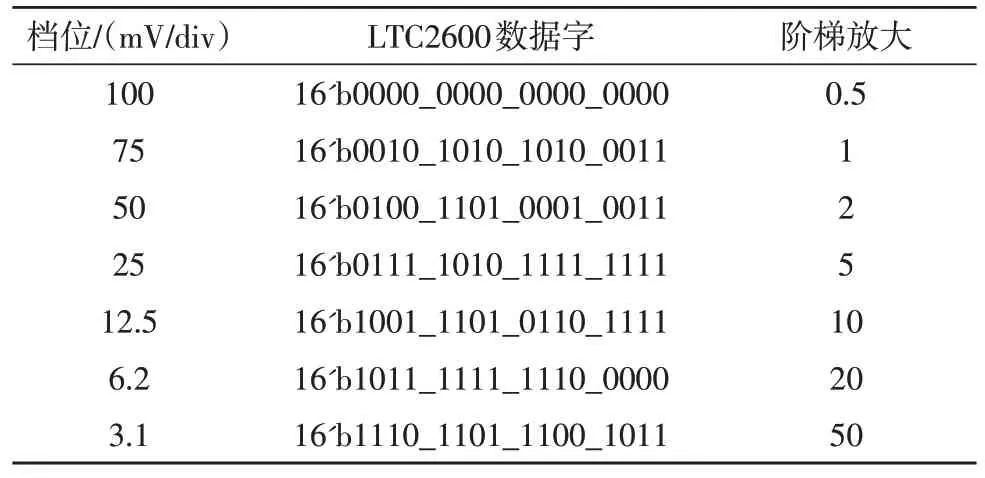

該設計中數模轉換電路使用LTC2600 調節垂直增益放大電路的增益倍數,LTC2600 的基準電壓使用ADR02 輸出+5 V 參考電壓。上位機通過USB 發送16 位十六進制數作為控制指令,由FPGA 讀取USB 中接收到的指令并識別上位機控制的通道以及所控制的通道的放大倍數從而控制LTC2600 所對應通道的電壓,以實現雙通道放大倍數和偏置的控制。該文垂直系統幅值刻度調節范圍為1~100 mV/div,共有七個檔位,上位機垂直系統幅值刻度初始為100 mV/div,刻度值越大,放大倍數越小,具體對應關系如表1所示。垂直系統偏置調節范圍為-500~500 mV,當LTC2600 的B 或D 通道輸出電壓為0 V 時,偏置為-500 mV,當B或D通道輸出電壓為2.5 V時,偏置為0 mV,當B或D通道輸出電壓為5 V時,偏置為+500 mV。

表1 DAC數據字與放大倍數對應關系

2.3 AD7367數據采集模塊

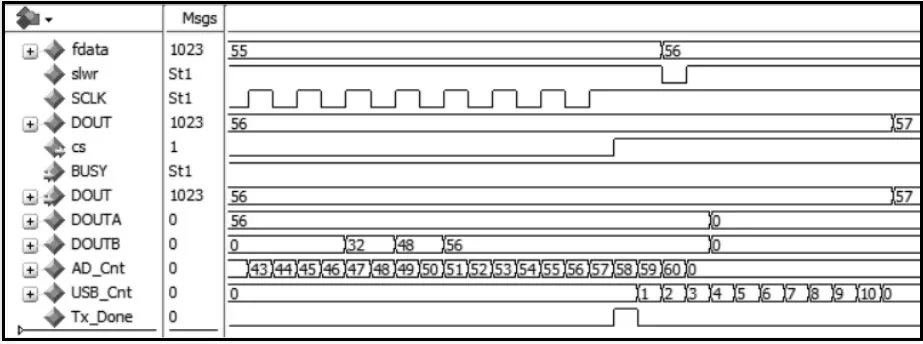

由FPGA 驅動AD7367 數據采集模塊對垂直增益放大電路調理后的中頻信號進行同步采集,精密時基模塊每隔20 μs 產生取樣脈沖對被測信號進行取樣[14],同時產生50 kHz 同步采樣脈沖驅動AD7367的CNVST 信號開啟模數轉換,采集取樣后的中頻信號[15]。當BUSY 信號拉低產生下降沿,表示模數轉換完成,FPGA 檢測到BUSY 信號下降沿后拉低CS 使能信號,此時DOUT 數據線輸出第14 位數字信號,SCLK 信號下降沿更新DOUT 數據線上的數據,FPGA 產生14 個SCLK 信號并在SCLK 信號上升沿時讀取DOUT 數據線上的數字信號,直到讀取完最后一位數字信號后拉高CS 信號,DOUT 數據線回到高阻態并等待下一次數據轉換。

依據AD7367 的工作時序圖對其進行仿真,仿真結果如圖5 所示。當檢測到BUSY 信號的下降沿后,AD_cnt 開始計數,線性序列機根據AD_cnt 的數值拉低CS 使能信號,并依次產生SCLK 信號讀取AD7367轉換完成的數字信號。最后,Tx_Done 拉高一個時鐘周期,代表傳輸結束,CS 使能信號拉高。FPGA 將模數轉換完成的數字信號分組存到SDRAM 中并通過USB2.0 發給上位機進行波形重構和分析。

圖5 AD7367工作仿真圖

3 實驗驗證與數據分析

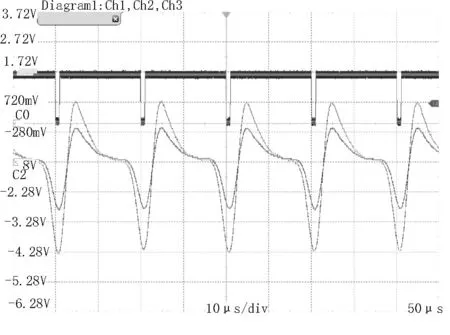

3.1 上位機控制垂直增益放大電路階梯放大

上位機啟動USB Control Center(USB 控制中心),使用Control Center 將CY7C68013A 芯片配置為從設備FIFO 模式之后發送控制垂直增益放大電路階梯放大的邏輯電平指令,指令用8 位十六進制數表示,邏輯指令更新到FPGA 后,由FPGA 識別指令然后配置LTC2600 從而實現對垂直增益放大電路進行控制,實現階梯放大倍數。對其進行板級驗證,將輸入80 mV 的中頻取樣信號放大50 倍,信號經垂直增益放大電路輸出幅值為4 V,如圖6 所示。其中,被測信號經取樣、濾波、放大后其幅值信息存在于正弦包絡狀信號的峰值位置[16],3 通道脈沖信號為同步取樣信號,頻率為50 kHz,脈沖信號的下降沿驅動AD7367 對正弦包絡狀信號的峰值位置進行采樣,上位機根據采集到的數據、時基刻度和采樣點數就可以重構出被測信號的頻率和幅值。

圖6 80 mV中頻取樣信號放大50倍

3.2 上位機接收采集數據

為了驗證垂直電壓增益自動比例控制電路性能,將設計的硬件電路和精密時基電路、脈沖壓縮模塊、中頻濾波放大模塊進行聯調測試,實驗采用的射頻源為KEYSIGHT 的E8257D,示波器為ROHDE&SCHWARZ 的RTO2044 等儀器。

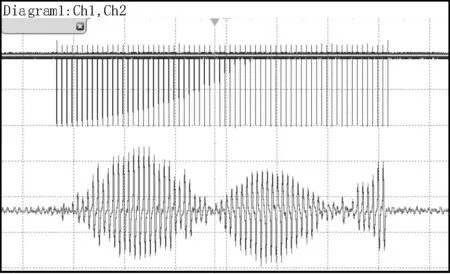

將整套硬件系統搭建好后,上位機設置精密時基模塊步進延時為10 ps,取樣點數為64,總延時范圍為640 ps,每20 μs 產生一次取樣脈沖,總取樣周期為1 280 μs。被測信號輸入2 GHz、200 mV 正弦信號,示波器測試波形如圖7 所示,示波器時基刻度為每格200 μs,其中正弦包絡狀信號為垂直增益放大后的取樣中頻信號,正弦包絡狀信號的峰值位置包含著被測信號取樣時的幅值信息,64 個正弦包絡狀信號依次組成2 GHz 被測信號。脈沖信號為同步取樣信號,頻率為50 kHz,脈沖信號的下降沿對應著正弦包絡狀信號的峰值位置并對其進行采樣,并由上位機根據每次產生取樣脈沖后的延時時間和采樣點數將被測信號重構出來。

圖7 被測信號為2 GHz時重構波形

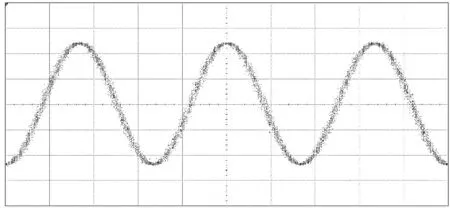

同理,上位機設置精密時基模塊取樣點數為8 192。被測信號輸入5 GHz、200 mV 正弦信號,使用14 bit 兩通道高精度同步采樣ADC 芯片AD7367 對垂直增益放大電路的輸出的正弦包絡狀信號進行采集,AD7367輸入范圍為-10~10 V,采集頻率為50 kHz,FPGA 讀取AD7367 轉化完成的數字信號并分組存入到相應通道的FIFO 內,當FIFO 內存儲的數據大于SDRAM 的突發長度時,FPGA 讀取FIFO 內的數據以突發寫的方式將數據存入SDRAM 中,然后進行相應的處理之后通過USB2.0 將數據傳輸到上位機。上位機對于上行數據進行轉碼處理和波形重構,其恢復波形如圖8 所示。

圖8 被測信號為5 GHz時重構波形

4 結論

該文針對垂直電壓增益放大電路,使用FPGA控制垂直增益放大倍數、數據的采集與存儲和USB2.0 與上位機進行雙向通信,通過上述實驗驗證和數據分析得知,垂直電壓增益放大電路的放大倍數誤差小于2%,且放大倍數采用1、2、5 比例放大,具有更全面的覆蓋范圍,以保證ADC 位數盡量多的被使用,使得上位機恢復的波形更加準確。與此同時,FPGA 通過分析上位機指令靈活控制雙通道數據存儲長度,每個通道的采樣點數為16~65 536 個,靈活的采樣率能夠根據不同情況捕獲不同長度的波形,上位機能夠分析信號中微弱的抖動或者毛刺信號,使得波形測試結果更加精確。