LDO穩(wěn)定性分析及環(huán)路補(bǔ)償

馬文超

(中國(guó)電子科技集團(tuán)公司第五十八研究所,江蘇無(wú)錫 214072)

線性穩(wěn)壓器(LDO)早期一般采用雙極型晶體管工藝,功率管為負(fù)極正極負(fù)極(NPN)型、正極負(fù)極正極(PNP)型或者NPN 達(dá)林頓管,器件的靜態(tài)功耗和輸入輸出壓差比較大,轉(zhuǎn)化效率低,但是該類(lèi)器件的響應(yīng)速度快,可以輸出的負(fù)載電流高;隨著MOS 工藝的出現(xiàn),以N 型金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)管(NMOSFET)或者P 型金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)管(PMOSFET)為導(dǎo)通功率管的LDO 逐漸成為主流,NMOSFET作為導(dǎo)通器件時(shí),LDO 的漏失電壓至少大于NMOS 閾值電壓與驅(qū)動(dòng)級(jí)飽和壓降之和,驅(qū)動(dòng)電路設(shè)計(jì)較為復(fù)雜或者采用雙電源供電(偏置電源和功率電源PVIN),該類(lèi)LDO 環(huán)路穩(wěn)定性較好,對(duì)輸出電容等效串聯(lián)電阻(ESR)依賴程度不高,相同負(fù)載電流時(shí),相對(duì)PMOSFET 型LDO,功率管面積小,因此,器件可以做成小封裝。PMOSFET 構(gòu)成的LDO 漏失電壓比較小,靜態(tài)電流和電源噪聲很低,驅(qū)動(dòng)電路簡(jiǎn)單,超低壓差線性穩(wěn)壓器多采用此類(lèi)器件,該電路的缺點(diǎn)是環(huán)路穩(wěn)定性補(bǔ)償相對(duì)復(fù)雜,但MOS 半導(dǎo)體工藝和控制理論技術(shù)的成熟使得該問(wèn)題迎刃而解,因此,由PMOS 構(gòu)成的LDO 成為市面上的主流產(chǎn)品,對(duì)該類(lèi)器件的研究也比較多[1-3]。

針對(duì)不同的應(yīng)用場(chǎng)景,對(duì)LDO 的特性有不同的要求,一般可以分為以下幾類(lèi):

高功率LDO,該類(lèi)LDO 主要應(yīng)用于控制芯片、內(nèi)存、主板、顯卡或者汽車(chē)電子,最大負(fù)載電流可達(dá)幾安培,如TPS75901 等,封裝采用TO-220 或者TO-263,體積較大,在使用時(shí)一般需要采用額外的散熱片才能正常使用,應(yīng)用成本較高;

高電源電壓抑制比(PSRR)型LDO,在實(shí)際應(yīng)用時(shí),LDO的輸入電壓一般來(lái)源于前端的DC/DC 輸出,該輸出電壓分布在整個(gè)頻譜范圍內(nèi),通過(guò)LDO 可以耦合到負(fù)載對(duì)象中,可能造成對(duì)工作電壓比較敏感的模擬器件,如模擬數(shù)字轉(zhuǎn)換器(ADC)、射頻(RF)、壓控振蕩器(VCO)、鎖相環(huán)(PLL)以及混頻器等不能正常工作,因此,高PSRR 特性的LDO 可以“過(guò)濾”前級(jí)DC/DC 輸出的紋波干擾,給負(fù)載提供干凈的電源[4],ADP7158 屬于這類(lèi)器件;

快速瞬態(tài)響應(yīng)型LDO,有些負(fù)載在整個(gè)工作過(guò)程中,會(huì)在睡眠模式和正常工作模式之間不停地切換,因此負(fù)載電流在輕載和重載之間進(jìn)行切換,另外,LDO 的輸入電壓也經(jīng)常在典型工作電壓附近擺動(dòng),為了使得LDO 的輸出電壓能夠在上述狀態(tài)下仍然保持穩(wěn)定,要求LDO 具有快速的瞬態(tài)響應(yīng)能力[5],由于受到帶寬和壓擺率的限制(調(diào)整管柵極電容、寄生電容等因素的影響),環(huán)路調(diào)整需要一定的時(shí)間,另外,在不同的輸入電壓或者負(fù)載電流條件下,LDO 內(nèi)部的靜態(tài)工作點(diǎn)也會(huì)發(fā)生變化,因此,LDO 的輸出電壓會(huì)產(chǎn)生過(guò)沖或者下沖現(xiàn)象,甚至?xí)霈F(xiàn)環(huán)路震蕩[6],TPS755XX 屬于這類(lèi)器件;

低噪聲型LDO,對(duì)于一些音頻或者RF 芯片,要求供電電源的噪聲比較小,LDO 的噪聲主要來(lái)源于帶隙基準(zhǔn)、誤差放大器、電阻分壓網(wǎng)絡(luò)以及功率管產(chǎn)生的噪聲,其中基準(zhǔn)占大部分(75%以上),功率管本身尺寸較大,溝道電阻比較小,產(chǎn)生的噪聲比較小,同時(shí)誤差放大器的增益很大,所以功率管產(chǎn)生的噪聲經(jīng)過(guò)放大器衰減后可以忽略,一般將帶隙基準(zhǔn)、誤差放大器和電阻分壓網(wǎng)絡(luò)內(nèi)部電路模塊產(chǎn)生的噪聲等效至誤差放大器的輸入端,一般只關(guān)注10 Hz~100 kHz 范圍內(nèi)的噪聲頻譜分布,何颯和孫蕊在設(shè)計(jì)上通過(guò)基準(zhǔn)進(jìn)行輸出濾波的方法降低LDO 輸出噪聲[7-8];

低靜態(tài)功耗型LDO,在電池供電場(chǎng)景中,比如穿戴電子設(shè)備、煙霧或者熱量探測(cè)裝置、血液葡萄糖監(jiān)測(cè)儀等,為了增加電池的使用時(shí)間或者產(chǎn)品的待機(jī)時(shí)間,需要電源具有較低的靜態(tài)功耗,即比較低的靜態(tài)電流和關(guān)斷電流,比如TI 公司的TPS7A02,該款LDO 的靜態(tài)電流為25 nA,關(guān)斷電流為3 nA,是業(yè)界的典型代表產(chǎn)品[9];

無(wú)片外電容型LDO,多數(shù)LDO 通過(guò)輸出電容的ESR特性進(jìn)行環(huán)路補(bǔ)償,輸出電容的ESR需要滿足一定的范圍才能使LDO 輸出穩(wěn)定,給實(shí)際選用帶來(lái)一定的困難,在某些使用場(chǎng)景下,比如片上系統(tǒng)(SoC)芯片,對(duì)體積要求較為嚴(yán)格,LDO的輸出電容一方面增加了印制電路板(PCB)尺寸,輸出電容的焊盤(pán)走線也會(huì)帶來(lái)寄生電感,另外一方面使得成本提升,因此無(wú)片外電容的LDO 或者只需要小容量陶瓷電容的LDO成為近些年研究的熱點(diǎn),段杰斌和唐宇分析了該類(lèi)LDO 的環(huán)路特性,并給出了環(huán)路穩(wěn)定性補(bǔ)償策略[10-11],TLV713 是該類(lèi)電容的一個(gè)典型代表,該產(chǎn)品可在無(wú)輸出電容情況下穩(wěn)定運(yùn)行,同時(shí)具有折返電流限制功能,封裝尺寸只有1 mm×1 mm,非常適合便攜式設(shè)備或者集成在SoC 中;

低輸入電壓型LDO,在醫(yī)療電子領(lǐng)域,需要低輸入電壓型LDO,該類(lèi)LDO 主要從工藝上進(jìn)行設(shè)計(jì)選型,輸入端采用低壓功率管,如采用1.8 V 工藝設(shè)計(jì)的ADP1763,去掉不必要的Fuse 修調(diào)部分,整個(gè)芯片面積小于1.0 mm×1.0 mm,體積較小,最大輸出電流為3 A,輸入電壓1.1~1.98 V,典型輸入電壓1.2、1.5 和1.8 V;

寬輸入電壓型LDO,工業(yè)應(yīng)用環(huán)境中,大量用到功率放大器或者運(yùn)算放大器電路,該類(lèi)器件的工作電壓為±15、±12 V 等,工作電流一般為mA 級(jí),如果采用DC/DC 架構(gòu),需要電感電容等濾波元件,電源占用的PCB 面積較大,往往采用高壓LDO 電路(包括正高壓和負(fù)高壓),如TPS7A49 輸入電壓3.0~36 V(最大輸出電流150 mA),TPS7A30 輸入電壓-3.0~-35 V(最大輸出電流200 mA),使用此類(lèi)器件可以搭配使用,比如輸入電壓±24 V。

上述LDO 都在某些特性的領(lǐng)域具有一定的市場(chǎng)占有率,除了上述特點(diǎn)外,根據(jù)使用功能要求不同,LDO 還具有電流折返、電流限、熱保護(hù)、輸出電壓狀態(tài)指示、輸出電流監(jiān)測(cè)、遠(yuǎn)端補(bǔ)償、內(nèi)部結(jié)溫監(jiān)測(cè)、并聯(lián)均流、軟啟動(dòng)、欠壓保護(hù)、負(fù)載電流快速泄放等多種功能,可以根據(jù)實(shí)際需要選擇。

1 LDO 基本架構(gòu)和工作原理

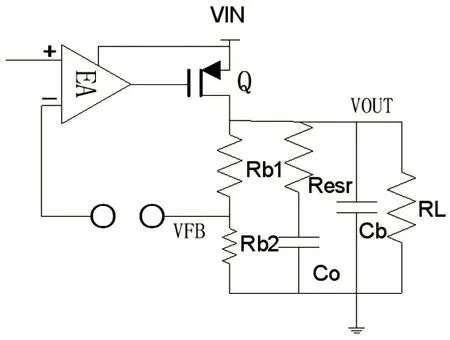

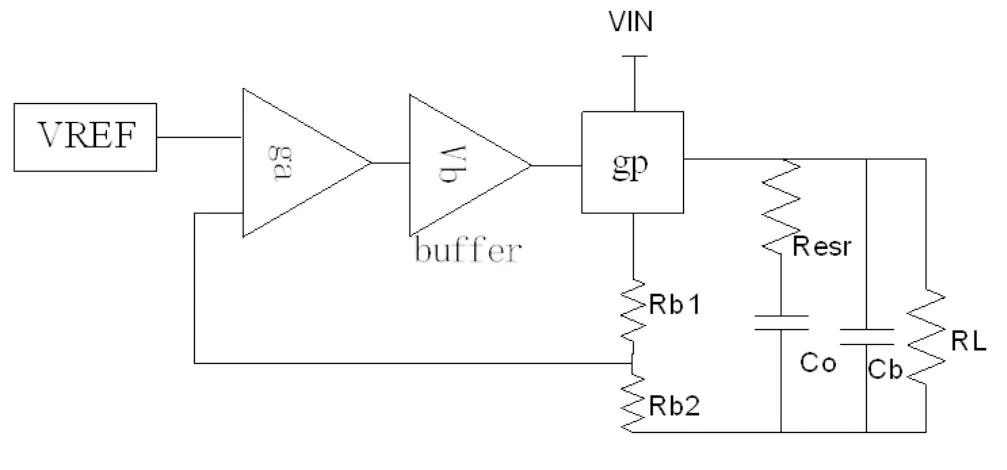

文獻(xiàn)[12]給出以PMOS 為功率管的LDO 簡(jiǎn)易環(huán)路結(jié)構(gòu),如圖1 所示。

圖1 LDO環(huán)路結(jié)構(gòu)圖

從圖1 可以看出,一個(gè)LDO 主要包含了功率管、電壓基準(zhǔn)、誤差放大器和反饋網(wǎng)絡(luò),輸出電壓經(jīng)過(guò)兩個(gè)分壓電阻進(jìn)行采樣,采樣電壓與基準(zhǔn)電壓進(jìn)行相減,誤差信號(hào)經(jīng)過(guò)放大后驅(qū)動(dòng)功率管的導(dǎo)通得到穩(wěn)定的輸出電壓。輸出濾波電容可以等效為一個(gè)等效串聯(lián)電阻串聯(lián)理想電容,當(dāng)負(fù)載電流突然增加時(shí),首先由輸出電容提供瞬時(shí)電流給負(fù)載供電,維持輸出電壓穩(wěn)定,調(diào)整過(guò)程中輸出電壓略微下降后再恢復(fù)設(shè)定值;同理,當(dāng)負(fù)載電流突然減小時(shí),功率管額外的輸出電流給電容充電,使得輸出電壓略微上升,之后通過(guò)負(fù)反饋調(diào)節(jié),輸出恢復(fù)設(shè)定值。

2 LDO 關(guān)鍵指標(biāo)和性能

LDO 的指標(biāo)反映了其性能優(yōu)劣,部分指標(biāo)之間存在一定的關(guān)聯(lián)性,因此每個(gè)器件不可能做到所有指標(biāo)都盡善盡美,芯片設(shè)計(jì)師在設(shè)計(jì)時(shí)進(jìn)行取舍,客戶在選用時(shí)根據(jù)系統(tǒng)要求進(jìn)行選型。

2.1 Dropout 電壓

壓差是在一定負(fù)載電流條件下,為了保證輸出電壓穩(wěn)定的最小輸入輸出電壓差,該數(shù)值隨著負(fù)載電流增加而增加,負(fù)載電流最大時(shí),該值最大,隨著溫度升高而線性增加,實(shí)際使用時(shí),為了保證器件在全溫度和全負(fù)載條件下工作,至少保證輸入大于輸出與壓差最大值之和。

2.2 靜態(tài)電流、關(guān)斷電流和地電流

靜態(tài)電流、關(guān)斷電流和地電流反映器件的功耗大小,其值越小,器件功耗越小。靜態(tài)電流是空載且使能有效輸出時(shí)的電源電流,關(guān)斷電流是使能無(wú)效時(shí)的電源電流,地電流是整個(gè)電路從電源吸取的電流,使用晶體管為功率器件的設(shè)計(jì)該數(shù)值隨負(fù)載增加而增加,使用基于MOSFET 的LDO 地電流隨負(fù)載增加時(shí)變化不大。

2.3 線性調(diào)整率和負(fù)載調(diào)整率

線性調(diào)整率[12]反映輸出電壓由于輸入電壓變化而引起的變化量,其表達(dá)式如式(1)所示,環(huán)路增益越大,該數(shù)值越小,表示輸出電壓受輸入變化影響越小。

負(fù)載調(diào)整率[13]反映輸出電壓由于負(fù)載變化而引起的變化量,計(jì)算公式為式(2)或(3):

負(fù)載調(diào)整率即為負(fù)載調(diào)整電阻,此電阻越小,輸出電壓的變化量越小,LDO 的輸出受負(fù)載變化影響越小。該電阻包含閉環(huán)輸出電阻Rout和輸出端PCB 走線電阻RPCB,后者可以通過(guò)大面積敷銅的方法盡可能減小該值,前者可以通過(guò)提高環(huán)路增益降低該值,但是提高增益可能會(huì)引起環(huán)路不穩(wěn)定,環(huán)路補(bǔ)償難度增加,要綜合考慮。

2.4 輸出電壓精度

輸出電壓精度[13]由線性調(diào)整率、負(fù)載調(diào)整率、帶隙基準(zhǔn)電壓漂移、誤差放大器電壓漂移、輸出分壓電阻精度和工作溫度共同決定,一般精度要求在1%~3%。

2.5 電源紋波抑制比

電源紋波抑制比PSRR[1,12]指輸入電壓微小波動(dòng)時(shí),電路對(duì)輸出電壓的調(diào)節(jié)能力。PSRR反映了LDO 對(duì)輸入電壓引入的波動(dòng)抑制能力,通常在一定的輸入電壓、輸出電壓、負(fù)載電流和輸入輸出電容條件下,該數(shù)值隨頻率變化,主要關(guān)注100 Hz、1 kHz 和100 kHz 三個(gè)頻率點(diǎn)的數(shù)值,該數(shù)值越大,越可以濾除輸入電壓波動(dòng)對(duì)輸出的干擾。提高直流增益可提高PSRR,輸出電容增加也會(huì)改善高頻段的PSRR,但輸出電容的增加會(huì)導(dǎo)致環(huán)路穩(wěn)定性問(wèn)題,PCB面積增加,使得成本提高。

2.6 最大輸出電流

產(chǎn)品手冊(cè)中標(biāo)注的最大輸出電流一般是室溫狀態(tài)及典型壓差情況下的理想值,LDO 輸出電流越大,自身功耗也越大,芯片內(nèi)部結(jié)溫就越高,具體選用時(shí)需要考慮溫度情況,結(jié)合器件的最大結(jié)溫、熱阻和最大功耗進(jìn)行估算,同時(shí)還要留有裕量。

2.7 最小負(fù)載電流

針對(duì)晶體管工藝的LDO 需滿足最小負(fù)載電流電路才能穩(wěn)定工作,實(shí)際使用時(shí)可以在輸出和地連接一個(gè)kΩ 阻值的電阻。

2.8 輸出噪聲

LDO 的輸出噪聲[7]實(shí)際應(yīng)用時(shí)與輸出電壓、負(fù)載電流大小等密切相關(guān),需要特殊設(shè)計(jì)才能做到比較低的噪聲。

2.9 瞬態(tài)響應(yīng)特性

瞬態(tài)響應(yīng)[14]包括負(fù)載瞬態(tài)響應(yīng)和線性瞬態(tài)響應(yīng),前者是當(dāng)負(fù)載在輕載和重載之間以一定的跳變率進(jìn)行來(lái)回跳變時(shí),輸出電壓的波動(dòng)情況,具有快速瞬態(tài)響應(yīng)特性的LDO 可以適用于工作狀態(tài)變化劇烈的負(fù)載對(duì)象,提高環(huán)路帶寬可以減小恢復(fù)時(shí)間,設(shè)計(jì)上提高功率管柵極壓擺率也可以改善LDO 輸出負(fù)載瞬態(tài)響應(yīng);后者是輸入電壓變化時(shí),輸出電壓的變化過(guò)程,提高環(huán)路增益可以獲得較好的線性瞬態(tài)響應(yīng)。

2.10 軟啟動(dòng)和啟動(dòng)時(shí)間

電路的軟啟動(dòng)功能是為了防止輸出電壓過(guò)沖,部分LDO預(yù)留軟啟動(dòng)引腳(比如SS),實(shí)際使用時(shí),在該引腳和地之間連接一個(gè)陶瓷電容作為軟啟動(dòng)電容,可以調(diào)節(jié)輸出電壓爬升的快慢;啟動(dòng)時(shí)間是指輸出相對(duì)于供電電壓或者使能信號(hào)的延遲時(shí)間。

2.11 保護(hù)功能

電路通常具有各種保護(hù)機(jī)制,在上電或者輸出異常時(shí)保護(hù)電源芯片或者負(fù)載,常見(jiàn)的主要有輸入欠壓保護(hù)、熱關(guān)斷、輸出短路保護(hù)、輸出電流限制和電流折返、過(guò)壓關(guān)斷、反接保護(hù)和反向泄漏保護(hù)。

2.12 輸入電壓

單板或單機(jī)設(shè)計(jì)時(shí),首先考慮需要的電源軌,比如5、12 V 電源線,通過(guò)DC/DC 或者LDO 進(jìn)行變換,在確定LDO 的輸入電壓時(shí),要滿足兩個(gè)條件:大于芯片輸入電壓的最小值且大于實(shí)際輸出電壓與全溫范圍下壓差最大值之和。

2.13 輸出電壓及其調(diào)節(jié)方式

輸出電壓一般可通過(guò)兩個(gè)分壓電阻進(jìn)行設(shè)置,電阻精度取1%以上,首先選定Rb2,再計(jì)算出Rb1,查找電阻標(biāo)稱值表,把實(shí)際電阻值代入輸出電壓計(jì)算公式得出輸出電壓值,根據(jù)與理論輸出電壓的相對(duì)百分比,可以在標(biāo)稱值最近的兩檔選擇合適的電阻值[9]。

2.14 負(fù)載電流監(jiān)測(cè)

部分LDO 設(shè)置了輸出負(fù)載電流監(jiān)控引腳,通過(guò)在該引腳對(duì)地或者與輸入電源端連接一個(gè)電阻,該引腳的電壓值與負(fù)載電流呈線性關(guān)系,間接反映出負(fù)載電流大小,可以通過(guò)監(jiān)測(cè)該引腳電壓值進(jìn)行電源的健康管理。

2.15 遠(yuǎn)端補(bǔ)償

由于LDO 的輸出端與負(fù)載之間存在PCB 走線電阻,在重負(fù)載條件下,在PCB 走線上的電壓降不可忽略,負(fù)載端的實(shí)際電壓值低于LDO 的輸出電壓,為了彌補(bǔ)線損,部分LDO 設(shè)置了遠(yuǎn)端補(bǔ)償引腳,將該端口走線連接負(fù)載供電端,類(lèi)似開(kāi)爾文接法,可提高負(fù)載端供電電壓的精準(zhǔn)度。

2.16 內(nèi)部結(jié)溫輸出指示

為了監(jiān)測(cè)芯片內(nèi)部的結(jié)溫,利用二極管的基級(jí)射級(jí)電壓(VBE)與溫度的線性關(guān)系,在芯片引出端給出結(jié)溫指示引腳,該引腳電壓與內(nèi)部結(jié)溫呈正比,對(duì)調(diào)試階段、監(jiān)控或者計(jì)算封裝熱阻都具有實(shí)用意義。

2.17 并聯(lián)均流

為了滿足大負(fù)載電流要求,或者為了使器件熱量進(jìn)行分散,部分LDO 可以進(jìn)行雙路并聯(lián),使用并聯(lián)均流功能時(shí),需要按照產(chǎn)品手冊(cè)將兩個(gè)器件的相關(guān)引腳短接,在PCB 布局時(shí)盡可能使輸出端的阻抗一致,以免引起電流不均勻。

2.18 使能和輸出狀態(tài)指示

大部分LDO 都有輸出使能引腳EN(或者低電平有效),通過(guò)外部CMOS 邏輯電平可以控制該端口的高低狀態(tài),以開(kāi)啟或者關(guān)斷LDO;部分LDO 設(shè)置了漏極開(kāi)路的Power Good 端口,使用時(shí)通過(guò)上拉電阻接到電源輸入或者輸出端,用來(lái)指示輸出電壓的狀態(tài)。

2.19 封裝和熱阻

封裝決定了熱阻,采用不同的封裝形式、封裝材料,器件的熱阻也不同,散熱越好的封裝,熱阻越小,器件結(jié)溫低,可靠性提高。熱阻通常有θJA、θJCbottom和θJCtop三種形式,器件的工作結(jié)溫范圍由制造工藝決定,最大允許功耗由最大環(huán)境溫度、器件最大持續(xù)結(jié)溫和結(jié)到空氣之間的熱阻值決定,超過(guò)最大功耗會(huì)使得器件超過(guò)最高結(jié)溫,影響器件的可靠性,使用時(shí)器件結(jié)溫應(yīng)不超過(guò)最大結(jié)溫的90%進(jìn)行降額。

2.20 輸出電容

除了前文提到的無(wú)片外電容型LDO 外,其他LDO 都有最小輸出電容值要求,輸出電容及其ESR會(huì)影響LDO 的穩(wěn)定性,提高電容值可以改善負(fù)載瞬態(tài)響應(yīng)、提高電源紋波抑制比,但輸出電容過(guò)大往往會(huì)引起上電啟動(dòng)異常。

3 LDO 零極點(diǎn)模型

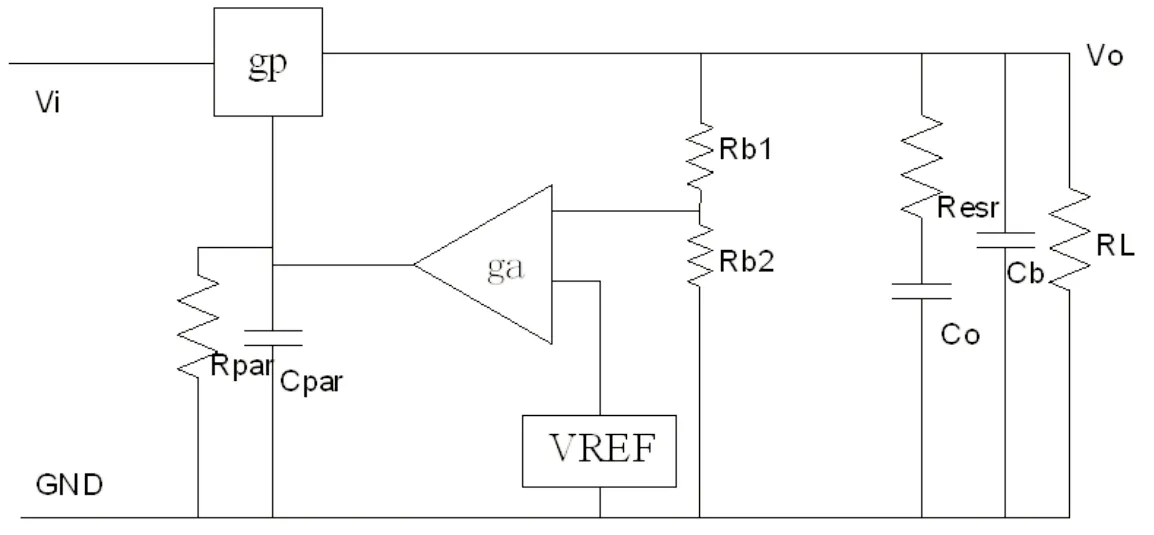

將圖1 的反饋環(huán)路斷開(kāi),可以得到LDO 的交流小信號(hào)模型,如圖2 所示。

圖2 小信號(hào)模型

根據(jù)系統(tǒng)的開(kāi)環(huán)傳遞函數(shù),可以計(jì)算出零極點(diǎn)[15]:

LDO 系統(tǒng)通常包含了三個(gè)極點(diǎn)和一個(gè)零點(diǎn):Po是由輸出端大電容產(chǎn)生的,隨著負(fù)載電流變化;Pa是功率極點(diǎn),由誤差放大器的輸出和功率管輸入?yún)?shù)決定;Pb是由高頻旁路電容產(chǎn)生的;ZESR是由輸出電容等效串聯(lián)電阻產(chǎn)生的。

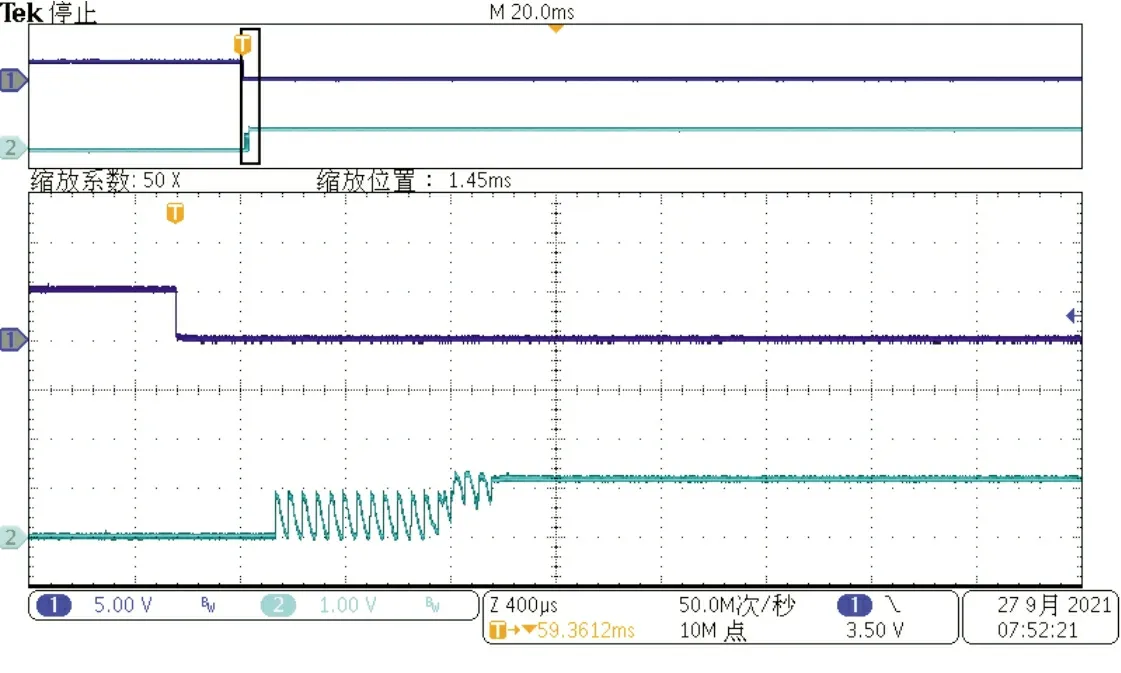

4 LDO 輸出震蕩的原因

LDO 輸出震蕩波形如圖3 所示,可以看出LDO 處于輸出震蕩狀態(tài)。綜合實(shí)際應(yīng)用情形,發(fā)生輸出震蕩的情況有:輸入上電、輸出負(fù)載跳變,實(shí)際案例中發(fā)生過(guò)常溫和高溫狀態(tài)正常,低溫時(shí)輸出震蕩的情況,也發(fā)生過(guò)采用不同的輸出電容輸出不穩(wěn)定的情況。當(dāng)LDO 環(huán)路補(bǔ)償不足時(shí),在外界因素如溫度變化、輸入電壓跳變或者輸出負(fù)載電流突變等作用下,LDO 輸出震蕩,因此需要對(duì)其進(jìn)行環(huán)路補(bǔ)償,總體來(lái)說(shuō),包含外部補(bǔ)償和內(nèi)部補(bǔ)償,外部補(bǔ)償主要是通過(guò)選擇LDO 外圍元件參數(shù)保證LDO 穩(wěn)定工作,內(nèi)部補(bǔ)償主要是從設(shè)計(jì)上進(jìn)行環(huán)路補(bǔ)償,保證在不同條件下,LDO 穩(wěn)定工作。

圖3 LDO輸出震蕩波形

5 LDO 補(bǔ)償方式

LDO 是多極點(diǎn)系統(tǒng),需要環(huán)路補(bǔ)償才可以正常工作,多采用電流環(huán)加電壓環(huán)雙環(huán)路補(bǔ)償方式,電流環(huán)為內(nèi)環(huán),設(shè)計(jì)成低增益高帶寬環(huán)路,電壓環(huán)為外環(huán),設(shè)計(jì)成高增益低帶寬環(huán)路,兩個(gè)環(huán)路為并聯(lián)關(guān)系,在不同的頻段分別起作用,具體的補(bǔ)償方法有以下幾種。

5.1 負(fù)載電容ESR 補(bǔ)償

外部補(bǔ)償方式,利用輸出電容的等效串聯(lián)電阻產(chǎn)生的零點(diǎn)來(lái)提高相位裕度,改善環(huán)路穩(wěn)定性。如果ESR太大,使得零點(diǎn)頻率較低,系統(tǒng)帶寬增加,極點(diǎn)出現(xiàn)在單位增益帶寬內(nèi),相位裕度減小,穩(wěn)定性更差;如果ESR太小,使得零點(diǎn)頻率較高,出現(xiàn)在單位增益帶寬外,沒(méi)有補(bǔ)償作用[12,15-16]。因此,相關(guān)產(chǎn)品手冊(cè)中都會(huì)給出一定輸出電容值條件下,使得LDO 穩(wěn)定工作時(shí),輸出電容ESR隨負(fù)載電流變化的安全范圍。實(shí)際應(yīng)用時(shí),輸出電容的ESR隨溫度、電容材料發(fā)生變化,而且ESR還會(huì)帶來(lái)輸出電壓的過(guò)沖,造成使用困難。

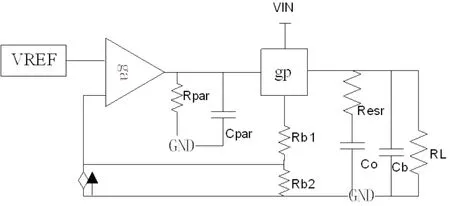

5.2 增加緩沖級(jí)隔離補(bǔ)償

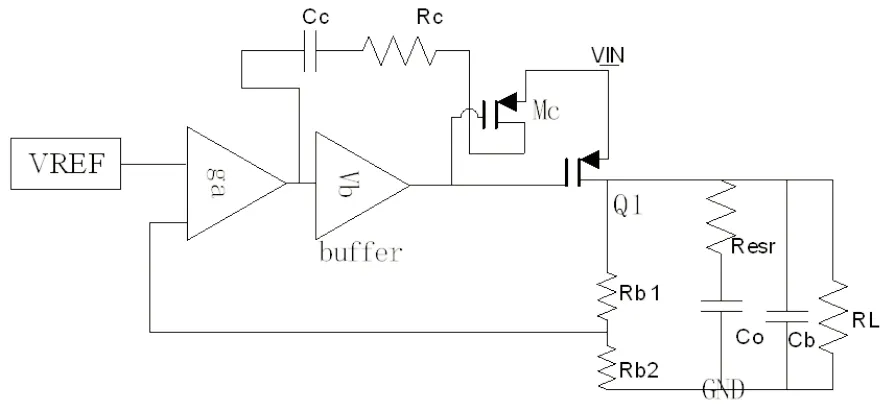

增加緩沖級(jí)隔離補(bǔ)償是在誤差放大器和功率管之間增加緩沖級(jí)進(jìn)行隔離,可以采用較小的ESR實(shí)現(xiàn)補(bǔ)償[15],其結(jié)構(gòu)如圖4 所示。

圖4 增加緩沖級(jí)補(bǔ)償法電路結(jié)構(gòu)圖

5.3 電壓控制電流源補(bǔ)償

反饋環(huán)路中加入了一個(gè)電壓控制電流源(CCSV),如圖5所示,通過(guò)這個(gè)結(jié)構(gòu)在反饋環(huán)路中引入了一個(gè)零點(diǎn)進(jìn)行補(bǔ)償,這種頻率補(bǔ)償結(jié)構(gòu)的穩(wěn)定性可以完全不依賴于外部電容的ESR電阻產(chǎn)生的零點(diǎn)[13]。此外,這種補(bǔ)償方法可以減小電路噪聲,提高輸出電流瞬態(tài)特性[15]。

圖5 反饋環(huán)路中加入壓控電流源補(bǔ)償

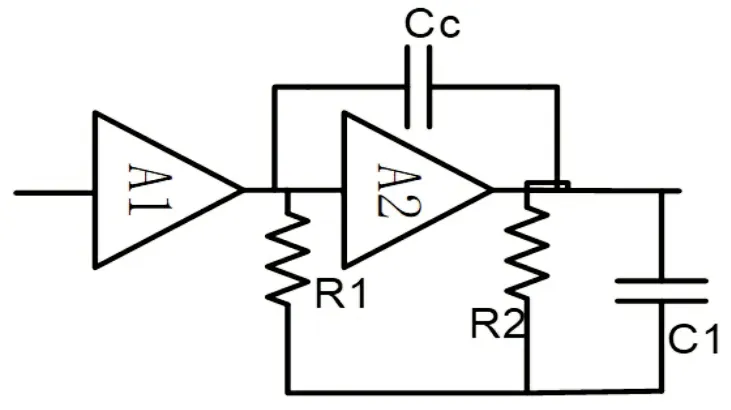

5.4 密勒補(bǔ)償

LDO 中一般采用兩級(jí)運(yùn)放甚至多級(jí)運(yùn)放,功率極點(diǎn)Pa和負(fù)載極點(diǎn)Po距離比較近而且都處于頻率比較低的頻點(diǎn),因此,容易造成相位裕度較小或者環(huán)路不穩(wěn)定。如果在運(yùn)放的輸入端增加一個(gè)輸入電容,可以使得兩個(gè)極點(diǎn)分離,Pa靠近原點(diǎn),Po遠(yuǎn)離原點(diǎn),這樣就可以提高相位裕度,但是,會(huì)使得系統(tǒng)帶寬被限制在一個(gè)相對(duì)比較低的值,而且大的輸入電容占用比較大的芯片面積。利用密勒效應(yīng)[12-13],以兩級(jí)運(yùn)放為例,在第二級(jí)運(yùn)放的輸入和輸出跨接一個(gè)電容Cc,可以等效為在A2的輸入端放置了容值為(1+A2)Cc的電容,極點(diǎn)向原點(diǎn)即低頻方向移動(dòng),輸出極點(diǎn)遠(yuǎn)離原點(diǎn)移動(dòng),實(shí)現(xiàn)了極點(diǎn)分離,這樣就利用一個(gè)較小電容Cc實(shí)現(xiàn)了環(huán)路補(bǔ)償,這種方法稱為密勒補(bǔ)償,如圖6 所示。

圖6 傳統(tǒng)密勒補(bǔ)償

值得說(shuō)明的是,上述密勒補(bǔ)償增加了右半平面零點(diǎn),該零點(diǎn)會(huì)衰減環(huán)路的相位裕度,因此,需要給密勒電容串聯(lián)一個(gè)電阻以抵消該右半平面零點(diǎn)[1]。

5.5 密勒電容倍增補(bǔ)償

電容倍增頻率補(bǔ)償?shù)脑硎峭ㄟ^(guò)采樣流過(guò)電容的電流,在電流鏡的作用下,將其放大K倍,然后反饋到采樣端,這樣等效于將采樣的電流放大了K+1 倍,頻率較低的情況下,容抗增加了K倍[17],原理如圖7 所示。

圖7 密勒電容倍增補(bǔ)償

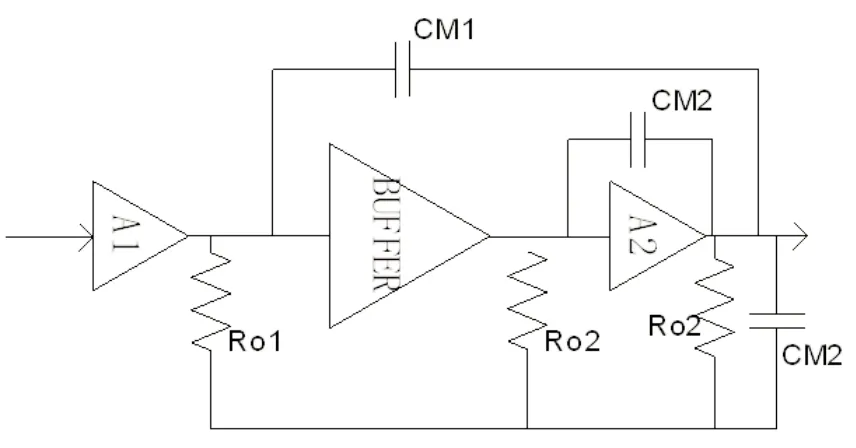

5.6 嵌套式密勒補(bǔ)償

嵌套式密勒電容補(bǔ)償技術(shù)是各種高階增益系統(tǒng)補(bǔ)償設(shè)計(jì)的基礎(chǔ),它是基于傳統(tǒng)的兩級(jí)密勒補(bǔ)償技術(shù)延伸出來(lái)的,通過(guò)一個(gè)外部補(bǔ)償電容CM1 和一個(gè)內(nèi)部補(bǔ)償電容CM2 來(lái)分離極點(diǎn)的位置,如圖8 所示。其中CM1 主要用來(lái)壓縮第一級(jí)的輸出極點(diǎn),CM2 用來(lái)改變兩個(gè)次極點(diǎn)的性質(zhì),分離兩個(gè)次極點(diǎn),或者讓之成為一對(duì)共扼復(fù)極點(diǎn),并且控制其Q值大小,從而改變頻率響應(yīng)特性[17]。

圖8 嵌套式密勒補(bǔ)償

5.7 共源共柵密勒補(bǔ)償

傳統(tǒng)密勒補(bǔ)償會(huì)產(chǎn)生一個(gè)右半平面零點(diǎn)衰減環(huán)路的相位裕度,需要串聯(lián)一個(gè)調(diào)零電阻來(lái)抵消該右半平面零點(diǎn),這增加電路設(shè)計(jì)的復(fù)雜度和成本,為了避免傳統(tǒng)密勒補(bǔ)償?shù)牟蛔阒帲谛酒O(shè)計(jì)時(shí)采用共源共柵密勒補(bǔ)償[1]。

5.8 零點(diǎn)跟蹤負(fù)載電流頻率補(bǔ)償

將誤差放大器和功率管之間增加緩沖級(jí)來(lái)進(jìn)行隔離的方法采用較小的ESR電阻就能起到頻率補(bǔ)償?shù)淖饔茫荒鼙WC整個(gè)負(fù)載范圍的相位裕度,而在實(shí)際設(shè)計(jì)中,為了優(yōu)良的性能,應(yīng)確保其在盡可能寬的工作條件下有足夠大的相位裕度和足夠快的瞬態(tài)響應(yīng)。如果此時(shí),系統(tǒng)內(nèi)部有一個(gè)零點(diǎn)產(chǎn)生,并且此零點(diǎn)的位置也是隨著負(fù)載電流的變化而變化,當(dāng)負(fù)載電流變大的時(shí)候,零點(diǎn)的位置也移向高頻,并且此零點(diǎn)和輸出極點(diǎn)的位置相差不大,此零點(diǎn)就可以補(bǔ)償輸出極點(diǎn)造成的附加相位[15,17],具體電路如圖9 所示。

圖9 零極點(diǎn)跟蹤負(fù)載電流補(bǔ)償

在傳統(tǒng)的電路中增加一個(gè)電阻Rc,一個(gè)電容Cc,同時(shí)再增加一個(gè)PMOS 管Mc(工作在線性區(qū)MOS 管相當(dāng)于一個(gè)可變電阻),使得Mc的柵極和調(diào)整管的柵極相連,同時(shí)保持Cc、Rc、Mc串聯(lián),負(fù)載電流變化時(shí),極點(diǎn)和零點(diǎn)位置都發(fā)生變化,達(dá)到增加相位裕度、保證穩(wěn)定的目的。

5.9 阻尼系數(shù)控制頻率補(bǔ)償

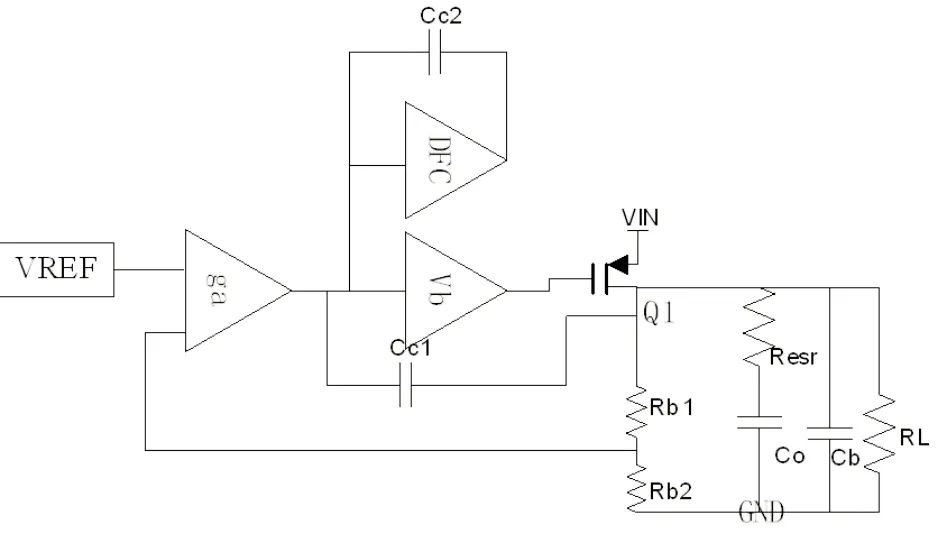

采用級(jí)間密勒補(bǔ)償在環(huán)路中會(huì)產(chǎn)生一個(gè)頻率非常低的主極點(diǎn),然后由于受到兩個(gè)次極點(diǎn)的影響,環(huán)路的穩(wěn)定性能不佳,此時(shí)如果通過(guò)一個(gè)阻尼系數(shù)控制單元(DFC)使得兩個(gè)次極點(diǎn)的位置調(diào)整到單位增益帶寬以外,降低次極點(diǎn)對(duì)環(huán)路相位的影響,保證在單位增益帶寬以內(nèi)只有一個(gè)主極點(diǎn),則可以大幅度提高環(huán)路的穩(wěn)定性[17],阻尼系數(shù)控制頻率補(bǔ)償電路如圖10 所示。

圖10 阻尼系數(shù)控制頻率補(bǔ)償

6 結(jié)論

本文討論了LDO 主要性能和關(guān)鍵指標(biāo),分析了LDO 輸出震蕩的機(jī)理和環(huán)路補(bǔ)償方法,針對(duì)工程應(yīng)用提出了LDO 選型的建議,有助于硬件工程師增強(qiáng)對(duì)LDO 電源芯片的認(rèn)識(shí)、正確選型和應(yīng)用。