快速瞬態(tài)響應(yīng)低噪聲無片外電容LDO

張濤,吳小奔,劉勁

(武漢科技大學(xué) 信息科學(xué)與工程學(xué)院,湖北 武漢 430081)

隨著半導(dǎo)體工藝尺寸的不斷縮小和人工智能技術(shù)的快速發(fā)展,各種便攜式設(shè)備開始融入人們的生活。在電池供電的便攜式設(shè)備系統(tǒng)內(nèi)部,射頻收發(fā)器、調(diào)制解調(diào)器、核心處理器、顯示驅(qū)動以及存儲等模塊所需要的電源電壓不盡相同。例如,為保證PCB 級信號的完整性,接口電路通常需要1.8,2.5 和3.3 V 的供電電壓,而核心電路部分則需要1.2 V 甚至更低的電壓以防止納米級工藝的MOS 管被擊穿[1]。電源管理系統(tǒng)首先通過高效的開關(guān)電源轉(zhuǎn)換器將鋰電池電壓進行降壓處理,隨后利用多個低壓差線性穩(wěn)壓器(Low Dropout Regulator,LDO)為各模塊提供獨立的電源電壓。這些LDO 通常需要外接微法級的電容來滿足快速瞬態(tài)響應(yīng)、穩(wěn)定性、高電源抑制、低噪聲等要求[2]。然而,對于便攜式的電子產(chǎn)品,大容量的片外電容消耗了PCB 布局面積,不利于集成,為解決這一問題,采用內(nèi)部補償方式的無片外電容型LDO 被提出[3-5]。

另外,現(xiàn)代移動設(shè)備強調(diào)多功能的大規(guī)模集成和快速運行速度,這使得內(nèi)部模塊越來越耗電,而且它們的動態(tài)電流曲線往往包含快速變化成分,這對LDO的帶載能力以及在負載瞬變時產(chǎn)生的過沖及下沖提出了嚴格的要求[6]。Al-Shyouke 等[7]通過在誤差放大器與功率管之間加入一個自適應(yīng)偏置的電壓緩沖器來增大功率管柵端的擺率,從而增強了瞬態(tài)響應(yīng)。Maity等[8]對誤差放大器采用自適應(yīng)偏置技術(shù),在重載時增大環(huán)路的帶寬來改善瞬態(tài)響應(yīng)。上述方法在負載電流小于100 mA 時效果顯著,而當負載電流增大后,其有效性可能會降低。

針對上述問題,本文提出了一種應(yīng)用于便攜式設(shè)備的無片外電容NMOS 型LDO,將功率管柵極與一較大容值的電容進行串聯(lián)構(gòu)成浮柵結(jié)構(gòu),并通過輔助運放對電容充放電,為功率管柵極提供直流工作點,輔助運放采用推挽輸出,且只有當電容充電時才需要電荷泵提供少量電荷,極大地減小了片內(nèi)集成電荷泵的版圖面積和噪聲影響。另外,取樣輸出電流動態(tài)調(diào)整誤差放大器輸出,并通過獨特的偏置技術(shù)保證其不會超出誤差放大器的輸出電壓范圍,提高了電路的瞬態(tài)響應(yīng)能力。除輔助運放采用電荷泵供電外,其他電路均由內(nèi)部LDO 供電,該LDO 對輸入電壓進行預(yù)穩(wěn)壓處理,進一步提高了系統(tǒng)的電源抑制比。

1 LDO 芯片系統(tǒng)設(shè)計

1.1 系統(tǒng)結(jié)構(gòu)

本文的LDO 系統(tǒng)結(jié)構(gòu)如圖1 所示,核心部分由誤差放大器(Error Amp)、失調(diào)電容COFFSET、伺服放大器(Servo)、NMOS 功率管以及高阻反饋網(wǎng)絡(luò)RF1/RF2構(gòu)成。

圖1 LDO 芯片系統(tǒng)結(jié)構(gòu)圖Fig.1 The system structure of LDO

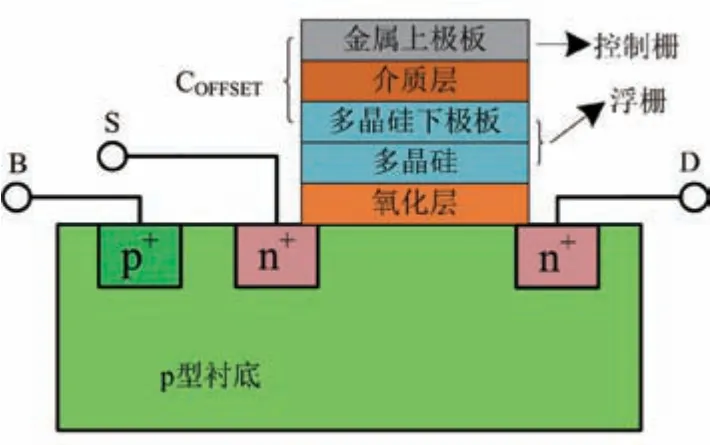

NMOS 功率管的柵端與誤差放大器的輸出通過失調(diào)電容COFFSET耦合在一起,構(gòu)成類似浮柵的結(jié)構(gòu),如圖2 所示,電容COFFSET為MIP 電容,由于平衡狀態(tài)時伺服放大器不會對外充放電,因此電容的下極板與功率管的柵極可被當作浮柵,電容上極板則作為控制柵。浮柵上的電壓VGATE為控制柵上的電壓與電容兩端的電壓VOFFSET之和,即:

圖2 電容與功率管級聯(lián)物理結(jié)構(gòu)示意圖Fig.2 Capacitor and powermos cascade physical structure

非平衡狀態(tài)(負載變化)時,伺服放大器參與調(diào)整,該放大器通過向電容充放電來改變失調(diào)電壓VOFFSET,進一步改變VGATE的大小。具體工作方式為:伺服放大器通過比較VA和VVREF,當VA高于VVREF時,伺服電路為失調(diào)電容充電,使VGATE升高,隨后反饋環(huán)路快速響應(yīng),將VA的值降低到VVREF;同理,當VA低于VVREF時,伺服電路從失調(diào)電容抽取電流,VGATE降低使VA上升到VVREF。

電壓VVREF是由動態(tài)基準模塊(Variable Ref)產(chǎn)生。為了使誤差放大器在負載響應(yīng)時有最大的動態(tài)范圍,VVREF會隨著輸出電流變化。如圖1 所示,電流取樣電路取樣輸出電流,并按一定的比例送到動態(tài)基準電路。當負載電流趨于滿載時,VVREF最大;當負載電流趨于零時,VVREF有最小值。因此,當負載突然增大后,VA可以從一個很低的值快速上升到一個較高的值,使功率管快速提供大電流。

功率管采用NMOS,其源跟隨器的工作方式相比于PMOS 的共源極工作方式,具有更好的負載調(diào)制能力和電源噪聲抑制能力[9],同時具有簡單的頻率補償結(jié)構(gòu)[10]。另一個優(yōu)點是,在相同的電流驅(qū)動能力下,NMOS 所占用的版圖面積遠小于PMOS。然而,為保證NMOS 輸出級正常工作,柵端電壓需要比輸出電壓高一個VGS的壓差,這在低壓工作時會使柵端電壓高于電源電壓。一種解決辦法是使用內(nèi)部電荷泵電路提供一個比電源電壓更高的電壓為誤差放大器供電。這需要電荷泵給誤差放大器提供大電流來快速調(diào)整功率管的柵端電壓,保證良好的負載瞬態(tài)響應(yīng)[11]。然而,大電流的電荷泵產(chǎn)生了更大的噪聲,并占用了較大的版圖面積。本文的結(jié)構(gòu)中電荷泵僅給伺服放大器供電,且只有在失調(diào)電容充電期間才會有少量電流流出,極大地減小了電荷泵的版圖面積和噪聲影響。

每個故事都是旅行故事,都是空間的實踐。一個人因為突如其來的遭遇來到一片全然陌生的地域,在經(jīng)歷矛盾糾結(jié)的自我否定之后,更開放地迎接全新的人生之旅,更具有同理心地去理解異質(zhì)文化的諸多內(nèi)容,如此,一個人空間地域的轉(zhuǎn)換也是一個人自身生命之旅的主體遷徙。跨族群、跨地域、跨文化的故事書寫往往都是借助于空間旅行得以啟動,而其中的孤獨漂移意味著不可避免地沉浮在講述故事的人與異質(zhì)、具有多重建構(gòu)的他者之間。

1.2 電路瞬態(tài)性能分析

負載跳變時,誤差放大器快速響應(yīng),由于失調(diào)電容的存在,功率管的柵端電壓VGATE的變化量為:

式中:Cpar為功率管柵端電容;COFFSET為失調(diào)電容容值;ΔVA為誤差放大器輸出電壓的變化量。

由于COFFSET的值遠大于Cpar,因此VA的變化快速傳遞到VGATE,伺服電路僅需提供少量的電荷來改變VGATE,對應(yīng)地,電荷泵僅需提供少量電荷,小電流的電荷泵即可滿足需求。

當負載由輕載跳變?yōu)橹剌d時,輸出電壓出現(xiàn)下沖,一方面,由于輸出端為NMOS 功率管的源端,因此NMOS 管直接響應(yīng)從而增大輸出電流,同時取樣電流也隨之增大使VVREF上升;另一方面,該下沖被反饋到誤差放大器的反向輸入端,使VA和VGATE上升,進一步增大輸出電流。當負載由重載跳變?yōu)檩p載時,同理。在此期間,伺服放大器不斷比較VA和VVREF,向電容COFFSET抽取或注入電流,將失調(diào)電壓維持在合適的值。

1.3 系統(tǒng)穩(wěn)定性分析

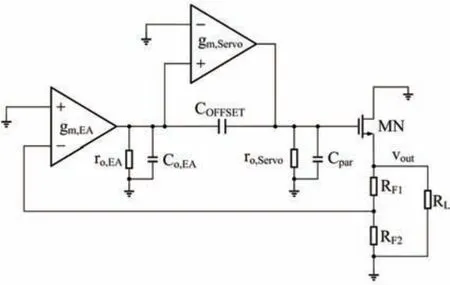

圖3 為LDO 環(huán)路小信號示意圖,由圖可以得到誤差放大器的輸出極點為:

圖3 LDO 環(huán)路小信號示意圖Fig.3 The small signal of LDO loop

式中:ro,EA為誤差放大器的輸出阻抗;Co,EA為誤差放大器的輸出電容。

LDO 電路的輸出極點為:

式中:gm,MN為NMOS 功率管的跨導(dǎo);COUT為LDO 的輸出電容。對于無片外電容設(shè)計,該輸出電容表現(xiàn)為輸出端各寄生電容總和,其值非常小,因此輸出極點為高頻極點。

Servo 放大器和失調(diào)電容構(gòu)成的正反饋結(jié)構(gòu)的零極點可通過圖4 的小信號電路進行計算,得到的傳輸函數(shù)和零極點為:

圖4 伺服放大器與COFFSET小信號電路圖Fig.4 Small signal circuit diagram of Servo amplifier and COFFSET

該結(jié)構(gòu)產(chǎn)生了一對左半平面的零極點,若伺服放大器的極性互換,與COFFSET構(gòu)成負反饋結(jié)構(gòu),則所產(chǎn)生的零點變?yōu)橛野肫矫娴牧泓c,該零點頻率較低,因此對系統(tǒng)的穩(wěn)定性產(chǎn)生了惡化。

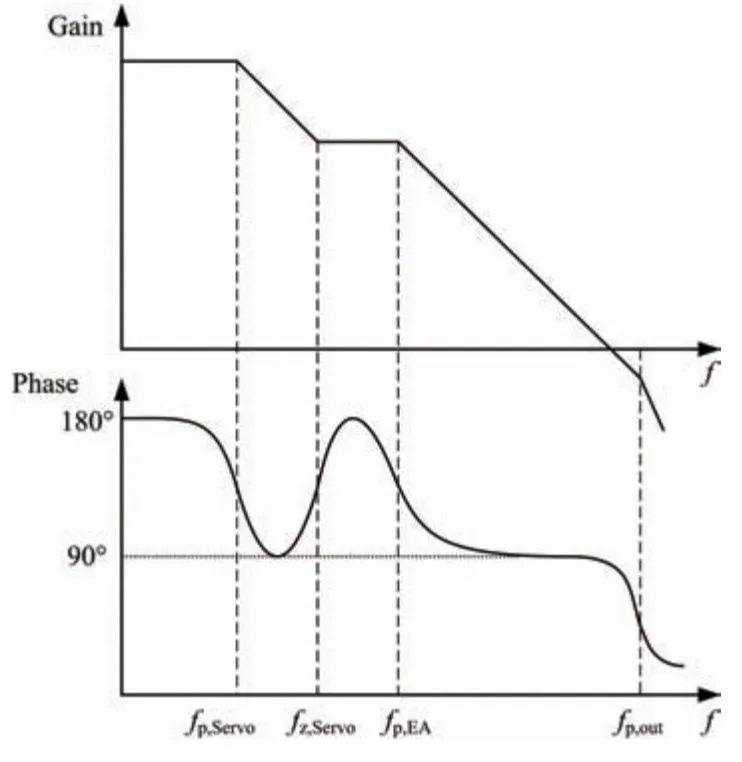

該系統(tǒng)是一個帶內(nèi)雙極點單零點的系統(tǒng)。設(shè)計時使COFFSET的值遠大于Co,EA,同時,Servo 放大器采用推挽輸出結(jié)構(gòu),使得ro,Servo遠大于ro,EA,因此,fp,Servo為系統(tǒng)主極點,fp,EA為次極點,兩極點頻率數(shù)量級相差較大,另外,根據(jù)上述公式,零點fz,Servo位于兩極點之間,提升了系統(tǒng)的相位裕度,保證了系統(tǒng)的穩(wěn)定性,系統(tǒng)的零極點分布如圖5 所示。

圖5 LDO 環(huán)路零極點分布Fig.5 The zero-pole distribution of LDO loop

2 LDO 芯片核心電路模塊設(shè)計

圖6 為誤差放大器的電路實現(xiàn),其結(jié)構(gòu)為單級折疊結(jié)構(gòu),相比于使用MOS 管作為輸入對管,NPN 管具有更好的瞬態(tài)響應(yīng)能力以及更大的電流跨導(dǎo)效率,可以得到更高的增益。與一般的n 型LDO 中誤差放大器由電荷泵直接供電不同,該電路由內(nèi)部穩(wěn)壓模塊供電,避免了電荷泵噪聲直接耦合到誤差放大器輸出端,有效地降低了該電路的電源抑制比(Power Supply Ripple Rejection,PSRR)需求。

圖6 誤差放大器電路Fig.6 Error amplifier circuit

動態(tài)基準電路的電路實現(xiàn)如圖7 所示,正如前文所述,動態(tài)基準電路產(chǎn)生一個隨輸出電流變化的動態(tài)基準電壓VVREF,可以采用電流比較的方式實現(xiàn)該功能。同時為防止VVREF的值超出誤差放大器的輸出范圍,引入M15 和M16 對VVREF進行鉗位。ISENCE為電流取樣電路按照一定比例取樣輸出電流的結(jié)果,IREF為帶隙基準電流,M10 和M12 以相同的比例映射這兩個電流。當ISENCE與IREF相等時,兩尺寸相同的倒比管M13和M14 構(gòu)成的分壓器使VVREF等于VDD/2,此時M15 和M16均截止;當ISENCE大于IREF時,節(jié)點A 有額外的電流流出,VVREF上升,當上升至某一值時,M16管導(dǎo)通,VVREF的最大值由M16 決定,為VB1+同理,當ISENCE小于IREF時,VVREF下降,其最小值為VB2-VGS,15。

圖7 動態(tài)基準電路Fig.7 Dynamic reference circuit

由于伺服放大器的作用,平衡狀態(tài)時誤差放大器的輸出與動態(tài)基準模塊的輸出相等,即誤差放大器的輸出范圍為(VB2-VGS,15,VB1+),為防止誤差放大器中M4 和M6 進入線性區(qū)導(dǎo)致增益下降,M4 和M6 分別由VB1和VB2偏置,在分別滿足≤VTH,4以及VGS,15≤VTH,6的情況下,可以保證M4 和M6 在整個輸出范圍內(nèi)始終工作在飽和區(qū),通過使用較大寬長比的M15 和M16,使其工作在亞閾值區(qū),可以滿足上述條件。

圖8 為伺服放大器的原理圖,伺服放大器通過比較VA與VVREF來為失調(diào)電容充放電。通過采用推挽輸出級,平衡狀態(tài)時不消耗功耗,只有當失調(diào)電容需要充電時,才會有電流從電荷泵流出,M22 尺寸較小,具有非常小的源漏寄生電容,而功率管柵電容較大,電容分壓后在功率管的柵極表現(xiàn)出非常小的電荷泵開關(guān)噪聲。此時系統(tǒng)的輸出噪聲主要由帶隙基準模塊產(chǎn)生,可以通過在帶隙輸出端使用RC 低通濾波來降低噪聲。

為實現(xiàn)推挽輸出,引入M23 管作為開關(guān)管,使M24 和M21 交錯導(dǎo)通。平衡狀態(tài)時VA等于VVREF,電路不對外充放電,可以合理設(shè)計B 點的電壓值,使M23 和M24 工作在弱反型區(qū),由于M23 和M24 的閾值電壓約為0.7 V,可以將B 點電位設(shè)置為0.6 V,此時M23 的柵極電壓需要設(shè)置為1.2 V,可以直接采用帶隙基準電壓,避免額外的偏置電路消耗功耗。當VA大于VVREF時,B 點電位下降,M23 導(dǎo)通,M24 截止,伺服電路通過M22 為失調(diào)電容充電;同理,當VA小于VVREF時,M23 截止,M24 導(dǎo)通,M25 從VGATE抽取電流為失調(diào)電容放電。

3 版圖與結(jié)果

本文的LDO 芯片采用HHGrace 0.35 μm BCD 工藝流片,整體芯片尺寸為1500 μm×1000 μm,LDO 整體版圖如圖9 所示。

圖9 LDO 版圖Fig.9 Layout of LDO

圖10 為空載時的LDO 環(huán)路穩(wěn)定性仿真曲線,該無片外電容LDO 的低頻增益為61 dB,帶寬為2.51 MHz,相位裕度為70°。即使在外接0.1 μF 電容的情況下,系統(tǒng)的相位裕度仍有42°,系統(tǒng)具有極高的穩(wěn)定性。

圖10 環(huán)路穩(wěn)定性曲線。(a)增益;(b)相位裕度Fig.10 Loop stability curves.(a) Gain;(b) Phase margin

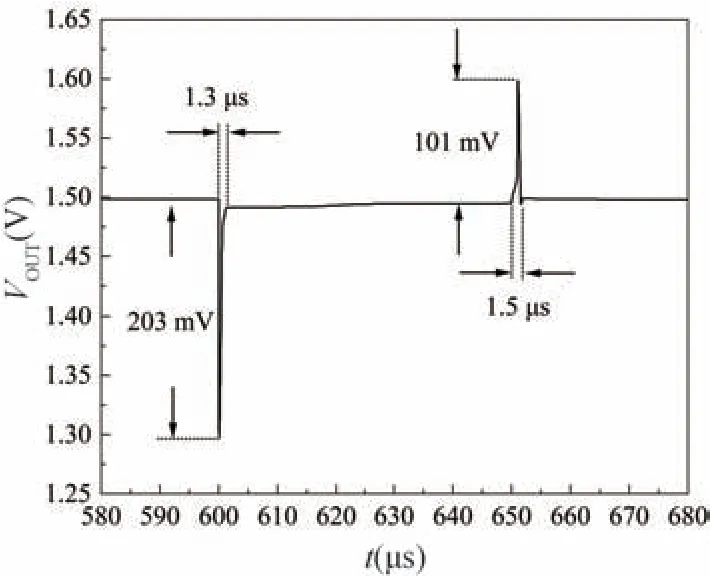

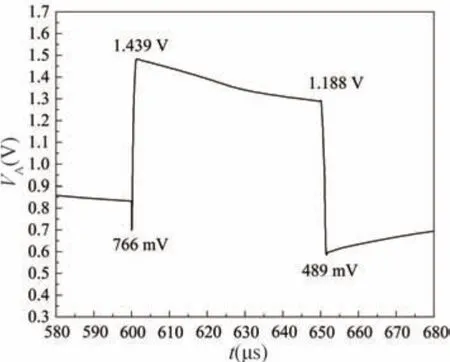

LDO 的負載瞬態(tài)響應(yīng)曲線如圖11 所示,當沒有外接電容時,在1 μs 的瞬態(tài)躍遷時間內(nèi),負載從1 μA跳變到400 mA,下沖為203 mV,響應(yīng)時間1.3 μs;負載從400 mA 跳變到1 μA,上沖為101 mV,響應(yīng)時間1.5 μs。另外,圖12 為負載發(fā)生跳變時誤差放大器的輸出電壓VA的變化,可以看出,在負載跳變時,其具有較大的輸出動態(tài)范圍。

圖11 負載瞬態(tài)響應(yīng)曲線Fig.11 Load transient response curves

圖12 VA隨負載變化的曲線Fig.12 The curve of VA with respect to load

圖13 為系統(tǒng)輸出噪聲曲線,在1 kHz 時的噪聲值為63 nV·Hz-1/2,在10 Hz 到100 kHz 的頻段內(nèi)進行積分求和,得到的噪聲值為14 μV·Hz-1/2。

圖13 輸出噪聲Fig.13 The result of output noise

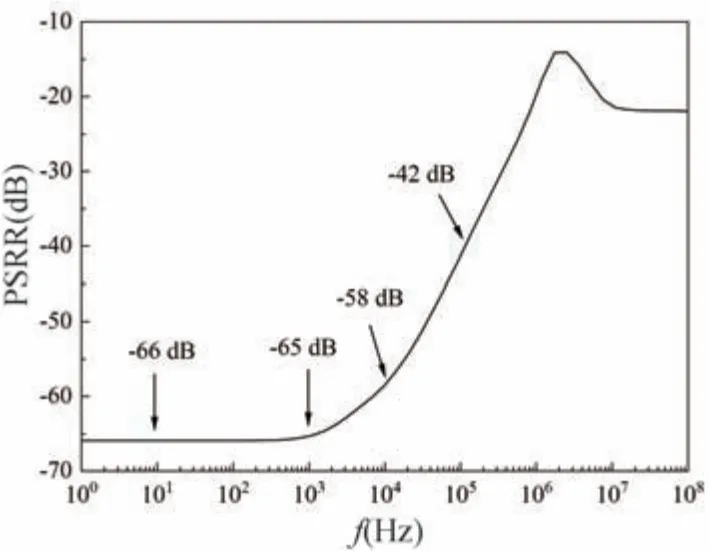

圖14 為LDO 電源抑制比(PSRR)的仿真曲線,可以看到,低頻段(100 Hz)的PSRR 為-66 dB,在1,10,100 kHz 時的PSRR 分別為-65,-58,-42 dB,系統(tǒng)具有較好的電源紋波抑制特性。

圖14 電源抑制比仿真Fig.14 Simulation of PSRR

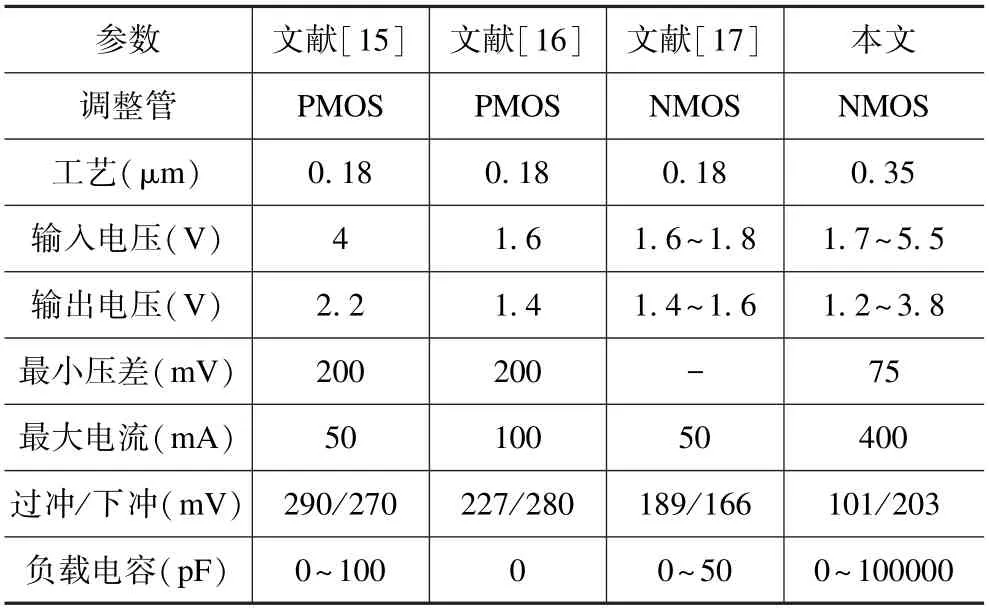

本文LDO 與其他文獻中LDO 的性能參數(shù)對比如表1 和表2 所示。可以看出,本文LDO 具其極低的輸出噪聲,適用于對噪聲敏感的電路,例如VCO;較大的帶載能力和良好的瞬態(tài)特性則適合為DSP、FPGA等供電。另外,本文的LDO 還具有寬泛的輸入輸出電壓范圍、低壓差、高穩(wěn)定性等優(yōu)點。

表1 與其他文獻電源抑制比及噪聲參數(shù)的對比Tab.1 Comparison of PSRR and noise parameters with other literature

表2 本文LDO 其他參數(shù)的對比Tab.2 Comparison of other parameters of the proposed LDO

4 結(jié)論

本文基于浮柵結(jié)構(gòu)設(shè)計了一種無片外電容NMOS型LDO,通過取樣輸出電流控制誤差放大器的輸出,顯著改善了LDO 的瞬態(tài)特性。由電容和具有推挽輸出級的輔助運放提供功率管的柵極偏置,極大地減小了電荷泵的噪聲耦合。基于HHGrace 0.35 μm BCD 工藝進行版圖設(shè)計和后仿真驗證,負載電流在1 μs 內(nèi),在1 μA 至400 mA 跳變時,輸出電壓的上沖和下沖分別為101 mV 和203 mV,穩(wěn)定時間小于1.5 μs;輸出噪聲電壓在10 Hz 到100 kHz 頻段內(nèi)的積分值為14 μV·Hz-1/2;LDO 的低頻PSRR 為-66 dB。通過與其他文獻研究工作的對比,該LDO 性能較優(yōu),能夠很好地滿足現(xiàn)代便攜式設(shè)備的應(yīng)用需求。