基于FPGA的便攜式高速測試工裝設計

任敏 魏驍 黃毅龍

摘? 要:針對某型高速嵌入式信息安全設備的測試需求,設計一種基于FPGA的便攜式高速測試工裝。該測試工裝包括上位機控制臺和下位機測試平臺兩部分,上位機控制臺采用軟件形式實現,完成測試樣本下發和測試數據儲存,并提供人機交互界面;下位機測試平臺采用FPGA作為核心處理單元,完成與上位機控制臺及被測設備的接口轉換和數據轉發。測試結果表明:基于FPGA的便攜式高速測試工裝能夠搭建穩定可靠的模擬測試環境,滿足某型高速嵌入式信息安全設備的能力測試需求。

關鍵詞:測試工裝;FPGA;高速;便攜式

中圖分類號:TP206+.1? 文獻標識碼:A? 文章編號:2096-4706(2023)19-0037-05

Design of Portable High-speed Testing Fixture Based on FPGA

REN Min, WEI Xiao, HUANG Yilong

(National Computer System Engineering Research Institute of China, Beijing? 100083, China)

Abstract: A portable high-speed testing fixture based on FPGA is designed to meet the testing requirements of a high-speed embedded information security device. The testing fixture includes two parts: the upper computer console and the lower computer testing platform. The upper computer console is implemented by software, which distributes testing samples, saves testing data, and provides the man-machine interaction interface. FPGA is used as the core processing unit in the lower computer testing platform, which completes interface conversion and data forwarding with the upper computer console and the tested device. Testing results show that the portable high-speed testing fixture based on FPGA can build a stable and reliable simulation testing environment to meet the capability testing requirements of the high-speed embedded information security device.

Keywords: testing fixture; FPGA; high-speed; portable

0? 引? 言

嵌入式信息安全設備主要應用于衛星通信領域的信息安全加密保護,通常采用獨立的板卡或者模塊形式實現[1],使用時通過專用接口嵌入通信宿主設備內部,隨通信宿主設備一起開機啟動,并由通信宿主設備提供電源和數據。嵌入式信息安全設備和通信宿主設備通常由不同廠家負責研制,通信宿主設備不能配合嵌入式信息安全設備開展全周期測試。測試工裝作為一種常用的陪測設備[2],可以模擬通信宿主設備的硬件接口和軟件功能[3],配合嵌入式信息安全設備搭建模擬測試環境,驗證被測設備的各項能力指標。

測試工裝通常包括上位機控制臺和下位機測試平臺兩部分[4,5],傳統的測試工裝核心處理單元多采用CPU+FPGA架構實現[6,7],CPU連接上位機,實現下位機測試平臺與上位機控制臺的接口通信和指令解析功能,FPGA連接被測設備,實現下位機測試平臺與被測設備的接口轉換和數據轉發功能,這種設計方案功能劃分比較清晰,設計相對容易實現,但是在高速測試應用方面具有一定的局限性。比如:低性能CPU處理能力差、接口速率慢,不能滿足被測設備的高速處理能力的測試需求,而高性能CPU一般體積大、功耗高,平臺設計多為大型獨立式設備[8],外出測試攜帶不方便,并且需要同時開發維護CPU和FPGA兩個處理單元,人員成本相對較高。本文針對某型高速嵌入式信息安全設備的能力測試需求,同時考慮降低設計成本、提高設備便攜性,提出一種基于FPGA的便攜式高速測試工裝設計。

1? 方案設計

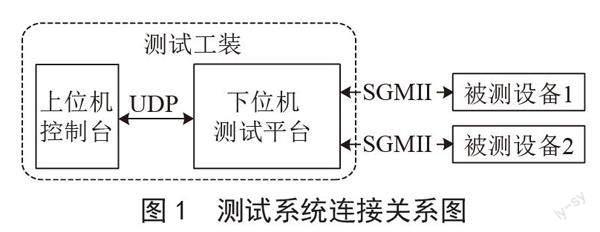

基于FPGA的便攜式高速測試工裝包括上位機控制臺和下位機測試平臺兩部分,上位機控制臺以軟件形式實現,主要完成測試樣本生成和指令下發、測試數據實時存儲、測試結果統計和顯示等功能,并提供人機交互界面,上位機控制臺軟件安裝運行在通用測試計算機中。下位機測試平臺用于模擬通信宿主設備,測試平臺提供的物理接口與通信宿主設備完全一致,可以為嵌入式被測設備提供安裝位置、供電電源以及數據通路。某型高速嵌入式信息安全設備的業務加解密處理速率不低于300 Mbit/s,對外數據通信采用高速SGMII接口實現,為了滿足其測試應用需求,下位機測試平臺對上采用UDP協議的千兆網口實現與上位機控制臺的接口通信和數據交互,對下采用SGMII高速接口實現與被測設備的接口轉換和數據轉發。測試平臺可以同時安裝兩塊嵌入式信息安全設備,模擬兩個通信終端之間的傳輸信息的加密和解密過程,整個測試系統連接關系如圖1所示。

1.1? 硬件設計

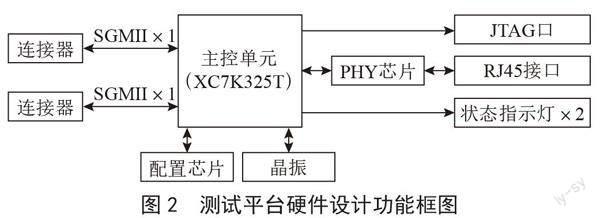

下位機測試平臺的核心處理單元采用1片高性能FPGA實現,FPGA選用XILINX公司目前市場廣泛應用的XC7K325T芯片,XC7K325T內部集成了豐富的邏輯單元和塊RAM存儲資源,并且具有8個GTX高速序列化接口,是一款性價比性相對較高的FPGA芯片,滿足便攜式高速測試工裝的接口通信和數據處理需求。測試平臺硬件功能原理如圖2所示,FPGA對外輸出2路獨立的SGMII接口分別連接兩塊嵌入式被測設備,輸出1路千兆網口連接上位機控制臺,輸出2路指示燈分別顯示兩塊被測設備的運行狀態。測試平臺的SGMII接口在物理形態上與被測的某型高速嵌入式信息安全設備配對設計,采用航空插頭連接器實現;千兆網口在物理形態上采用標準RJ45形式實現,標準網線可以直接接入連接。測試平臺硬件設計遵循小型化原則,配套的結構機殼便攜小巧,兩塊嵌入式被測設備通過測試平臺上方的對應接口進行插接安裝,操作過程方便容易。

1.2? 軟件設計

測試工裝軟件包括上位機控制臺軟件和下位機測試平臺FPGA軟件兩部分。

1.2.1? 上位機控制臺軟件

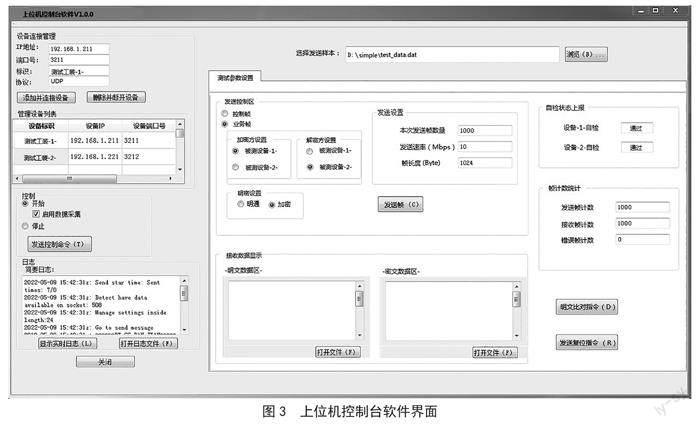

上位機控制臺軟件在Qt Creator 5.5環境下開發,該軟件提供了大量的API和實用工具,界面形式友好,開發效率較高。上位機控制臺主要實現測試需要的測試數據生成、控制指令下發、實時數據存儲、數據收發統計、自檢狀態監控、重要日志上報等功能。通過上位機控制臺軟件可以便捷地的執行各項測試指令,同時直觀地顯示測試結果,便于測試人員統計分析,上位機控制臺軟件界面如圖3所示,整個軟件界面可劃分為設備連接管理、日志顯示、發送控制、接收數據顯示、自檢狀態上報、幀計數統計等幾個重要功能。

1)設備連接管理:主要用于管理和配置下位機控制臺的網絡通信參數,包括IP地址、端口號、設備標識、通信協議等,實現上位機控制臺與下位機測試平臺的千兆網絡連接和數據通信。

2)日志顯示:主要用于完成測試過程中重要信息的實時上報顯示,輔助測試人員分析解決問題。

3)發送控制:主要用于管理和設置明文樣本數據的發送指令參數,包括:測試幀類型、加密方設備和解密方設備、明密方式、發送幀的數量、發送速率控制、發送幀的長度等。

4)接收數據顯示:主要用于讀取顯示本地存儲的測試數據,包括加密后密文測試數據和解密后明文測試數據。

5)自檢狀態上報:主要用于顯示被測設備的自檢狀態信息,監控被測設備的自身運行狀態。

6)幀計數統計:主要用于統計顯示本次測試的發送幀、接收幀和錯誤幀的具體數量,通過相關數據分析驗證被測設備的加解密處理能力。

1.2.2? 下位機測試平臺FPGA軟件設計

下位機測試平臺FPGA軟件在XILINX公司的Vivado 18.3環境下開發,編程采用Verilog語言,FPGA軟件主要實現測試平臺與上位機控制臺之間、測試平臺與被測設備之間的通信接口轉換和測試數據轉發功能。FPGA內部功能模塊設計如圖4所示,主要包括UDP接口控制模塊、協議處理模塊、通道切換控制模塊、2路獨立的SGMII接口控制模塊、FIFO存儲模塊。

1)UDP接口控制模塊:主要用于實現標準UDP通信協議的數據收發處理,完成下位機測試平臺與上位機控制臺的千兆網通信。

2)協議處理模塊:主要用于實現下行測試數據的協議解析和上行測試數據的協議封裝。

3)通道切換控制模塊:主要用于控制下行測試數據分流輸出至兩路獨立的SGMII接口,同時控制兩路獨立SGMII接口發送的上行數據分時輸出至UDP通信接口。

4)SGMII接口控制模塊:主要用于實現與被測設備的SGMII接口收發通信,兩路SGMII接口功能獨立,該模塊通過調用FPGA內部IP核形式實現。

5)FIFO存儲模塊:主要用于實現模塊之間的數據緩沖和速率匹配,該模塊通過調用FPGA內部IP核形式實現。

1.3? 工作流程

測試工裝主要用于測試某型高速嵌入式信息安全設備的加解密處理能力,整個測試系統的工作流程如圖5所示。

1)通過上位機控制臺生成明文測試樣本,設置明文測試樣本幀的發送數量和發送速率。

2)上位機控制臺按照設置的指令參數將明文測試樣本下發至測試平臺,并實時統計發送幀計數,測試平臺將明文樣本數據轉發至加密方被測設備進行加密處理。

3)加密方被測設備將處理后的加密測試數據發送回測試平臺,并通過測試平臺轉發至上位機控制臺。

4)上位機控制臺接收加密測試數據,并將加密測試數據按順序寫入本地文件,同時將加密測試數據下發至測試平臺,通過測試平臺將加密測試數據轉發至解密方被測設備進行解密處理。

5)解密方被測設備將處理后的解密測試數據發送回測試平臺,并通過測試平臺轉發至上位機控制臺。

6)上位機控制臺接收解密測試數據,實時統計接收幀計數,同時將接收的解密測試數據寫入本地文件。

7)測試數據發送完成,通過上位機控制臺讀取本地存儲解密測試數據,將解密測試數據與明文測試樣本逐幀進行比對,實時統計錯誤幀計數,并將錯誤幀信息通過日志實時上報。

8)比對完成后,統計上位機控制臺界面顯示的發送幀計數、接收幀計數、錯誤幀計數、實時日志等信息,并對測試結果進行記錄和分析。

2? 測試驗證

采用測試工裝對某型高速嵌入式信息安全設備進行測試驗證。按照圖6所示連接關系搭建模擬測試環境,參試設備包括測試平臺、測試計算機(運行上位機控制臺軟件)、兩塊嵌入式被測設備。

某型高速嵌入式信息安全設備的測試項目較多,這里以業務加解密性能測試為例,介紹模擬測試環境的測試流程和結果分析。

2.1? 測試目的

驗證被測設備在高速業務數據持續輸入條件下加密和解密處理性能的可靠性。

2.2? 測試步驟

1)測試計算機、測試平臺上電啟動,打開上位機控制臺界面。

2)通過上位機控制臺界面配置測試工裝IP地址為192.168.1.211,端口號配置為3211,通信協議設置為UDP。

3)點擊上位機控制臺“發送復位指令”按鈕,向兩塊嵌入式被測設備發送復位指令,觀察上位機界面被測設備上報的自檢狀態;如果顯示“通過”表示被測設備狀態正常,進入下一步操作。否則被測設備狀態異常,需排查故障。

4)在上位機控制臺的發送控制區選擇“業務幀”,選擇加密方為被測設備1,解密方為被測設備2,設置發送幀數量為100 000幀,設置發送速率為300 Mbit/s,設置幀長度為1 024 Byte,明密設置為加密。點擊選擇發送樣本欄的“瀏覽”按鈕,在本地文件中選擇相應的明文測試樣本,然后點擊“發送幀”按鈕,觀察日志欄上報的打印信息,直至顯示“數據幀發送完成”,記錄統計區“發送幀計數”“接收幀計數”的顯示數據。

5)點擊上位機控制臺“明文比對指令”按鈕,觀察日志欄上報的打印信息,直至顯示“數據幀比對完成”,記錄“錯誤幀計數”顯示數據。

6)保持發送控制區的指令參數不變,按照步驟4)、步驟5)重復操作2次。

7)在上位機控制臺的發送控制區選擇加密方為被測設備2,選擇解密方為被測設備1,其他指令參數不變,按照步驟4)、步驟5)重復操作3次。

8)記錄測試結果信息,整理并保存明文和密文測試數據,測試平臺斷電。

2.3? 測試結果及數據分析

表1中測試數據統計顯示6次測試的發送幀計數與接收幀計數全部一致,均為100 000幀,錯誤幀計數均為0幀,測試過程沒有出現丟幀和錯幀現象,兩塊被測設備的業務加解密處理性能穩定可靠,測試達到了預期目標,同時證明了測試工裝的可行性和測試能力。

3? 結? 論

本文提出了一種基于FPGA的便攜式高速測試工裝設計,測試工裝包括上位機控制臺軟件和下位機測試平臺兩部分,上位機控制臺軟件完成測試樣本下發和測試數據儲存,并提供人機交互界面;下位機測試平臺以FPGA為核心處理單元,用以完成與上位機控制臺及被測設備的接口轉換和數據轉發。通過測試驗證發現:基于FPGA的便攜式高速測試工裝能夠搭建穩定可靠的模擬測試環境,滿足某型高速嵌入式信息安全設備的測試應用需求,測試工裝開發維護成本低,攜帶方便,具有很高的實用性。

參考文獻:

[1] 吳召平,侯云江,蘇航.基于嵌入式平臺的某型模塊測試工裝設計 [J].信息技術與信息化,2021(8):113-115.

[2] 李強,黎小軍,吳召平.基于嵌入式平臺的某型網絡設備測試工裝的研究與設計 [J].電子世界,2022(2):144-146.

[3] 唐良偉.多通道綜合化控制臺通用測試工裝的設計與實現 [J].電子質量,2020(3):14-17+23.

[4] 張德智,曾星星,劉建妥,等.基于VPX架構的測控通信綜合測試系統設計 [J].計算機測量與控制,2016,24(5):53-54+70.

[5] 胡榮芳.一種通用自動化測試設備的設計與實現 [J].流體測量與控制,2023,4(2):20-24.

[6] 劉宗瑞.高速嵌入式檢測技術研究 [D].北京:北京理工大學,2018.

[7] 韓林濤.衛星數據通信地面檢測設備的設計與實現 [D].西安:西北大學,2022.

[8] 秦友倫,袁強,劉峰,等.一種全國產化多接口便攜式測試設備 [J].兵工自動化,2023,42(2):42-45.

作者簡介:任敏(1989—),男,漢族,山西大同人,工程師,碩士研究生,主要研究方向:電子通信、信息安全等。

收稿日期:2023-05-06