基于改進YOLOv5的PCB裸板缺陷檢測

程 霖,張 濤,葛平淑,劉俊杰,向青陽

(大連民族大學 機電工程學院,遼寧 大連 116605 )

隨著中國現(xiàn)代電子產業(yè)和新興技術的迅猛發(fā)展,印刷電路板(PCB)作為各種電子元器件的載體,是各種電子產品布線連接和信號傳輸?shù)年P鍵硬件支撐,決定著電子產品是否能夠正常運行。但生產PCB電路板的工藝十分復雜,受到當前生產工藝技術限制,在PCB生產過程中容易產生如漏孔、鼠咬、開路、短路、雜散、雜銅等缺陷。這些缺陷PCB板一旦應用到電子產品中會導致產品運行故障或者損壞,造成較大經濟損失。因此對PCB裸板及時進行缺陷檢測有著重要的現(xiàn)實意義和經濟價值。

近些年隨著深度學習技術在缺陷檢測領域的不斷發(fā)展,與傳統(tǒng)的機器學習方法相比,深度學習的泛化能力更強,適合于更多復雜生產環(huán)境。如今已有研究人員將深度學習算法應用于PCB板的缺陷檢測中來。當前基于目標檢測主要分為兩種,Two-stage和One-stage檢測[1]。Two-stage檢測算法中經典的有(R-CNN、Faster R-CNN)等。2020年6月沈非堯等[2]對Faster R-CNN算法進行優(yōu)化,選擇ResNet-101進行作為特征提取網絡,并在RoI pooling層中結合RoI Align優(yōu)化算法,提高了訓練速度和精度。2021年6月耿振宇等[3]使用ResNet代替VGG作為Faster R-CNN的主干網絡,并引入特征金字塔網絡(FPN)來解決多尺度檢測問題,并減少了計算量One-stage檢測算法主要為YOLO系列算法,與Two-stage檢測算法相比優(yōu)點在于速度更快,但精度略低于Two-stage檢測算法。為了兼顧速度與精度問題,2021年6月,孫燦等[4]以YOLOv3為基礎模型,在模型參數(shù)計算量、注意力機制以及重疊目標檢測等方面進行優(yōu)化,提高了YOLO算法的性能。2022年6月李洋等[5]利用ECANet優(yōu)化有效特征層融合方式,并改進特征金字塔網絡結構,提高了YOLO算法對小目標缺陷的檢測精度。

針對PCB裸板缺陷檢測難度大的問題,提升高密度場景下PCB缺陷檢測精度,緩解梯度消失并降低模型訓練損失仍是現(xiàn)階段大部分算法需要解決的首要問題。本文針對YOLOv5算法進行優(yōu)化改進,改進主干特征提取網絡。引入密集連接卷積網絡DenseNet思想[6],搭建密集連接模塊,對Bottleneck模塊進行改進。緩解了消失梯度問題,鼓勵特征重用,加強特征傳播。提高YOLOv5算法針對PCB裸板小目標缺陷檢測的精度。

1 YOLOv5算法結構

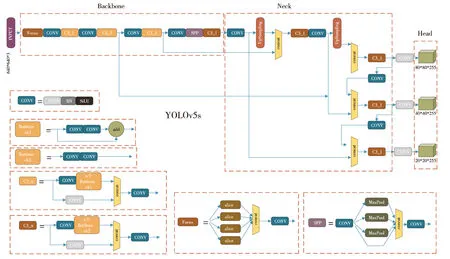

YOLO系列模型在目標檢測領域是性能較好的單階段目標檢測算法,2020年6月發(fā)布的YOLOv5是YOLO系列兼顧準確率和速度的模型。YOLOv5可以分為s、m、l、x四個版本,本文所用算法為YOLOv5s。YOLOv5網絡結構可以分為4個模塊:輸入端(Input)、主干網絡(Backbone)、頸部(Neck)和檢測網絡(Head)[7]。其結構如圖1。

圖1 YOLOv5結構

輸入端的作用就是進行圖像的預處理,將圖片縮放為網絡輸入大小、數(shù)據歸一化和數(shù)據增強。YOLOv5采用masaic增強技術把四張圖片的部分進行拼接隨機組成一張新的尺寸固定的輸入圖片。而YOLOv5與以往不同的是作者對其進行了改進,變?yōu)榱俗赃m應圖片縮放,之前的YOLO算法都是將不規(guī)則圖片進行填充,產生新的固定的正方形圖片,該方法所生產的新圖片有較多的黑色邊框,由此會造成信息冗余,從而產生不必要的計算量,進而影響算法的推理速度。YOLOv5算法因此改進了圖片縮放方式,采用了自適應的填充,由此對原始圖片添加最少的黑邊框。大大減少了算法推理計算量。主干網絡Backbone模塊則借鑒了跨階段局部網絡CSPNet(Cross Stage Partial Network)的設計思想[8],使用CSPdarknet為主干網絡,減少了模型整體計算量。其中在YOLOv5第一次使用了Focus結構。C3模塊是對殘差特征學習的主要模塊,主要作用是增加網絡深度,提高特征提取能力。C3由兩種不同的bottleneck結構和標準的卷積模塊組成,組成兩種不同的C3模塊。空間金字塔模塊SSP的主要思想為對輸入的特征圖進行卷積核大小不同的池化操作,得到不同大小的特征圖,最后進行拼接得到統(tǒng)一尺寸的特征圖[9]。頸部(Neck)網絡設計沿用了FPN+PAN的結構[10]。FPN結構通過自頂向下進行上采樣,構建出多尺度高級語義特征圖[11]。PAN結構則是自底向上進行下采樣,加入了自底向上的路線,彌補并加強了定位信息。

2 改進的YOLOv5算法結構

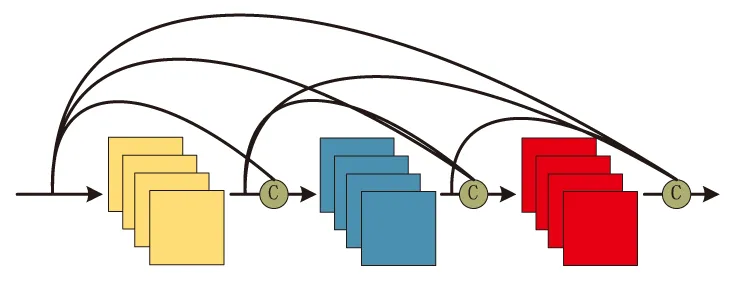

PCB缺陷檢測多為小目標檢測,需要對YOLOv5算法進行改進,而對于小目標檢測的難點在網絡的加深過程中,會出現(xiàn)圖像信息丟失的現(xiàn)象。在網絡加深的過程中,提取出的特征也由淺變深,淺層特征即具體的位置信息,深層特征即抽象的語義信息。隨著網絡加深,小目標在特征圖中所占據的像素會越來越少,使目標檢測的結果不理想。為了更加充分利用各個卷積層所提取出來的特征信息,本文在YOLOv5算法中引入密集連接卷積網絡(DenseNet)的思想,DenseNet網絡具體結構如圖2。

圖2 DenseNet密集連接網絡

在DenseNet網絡中,每兩層之間都直接相連,每層都可以獲得前面所有層的特征輸入,對于網絡L層輸出,傳統(tǒng)網絡的輸出與DenseNet網絡輸出如公式(1)、(2)所示:

xL=HL(xL-1);

(1)

(2)

從上述公式中可以看出,引入密集連接思想,可以實現(xiàn)特征重用。每一層只需學習很少的特征,不需要重復學習冗余的特征圖,通過更少的參數(shù)量就使得卷積層學習到更多的特征,相比于傳統(tǒng)的卷積網絡,這種結構的特征利用效率更高,使得網絡可以更加高效的學習新的信息。

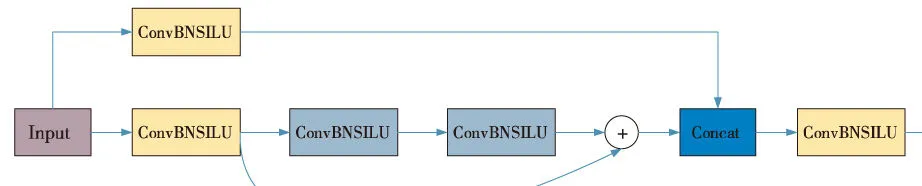

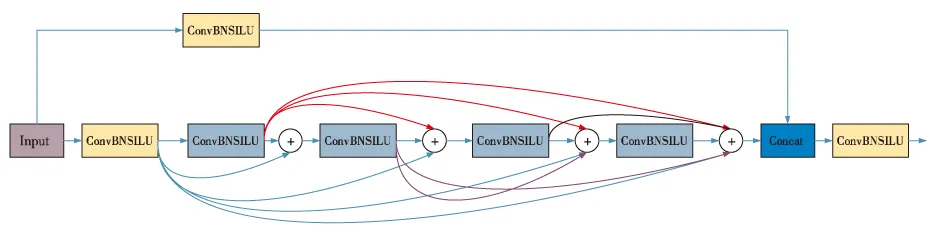

對YOLOv5中的主干特征提取網絡進行改進,在主干網絡的Bottleneck中添加兩個新的卷積塊,同時使得每層都可以獲得前面所有層的特征信息,這使得層之間的連接更緊密。密集卷積網絡精度提高的原因是各個層通過更短的連接從損失函數(shù)中獲得額外的監(jiān)督。可以將 DenseNet 解釋為執(zhí)行一種“深度監(jiān)督”。好處是它的每個隱藏層都有分類器,強制中間層學習判別特征。DenseNet以隱式方式執(zhí)行類似的深度監(jiān)督,DenseNet 的損失函數(shù)和梯度要簡單得多,因為所有層之間共享相同的損失函數(shù)。因此DenseNet網絡可以減少梯度消失,增強特征傳播,提高YOLOv5算法中的特征信息重用,使其更加適合PCB裸板缺陷的小目標檢測。具體改進結構如圖3~4。

圖3 原C3模塊

圖4 改進C3模塊

通過上述對YOLOv5算法中的主干特征提取模塊改進,相比于原來層與層之間的連接更加激進,模塊中大量使用了殘差分支,每一層都在接受前幾層的特征信息,并將自己的特征信息傳遞給后續(xù)的所有層,以提高算法的檢測精度。

3 實驗與驗證

3.1 實驗環(huán)境

軟件環(huán)境使用Windows 11 專業(yè)工作站版,PyTorch深度學習框架。硬件配置上為CPU:AMD Ryzen 9 5900X 12-Core Processor 3.70 GHz;GPU:NVIDIA RTX A4000 16G顯存。

3.2 數(shù)據集簡介

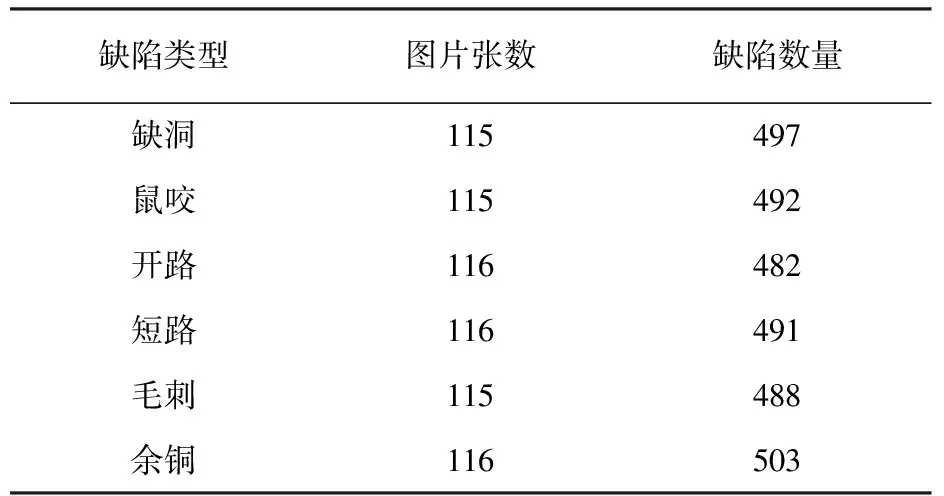

采用公開數(shù)據集PKU-Market-PCB,該數(shù)據集一共包含692張印刷電路板缺陷圖片,并附有對應的標注文件。包含了工業(yè)生產中常見的6種缺陷類型。圖片的張數(shù)和缺陷數(shù)量見表1。

表1 缺陷圖片數(shù)量及各缺陷數(shù)量

3.3 數(shù)據集增強

由于公開數(shù)據集PKU-Market-PCB只有692張缺陷圖片,由于數(shù)據量有限,很可能會因數(shù)據量較少而導致訓練結果過擬合,因此需要對原始數(shù)據進行擴增,本文采用的方法是通過旋轉、鏡像、增亮、加噪聲等隨機增強的方法進行擴增。最終得到數(shù)據6 920張。

3.4 評價指標

在評價算法的性能時,本文采用平均精度(mean Averrage Precision,mAP)、召回率(Recall)、F1得分(F)、精確率(Precision)、作為評價指標。

根據PCB測試樣本的真實類別與模型預測類別劃分為真正例(TP)、假正例(FP),真反例(TN),假反例(FN)。

精確率又叫做查準率,是指分類過程中模型預測的所有正例中預測正確的比例。召回率又叫查全率,是指模型預測正確的正例占據真實正例的比例,它們具體計算公式如(3)、(4)所示:

(3)

(4)

準確率和召回率是兩個矛盾的衡量標準,在準確率高時,召回率則會較低;而當召回率較高時,準確率則會較低[12]。綜合兩者,繪制P-R曲線,縱坐標為精確度的值數(shù),橫坐標為召回率的值數(shù),獲取值數(shù)后做出曲線圖,根據曲線面積與坐標軸圍成的面積即可得到平均精度AP(Averrage Precision),該面積越大則反映出算法的性能越好。在最后檢測結果中,每一個類別都會有一個AP曲線,所有的AP曲線收集起來,得到mAP即為均值平均精度。兩者計算公式如(5)、(6)所示:

(5)

(6)

3.5 算法訓練與實驗

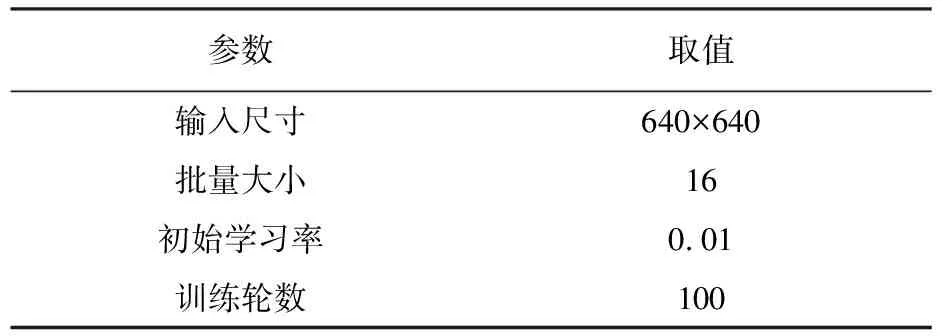

文中將訓練集、驗證集與測試集按照8:1:1的比例進行劃分。訓練的具體參數(shù)設置見表2。

表2 訓練的參數(shù)設計

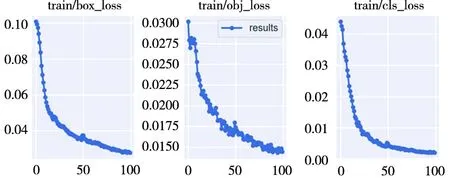

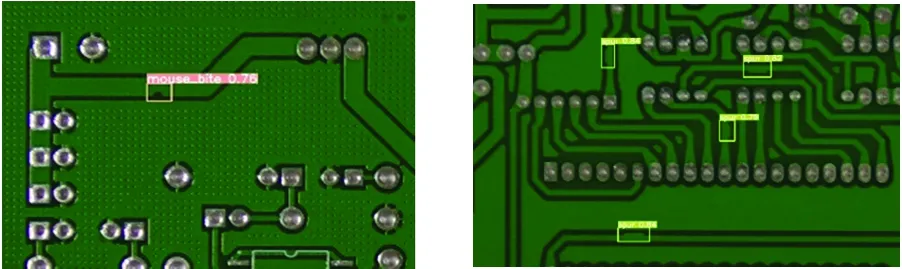

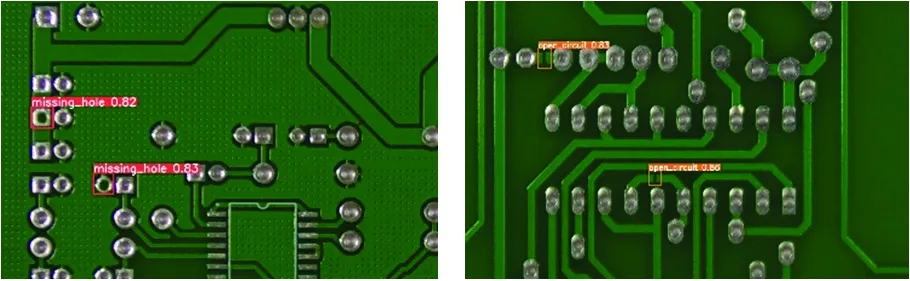

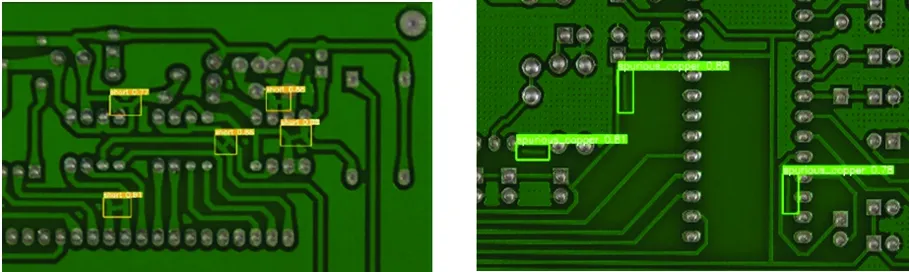

改進的YOLOv5算法訓練期間的損失曲線如圖5。觀察可知隨著訓練輪數(shù)的增加,損失曲線的斜率逐漸趨于平緩,圖5a代表訓練集位置損失;圖5b代表訓練集置信度損失;圖5c代表訓練集類別損失。由圖5可知訓練效果達到了較好擬合狀態(tài),證明該算法已經收斂,最終的實驗結果如圖6。改進后的算法對PCB裸板缺陷的識別平均精度為95.6%,其中對于漏孔缺陷的檢測精度最高,達到了99.5%。該算法檢測效果符合需求,準確檢測出各類缺陷如圖7~12。

a) box_loss圖 b) obj_loss圖 c)cls_loss圖圖5 損失曲線

圖6 P-R曲線圖

圖7 mouse bite 缺陷檢測 圖8 spur缺陷檢測

圖11 missing hole 缺陷檢測 圖12 open circuit 缺陷檢測

圖9 short 缺陷檢測 圖10 spurious copper 缺陷檢測

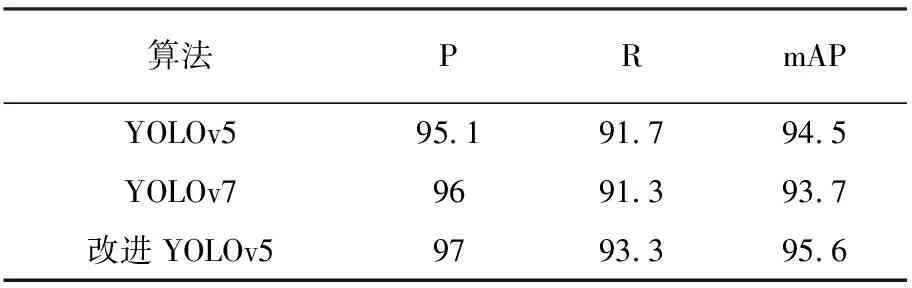

為了檢驗本文算法改進的有效性,在同一數(shù)據集中,對改進YOLOv5算法(YOLOv5+denseNet模型),原YOLOv5算法、YOLOv7算法進行對比實驗,所得到的性能參數(shù)見表3。

表3 改進后算法與YOLOv5、YOLOv7算法精度比較 %

由表3可知,改動后的算法相比較于原算法,平均精度提高了1.1%,平均精度提高了1.9%,召回率提高了1.6%。說明對YOLOv5算法中主干特征提取模塊引入密集連接思想,加強特征信息傳遞后有效地提高了算法性能,證明了改進YOLOv5算法在PCB裸板等目標檢測方面擁有較好的適用性,其性能優(yōu)于其他算法。

4 結 語

針對目前檢測算法對小目標缺陷檢測效果不理想的情況,對YOLOv5算法進行改進,提出了一種針對PCB裸板缺陷檢測的改進YOLOv5算法,主要是對YOLOv5算法的主干特征提取網絡進行改進。與原算法相比,在同一數(shù)據集中的平均精度得到了提高。值得注意的是不同數(shù)據集預處理方式會影響模型精度,因此后續(xù)將進一步提高改進模型的泛化性,同時拓展應用在其他目標尺寸較小的應用場景中。