基于邏輯門的新型多主訪問RS485總線方案*

林云策,朱浩然,包志舟

(1.溫州大學電氣與電子工程學院,浙江 溫州 325035;2.溫州大學樂清工業研究院,浙江 溫州 325035;3.浙江人民電器有限公司,浙江 溫州 325035)

0 引言

RS-485總線具有接口芯片豐富、硬件成本低、操作方便、低速傳輸時傳輸距離遠等特點[1-2],被廣泛應用于電鍍電源、實驗室電源管理、電力終端設備管理等領域[3-4]。傳統的RS-485 總線應用多為基于Modbus 協議的一主多從(一個主節點,多個從節點)通信方式,采用主節點輪詢從節點的方式進行通信[5-7],優點是通信方式簡單。但一主多從通信模式只適合規模不大或對通信實時性要求不高的場景。隨著從機節點數的增加,主節點輪詢從節點的時間會變長[8-9]。因此。為了提高通信實時性,拓寬RS-485總線的應用,多主訪問RS485通信方式被提出[10]。多主訪問RS485 通信方式是利用主節點可以主動發起通信的特點,取消了輪詢機制,采用通信節點主動變為主節點進行主從通信的方式,大大提高了通信的實時性。但是因為只有一條總線,當多個主節點發起通信時,在總線上會發生通信擁堵,如何解決總線上的通信擁堵是實現多主訪問RS485總線技術的關鍵[11]。

文獻[12]提出將RS-485 總線接收器的輸出端反相后接到CPU 的外部中斷管腳,用觸發中斷的方式判斷總線上是否有數據傳輸,同時結合定時器中斷判斷總線是否空閑。但需要軟件定時器的配合,且對并發節點的處理只是簡單采取隨機延時后重發,總線利用率不高。文獻[13]提出利用硬件電路實現,具體的電路由兩個對稱RS485 總線接收器構成,需要進行合適的阻抗匹配,兩個接收器的輸出相與后得到總線狀態信號。該方案電路復雜,容易引入故障點,且帶載能力較弱,不能超過16個節點。文獻[14]提出利用74HC123 單穩態觸發器形成總線狀態標志,判定當前總線是否為忙。該方案單穩態時間設計比較依賴固定的通信波特率,缺乏對并發主節點的有效的處理方式,導致總線利用效率仍然不高。文獻[15]提出利用定時器進行總線偵聽,再對總線進行改造,使之具備邏輯“與”功能,配合具有優先級的數據幀解決多節點并發問題。該方案相對優秀,總線利用率較高但需要用到定時器資源。文獻[16]提出一種令牌環機制,主節點按一定順序進行通信,需要緊急通信的主節點在一定搶發時間內爭搶總線,并發的主節點,按不同優先級重復發送數據,競爭總線。該方案適合規模小、數據量小的場合。

以上各方案都可以基本實現多主訪問的功能,但是都有各自的局限性,針對不同的場合都有各自的用處。針對現有的方案,本文提出了一種不占用軟件資源、帶載能力強、總線利用高的新型的可支持多主訪問的RS-485總線技術方案。

1 整體設計方案

1.1 多主訪問RS485存在的技術問題

多主多從模式設有多個主節點,隨機發起通信的多個主節點容易在總線上出現通信擁擠。為了避免這種情況,主節點的主動通信需要合理規劃,有效化解沖突。為此,節點需要滿足兩點要求。第一,主節點只有在檢測到總線空閑的時候,才有權限向總線發送數據,進行有效通信。第二,偵聽總線空閑雖然避免了主節點在總線忙時發送數據。但無法避免同時檢測總線空閑的主節點一起搶占總線,造成通信混亂。因此需要對多個并發的主節點進行仲裁,選中唯一可通信節點。

針對第一點,需要設計出偵聽總線空閑機制,通知主節點具備發送條件。針對第二點,需要設計出并發沖突節點競爭機制。

對偵聽總線空閑機制的設計,是抓主總線空閑的特征,即總線空閑時,總線信號不變;總線繁忙時,總線信號是變化的。因此可以根據這一特點,利用不同的技術手段和資源,根據需求設計總線空閑偵聽機制。

多個并發主節點在總線發生沖突時,會造成總線電平的不可預測混亂,導致節點接收的數據與發送端不一致。是否對發生沖突的總線規律化處理,沖突節點以何種方式再次發送是并發沖突節點競爭機制設計的關鍵問題。本文將偵聽總線空閑機制和并發沖突節點競爭機制合稱為沖突檢測機制。

1.2 多主訪問RS485總線設計方案

工程技術方案的設計除了解決功能性要求外,還需要考慮軟硬件資源配置的問題。本文針對偵聽總線空閑機制和并發沖突節點競爭機制的關鍵問題,在只添加少量硬件資源,不占用軟件定時器資源的條件下,提出了可靠性高的沖突檢測硬件電路,再配合特定的發送數據格式,實現可支持多主訪問的RS-485總線通信方式。

2 多主訪問RS485硬件電路設計

2.1 RS-485接口介紹

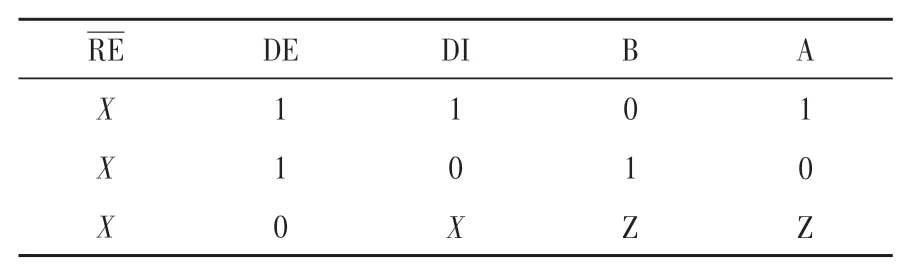

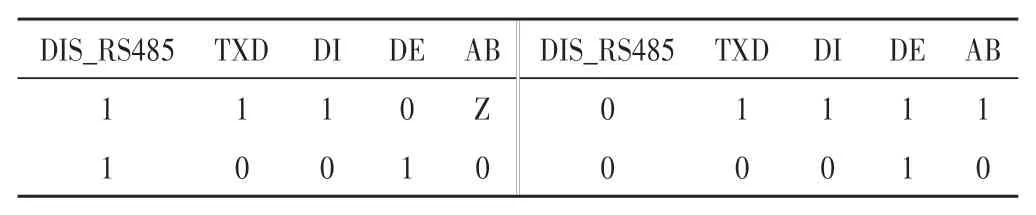

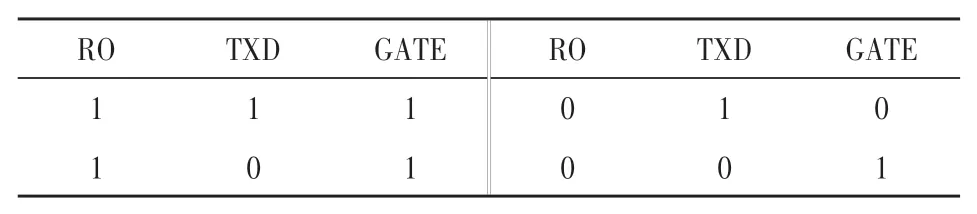

常用485接口芯片的接口如圖1所示。該芯片可以將實現USRT 串口電平格式和RS485 總線的電平格式相互轉化。該芯片一共有8 個引腳其分別為接收數據輸出腳RO、接收控制腳RE、發送控制腳DE、發送數據輸入腳DI、接受數據輸出腳和一對總線接口引腳A、B 所構成[17]。RS485 采用差分傳輸即通過AB 間的電壓差確定。發送控制腳DE 為低電平時,A、B 口為高阻態;發送控制腳DE 高電平時,使能發送控制腳,令A、B 解除高阻態。對于接受數據控制腳也同理,不過控制邏輯相反。RS-485引腳詳細的功能真值表1所示。

表1 輸出真值表

圖1 RS-485接口

2.2 沖突檢測電路

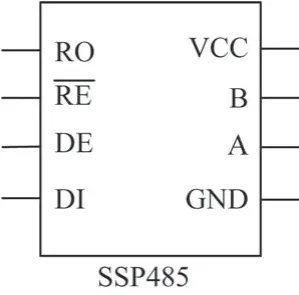

本文是利用485 芯片的AB 口高阻態特點,并配合少量的邏輯門電路,實現沖突檢測硬件電路,其結構圖如圖2所示。對485接口芯片的數據接收控制腳位一直使能。

圖2 沖突檢測電路結構

沖突檢測硬件電路的左邊接MUC,RS-485 為控制信號,TXD 為串口輸出,GATE 為沖突檢測信號。該沖突檢測的電路的原理是在當總線發生沖突時,GATE 會出現低電平;當總線空閑時,GATE會出現高電平。

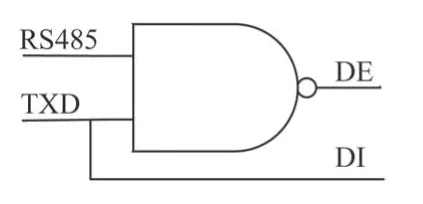

輸入環節是由1個與非門構成,如圖3所示。與非門的兩個輸入分別是RS485 控制信號和串口輸出TXD,與非門的輸出連接485 芯片的數據發送控制腳。串口輸出TXD 和485 接口芯片的數據發送腳DI 直連。輸入環節功能真值表如表2 所示。由表可知,輸入環節的特點是當DIS_RS485 信號為邏輯“0”時實現485 通信;當DIS_RS485 信號為邏輯“1”時可以令串口輸出的邏輯“1”,不是通過485 芯片的邏輯電平“1”的輸出,而是通過A、B 總線上的電阻來實現邏輯“1”的輸出。而當有節點出現邏輯“0”時總線電平被拉低,變成邏輯“0”。這種輸出方式可以保證總線上多個節點通信,不會破壞總線電平標準,有很強的帶載能力,且可以據此對節點進行優先級設置。

表2 輸入環節功能真值表

圖3 輸入環節電路

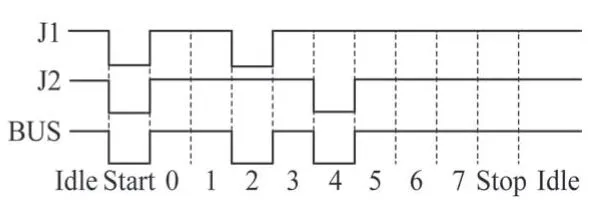

當總線上有兩個節點J1、J2 分別輸出USRT 串口格式字節0xFC 和0xEF 時,總線上收到的是0xEC。如圖4所示。

圖4 多節點總線沖突情況

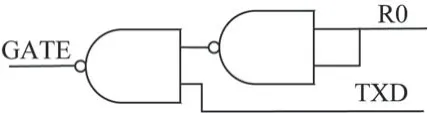

輸出環節是由1 個非門和1 個與非門組成,輸出環節的電路如圖5所示。

圖5 輸出環節電路

輸出環節的輸入是串口輸出TXD 和485 接收數據輸出腳RO。輸出環節的作用是利用總線數據和節點自身的輸出判定總線是否忙,功能真值如表3 所示。由表可以看出輸出環節的功能是類同或門。因為輸入環節的存在中,在本電路中第二種情況不會發生。當本節點收發邏輯電平不一致,即GATE為邏輯0時,說明當前總線不空閑(僅識別GATE為1,不能說明總線空閑)。利用GATE電平的變化的規律,MUC 通過一定的軟件手段,可以判定總線是否為忙。

表3 輸出環節功能真值表

沖突檢測電路對傳統的485 總線和控制機制進行了改造。將傳統485 通信的邏輯“1”的電平輸出,改為高阻態偏置電壓輸出,實現了總線沖突時高電平保持,出現低電平拉低的規律化特征,并實現節點輸出數據和總線數據的硬件比較。

2.3 工作機制

MUC 對沖突檢測電路的GATE 口進行檢測,只檢測到邏輯電平“1”時,授予節點通信權限;一旦檢測到邏輯電平“0”,該節點需要重新申請通信權限。

MUC 的一個外部中斷口接GATE 口,采用下降沿觸發或低電平觸發中斷,通過中斷對節點進行授權。

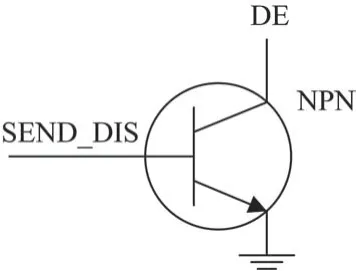

為了更好地偵聽總線是否空閑,且不影響總線通信,在發送數據引腳上額外增加上1 個發送控制電路如圖6 所示。利用1 個NPN 三極管,控制485 芯片的數據輸出控制腳,在偵聽總線時,SEND_DIS輸出高電平,拉低發送數據控制腳DE的電平,防止查詢總線幀對總線的影響。查詢總線幀是節點串口以總線485通信最低波特率的一半的查詢字節0xFF。因為串口發送字節時,存在一個低電平的起始位,所以查詢總線幀可以優先檢測出,總線上是否有通信發生。若在發送查詢數據幀期間,GATE口出現低電平則說明系統忙,否則總線空閑。當總線上在兩個字節波特率時間內沒有字節發送時,說明不存在有效通信,所以可以認定總線空閑。

圖6 發送控制電路

獲得發送權限的主節點按485 通信波特率發送優先級數據幀,GATE 腳出現低電平的主機退出競爭,繼續進行偵聽總線,申請發送權限。同時發起通信的主節點按優先級獲得發送權限。

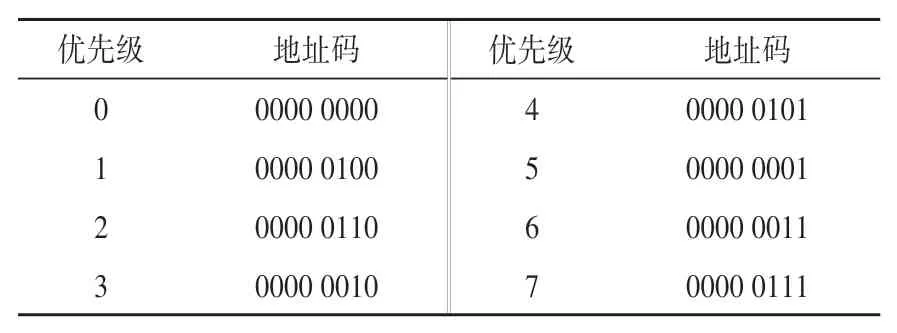

優先級和二進碼的換算關系如式(1)所示。

式中:n為優先級數;j為參與計算的bit-1 位數;i為先發送比特位數(i=0,1,2,…,j),數字越小越早發送;ai為對應比特位上的取值。

一個字節的高位5 位取相同位數,只計算低3 位比特位,按右邊為低位先發設計的優先級數據幀的形式如表4所示。

表4 計算3個比特位的地址碼

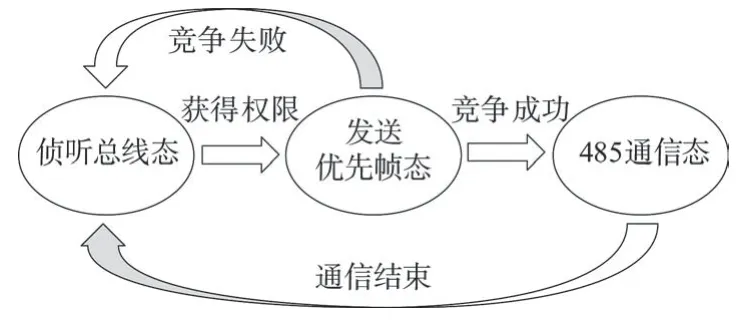

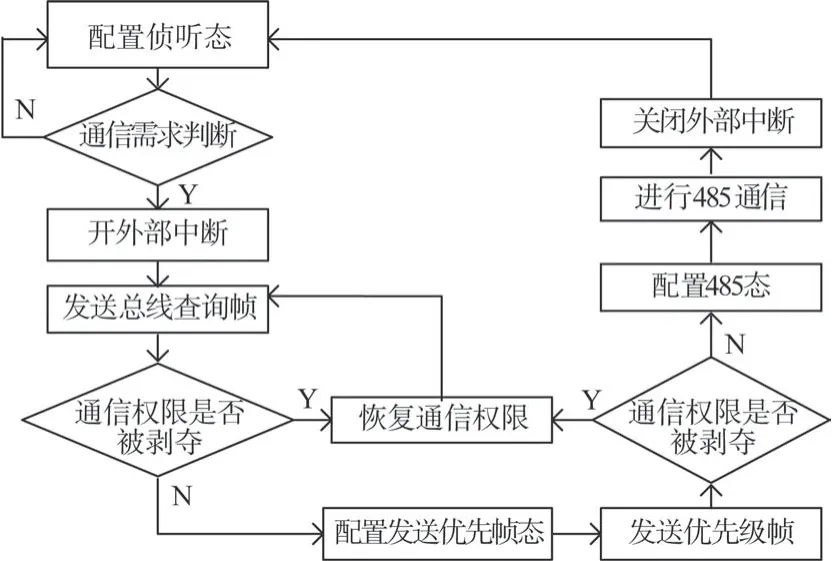

每個節點的狀態都是在偵聽總線態,發送優先幀態,485態之間相互轉換。狀態轉化如圖7所示。

圖7 節點狀態轉化

本機制不需要用到定時器資源,硬件實現沖突檢測。

3 多主訪問485軟件設計

3.1 主控芯片要求

本本設計方案對主控芯片的要求偏向IO 口資源,而不占用定時器資源。這對一些對定時器資源有要求的節點事務,且主控定時器資源少的主控有明顯的優勢。例如像51 單片機這種低成本、定時器資源少的主控,一旦存在定時查詢事務,定時器資源緊張的情況下,采用本方案就可以明顯緩解緊張資源。這為工程上提供了一種新的方案選擇。

3.2 通信狀態轉化程序設計

對總線偵聽程序的設計重點是在總線空閑判斷和狀態轉換。總線空閑判斷要和各個狀態轉換相匹配。狀態轉換主要是沖突檢測電路進行功能配置和必要的數據幀配合。

節點的起始狀態為偵聽總線態,默認具有通信權限。當節點有通信需求時,才會發送查詢總線幀。一般先配置沖突檢測電路功能令SEND_DIS=1,DIS_RS485=1,再開啟外部中斷,然后配置串口發送查詢總線幀。外部中斷的優先級必須高于串口中斷的優先級。在外部中斷函數中,對節點進行授權剝奪。在發送完查詢總線幀后且通信權限未被剝奪,節點進入發送優先幀態。

進入發送優先幀態的節點,也是先配置沖突檢測電路功能,令SEND_DIS=0,DIS_RS485=1。然后發送優先級幀,發送完成后,再查詢節點通信權限。如果仍然具有發送權限,則進入485 通信態,否則退回總線幀聽態,并恢復其通信權限,進行新一輪的總線查詢。

進入485 通信態的節點,配置相應的沖突檢測電路功能即令SEND_DIS=0,DIS_RS485=0。進行485 通信,通信結束后可以關閉通信或者總線偵聽態,等待下一次通信需求的發起。程序設計的流程如圖8所示。

圖8 程序設計流程

4 實驗驗證和結果分析

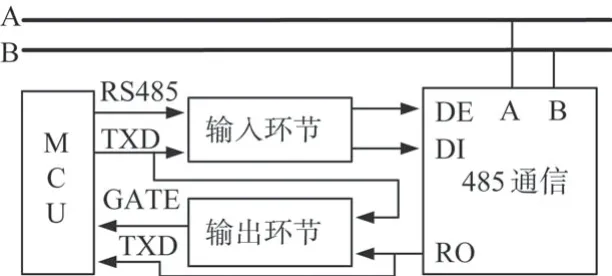

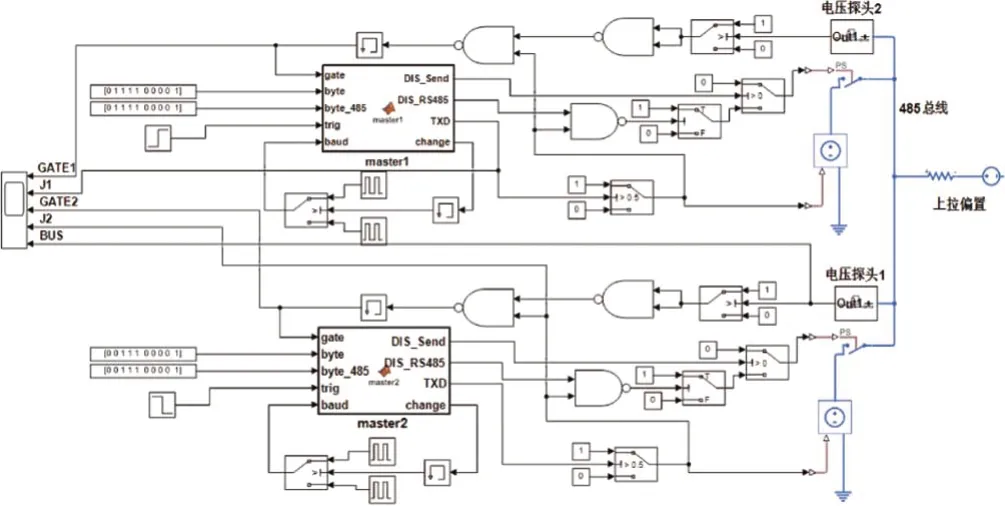

本文通過MATLAB Simulink 平臺對方案進行邏輯驗證了。實驗平臺對485總線AB 總線進行了合理簡化,一個節點的電位模擬總線信號,具體接法見圖9。用1個受控的開關模擬高阻態,開關的控制腳模擬485 芯片數據發送控制腳DE,開關斷開為高阻態,開關閉合總線電平由受控電壓源決定,即正常485通信。沖突檢測電路的3個與非門用了自帶的模型。節點的主控master 的控制邏輯用MATLAB FUNCTION 函數進行模擬。Change 引腳為波特率切換信號。兩個方波的頻率模擬波特率,輸入master 模塊的baud 腳。Trig 腳模擬數據發送請求,高電平為請求數據發送,低電平無請求。Byte 腳輸入優先級地址幀。Byte_485 模擬后續通信數據。其他腳和上文描述的意義相同。

圖9 多主訪問485總線方案

通過上述平臺以兩個主節點為例模擬本方案多節點錯時通信、多節點并發通信工況。

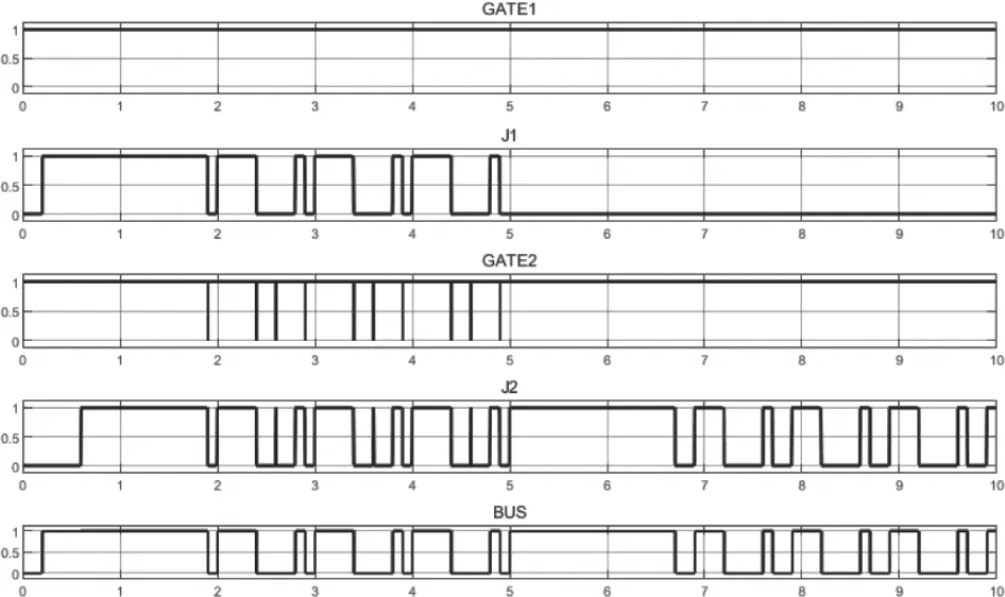

偵聽總線空閑通的模擬情況如圖10所示。由圖10可知當節點J1 正在通信的時候,節點J2 發送了總線查詢幀,當其遇到了J1通信過程中的低電平時,J2的GATE2腳迅速被拉低,并且重新發送總線查詢幀,并重復上述過程。一直到節點J1 完成通信后,節點J2 檢測總線空閑,才進入正常的通信。

圖10 多節點錯時通信

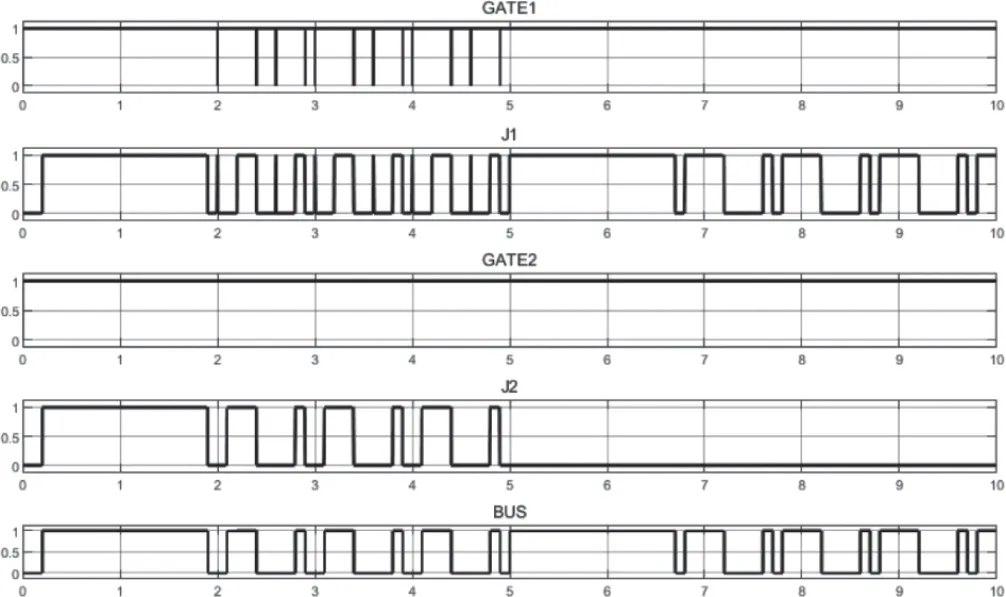

由圖11 可知節點J1 和節點J2 同時發起通信要求,同時監聽到總線空閑,并發進入發送優先幀態。由于節點J2的優先級比J1高,節點J1首先發送的電平為高電平遇到節點J2 發送的低電平后,GATE1 電平被迅速拉低,節點J1 退出競爭,進入總線偵聽態,而節點J2 競爭成功,繼續通信。直到節點J2通信結束后,節點J1檢測到總線空閑,并獲得總線通信權,開始正常通信。

圖11 多節點并發通信

從仿真結果可以看出當存在節點發起通信請求兩個通信字節時間后,必定有節點進行有效通信,體現了本方案總線高利用率和穩定性。

5 結束語

本文對多主訪問的RS-485總線技術進行了研究,針對總線空閑偵聽機制和多節點并發競爭機制兩個問題,提出了基于邏輯門的沖突檢測電路和相應的軟件算法,并在MATLAB Simulink 搭建了方案模型,并進行不同工況的仿真。仿真結果證明了本方案的可行性。此外,本方案還具備以下優點。

(1)在不采用定時器資源下,具備有高效的總線空閑偵聽機制,支持大規模節點的優點,為定時器資源少的主控芯片,提供了新的多主訪問RS485總線技術方案。

(2)在節點發送數據過程中就自動完成了總線競爭而不被打斷,無需強化沖突,浪費總線資源,大大提高了總線利用率。

本文為擴展RS-485多主訪問總線技術的應用做出了一定的貢獻。