重離子輻照引發的25 nm NAND Flash存儲器數據位翻轉

盛江坤,許 鵬,邱孟通,丁李利,羅尹虹,姚志斌,張鳳祁,緱石龍,王祖軍

(1.西安高技術研究所,陜西 西安 710025;2.強輻射脈沖環境模擬與效應全國重點實驗室 西北核技術研究所,陜西 西安 710024)

NAND Flash存儲器有著巨大的產量和市場占有率,在筆記本電腦、智能手機、平板電腦等領域應用廣泛。由于具有訪問速度快、成本低、存儲密度大、功耗小、重量輕等特點,NAND Flash存儲器非常適合用作衛星系統大數據量存儲設備。然而研究[1-2]表明,NAND Flash存儲器對輻射環境敏感,給衛星系統可靠運行造成了風險。其中,重離子入射對NAND Flash存儲器的影響備受關注。早期的NAND Flash存儲器對重離子入射最為敏感的電路是外圍電路,而浮柵存儲單元由于尺寸較大,即便因為重離子入射發生了電荷損失[3],也未產生較為嚴重的位翻轉。1999年,Nguyen等[4]發現重離子入射導致三星公司的128Mb NAND Flash存儲器出現功能中斷和由寄存器翻轉引發的讀出錯誤,但是未檢測到發生在浮柵存儲單元的位翻轉。隨著浮柵存儲單元特征尺寸不斷縮小,浮柵電荷數量不斷減少,位翻轉變得更為嚴重。2006年,Guertin等[5]發現當入射離子LET大于37 (MeV·cm2)/mg時,浮柵電荷損失導致的位翻轉隨注量累積呈現線性變化,類似于單粒子效應,而入射離子LET小于37 (MeV·cm2)/mg時,位翻轉表現為劑量效應。近年來,類單粒子效應的LET閾值已小于1 (MeV·cm2)/mg,甚至低能質子直接電離已足以引起存儲單元發生翻轉[6-7],因此NAND Flash存儲器重離子輻射效應研究一般遵循單粒子效應的研究方法和研究標準,主要關注入射離子特性[8-9]、入射角度[10]、器件工藝尺寸[11-12]以及退火時間[13-15]等因素對位翻轉的影響。

一般認為單粒子位翻轉截面與注量無關,因此在注量對NAND Flash存儲器位翻轉的影響方面,當前關注較少[16]。另外,對于重離子入射造成的多單元翻轉(multiple-cell upsets, MCU),當前研究更多關注多單元翻轉比率及其影響因素,對于多單元翻轉的拓撲結構報道較少[9],而拓撲結構信息能夠更為直觀地反映NAND Flash存儲器多單元翻轉的特征及其物理機制。為此,本文以兩款單層級(single level cell, SLC)NAND Flash存儲器為載體開展重離子實驗研究,重點關注不同注量下由浮柵電荷損失導致的位翻轉特點及其翻轉截面的變化,以及多單元翻轉拓撲結構特征。

1 實驗

1.1 待測器件

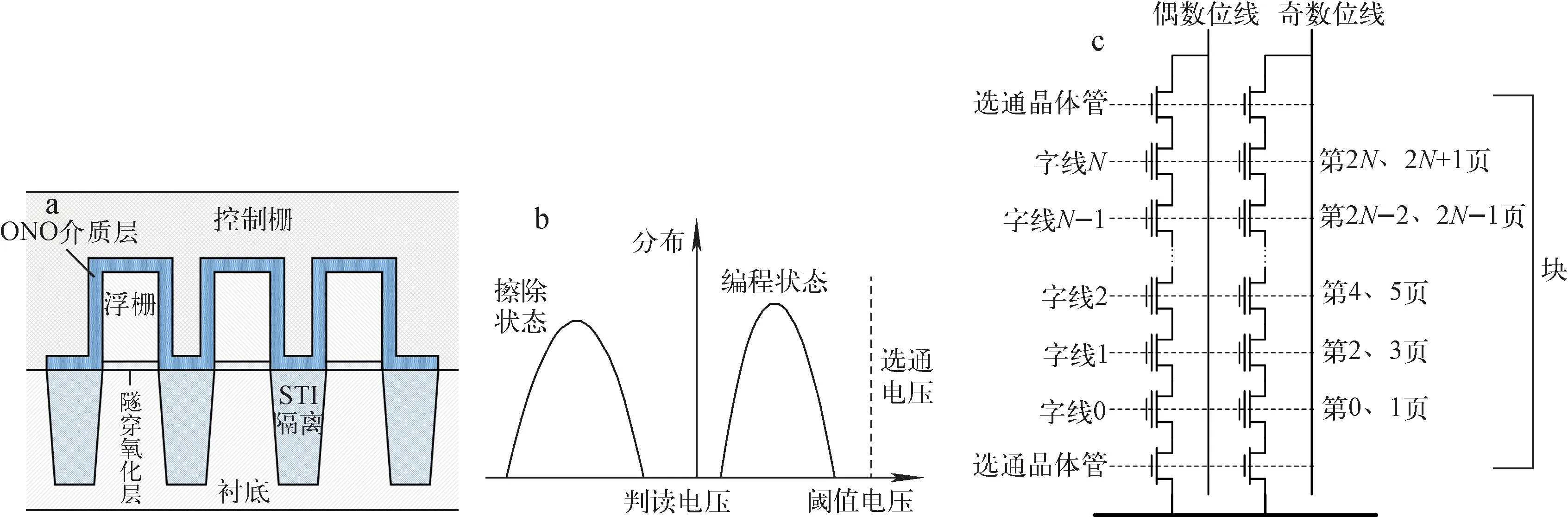

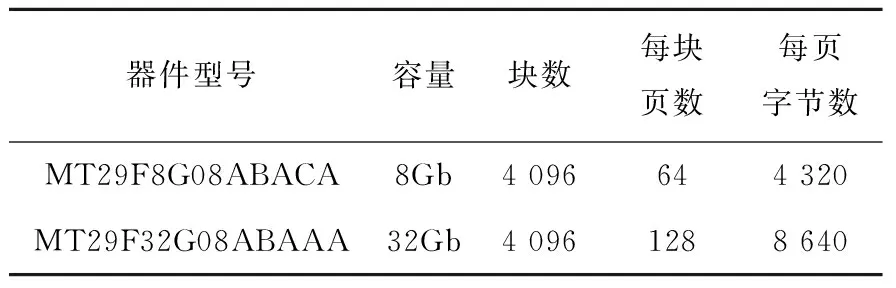

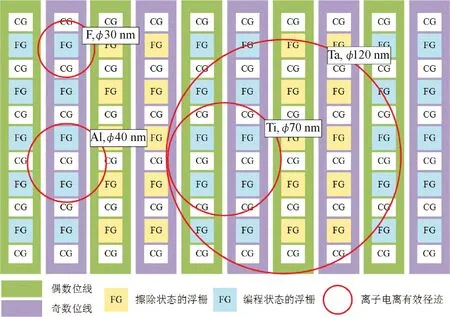

實驗選取的兩種SLC NAND Flash存儲器容量分別為8Gb和32Gb,特征尺寸均為25 nm,供電電壓為3.3 V。器件詳細參數列于表1。NAND Flash存儲單元是浮柵MOS晶體管,其結構如圖1a所示,浮柵和襯底之間是隧穿氧化層,浮柵和控制柵之間是由二氧化硅和氮化硅組成的介質層。存儲陣列中,多個浮柵存儲單元直接串聯形成NAND結構。存儲陣列閾值電壓分布如圖1b所示,存儲單元邏輯值是由其閾值電壓所處的電壓窗口決定的。對存儲單元進行編程操作后,浮柵中存在過量的電子,存儲單元閾值電壓升高,存儲數據0;執行擦除操作后,浮柵上電子減少,存儲單元閾值電壓降低,存儲數據1。在被訪問的存儲單元上施加判讀電壓,并在同一串聯結構的其他存儲單元和晶體管上施加選通電壓,通過串聯結構的導通狀態來判斷存儲單元的邏輯值。為避免讀出干擾,存儲陣列通常設計為位線交錯結構,即相鄰偶數頁和奇數頁的存儲單元交錯排布在一條位線上,如圖1c所示。

a——存儲單元;b——閾值電壓分布;c——存儲陣列位線交錯設計圖1 存儲陣列Fig.1 Memory array

表1 實驗器件參數Table 1 Device parameter used in experiment

1.2 實驗方案

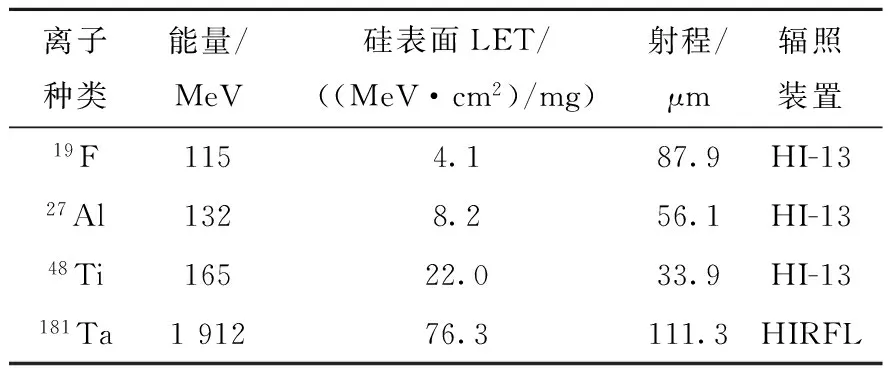

輻照實驗在中國原子能科學研究院HI-13串列加速器和中國科學院近代物理研究所蘭州重離子加速器HIRFL上開展。室溫條件下,以垂直入射方式,采用4種重離子對NAND Flash存儲器進行輻照,重離子詳細信息列于表2。

表2 重離子信息Table 2 Heavy ions used in experiment

輻照前向被試器件寫入數據55 h,輻照過程中被試器件不加電。每累積一定注量時,停止束流輸出,為被試器件施加3.3 V電壓后,進行位翻轉原位測試,記錄翻轉位地址。測試結束后器件斷電并繼續輻照。兩款器件各隨機選取2只進行Ta離子輻照,總注量為4×106cm-2。對于Ti、Al、F離子,每種離子、每種型號各選取4只器件進行輻照,總注量均為1×107cm-2。原位測試由西北核技術研究所開發的R-ictus-Ⅱ型測試系統完成,如圖2所示。

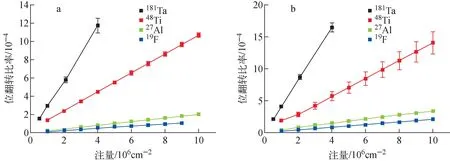

a——MT29F8G08ABACA;b——MT29F32G08ABAAA圖3 0到1的位翻轉比率隨注量的變化關系Fig.3 Bit upset ratio from “0” to “1” as a function of cumulative fluence

2 實驗結果與分析

2.1 重離子輻照導致的位翻轉

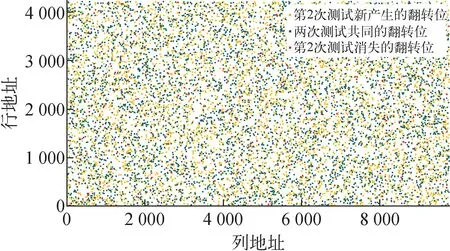

輻照過程中僅檢測到0到1的位翻轉,未檢測到1到0的位翻轉。位翻轉比率與注量基本呈線性關系,如圖3所示。位翻轉具有隨機性、繼承性、少量短時退火以及可再次編程等特點。翻轉位在地址上呈隨機分布,前一次檢測到的翻轉位絕大部分可在當次測試中檢測到,僅少量翻轉位消失。翻轉位仍能通過擦除和編程操作再次存儲數據1或0。圖4為Ti離子注量從5×106cm-2增加到1×107cm-2時,32Gb器件新增、消失以及共同擁有的翻轉位。重離子注量為1×107cm-2時,兩款器件翻轉位消失數約是注量為5×106cm-2時檢測到的翻轉數的3%。

Ti離子注量分別為5×106 cm-2、1×107 cm-2圖4 32Gb器件翻轉位對比Fig.4 Comparison of bit upset for 32Gb device

位翻轉特點表明位翻轉是由浮柵電荷損失造成的。重離子入射導致浮柵電荷損失的機制有兩種,一是載流子通過氧化層勢壘流出浮柵的凈通量[17]。浮柵、控制柵以及襯底產生的電子空穴的高能部分會形成越過氧化層勢壘進出浮柵的通量。器件未加電時,編程狀態下,浮柵中的過量電子會在氧化層形成指向浮柵的電場。在電場的作用下,浮柵電子的流出通量大于流入通量,空穴流入通量大于流出通量,凈通量導致浮柵中的電子減少。二是氧化層中電子空穴對的產生、復合和傳輸[18]。重離子在浮柵周圍的氧化層中形成電子空穴對。在氧化層電場作用下,電子迅速漂移至襯底,一部分空穴形成氧化物陷阱電荷,屏蔽浮柵負電荷,另一部分進入浮柵中進一步導致浮柵電荷減少。當氧化物陷阱電荷退火后,屏蔽作用減弱,使得少量位翻轉消失。入射離子LET越大,在浮柵及其周圍沉積能量越多,浮柵電荷損失越嚴重,相同注量下翻轉比率也就越高。

對于重離子入射事件,存儲單元被擊中次數的概率可通過泊松分布表示為:

(1)

其中:P(k)為在1個間隔中存儲單元被擊中k次的概率;λ為在1個間隔中存儲單元被擊中的平均次數。實驗中離子最大注量為1×107cm-2,而25 nm NAND Flash存儲密度約在1010cm-2量級,即便考慮下一小節討論的多單元翻轉,λ仍是一個遠小于1的數值,從而有:

(2)

式(2)表明實驗中存儲單元被擊中兩次以上的概率很小,被擊中的存儲單元絕大多數僅被擊中1次,因此位翻轉比率與注量呈現較好的線性關系。可以推測,當重粒子注量與存儲密度可比時,存儲單元被多次擊中的概率升高,翻轉率斜率將會降低。但不同于已翻轉的SRAM存儲單元再次被擊中后可能再次翻轉的情況,浮柵存儲單元被多次擊中時只會使浮柵電荷損失更多,因此,隨著注量的累積,SRAM和NAND Flash存儲器翻轉率斜率的降低程度可能不同。

雖然8Gb器件和32Gb器件都采用25 nm工藝,但圖3顯示,相同注量下8Gb器件位翻轉率小于32Gb器件。由于兩款器件在設計上存在差異,如8Gb器件的存儲密度和32Gb器件相近但浮柵尺寸要略大于32Gb器件、存儲陣列的塊頁容量不同、負載差異導致編程后浮柵電荷數量不同等方面,使得兩款器件的位翻轉率雖然有著相同的變化趨勢,但是數值并不一致。

2.2 多單元翻轉

由于位翻轉比率和注量之間存在線性關系,可定義存儲陣列的單粒子位翻轉截面和單粒子翻轉事件截面。單粒子位翻轉截面表示為:

(3)

其中:n為翻轉數;N為被檢測的存儲單元數量;Φ為離子注量,cm-2。單粒子翻轉事件截面表示為:

(4)

其中,nEvent為翻轉事件總數,有:

(5)

其中,ni-Event為翻轉數為i的單粒子翻轉事件數量,當i=1時,n1-Event表示單單元翻轉(single-cell upset, SCU)事件數量,當i>1時,ni-Event表示多單元翻轉事件數量。根據各參數定義,有:

(6)

多單元翻轉比率反映了多單元翻轉事件的嚴重程度,可為NAND Flash存儲器抗輻射加固設計以及系統抗輻射加固方案提供重要參考。定義多單元翻轉比率:

(7)

ηi也可理解為1個存儲單元因為翻轉數為i的單粒子翻轉事件而翻轉的概率。σSEU/σE-SEU可理解為單粒子翻轉事件中翻轉位數的平均值,即:

(8)

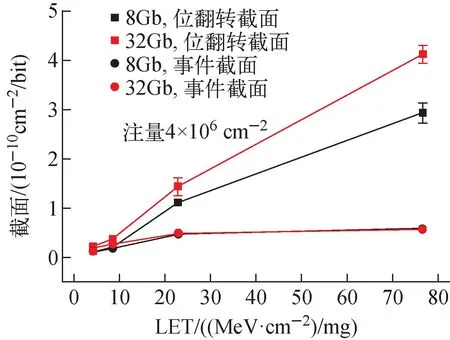

圖5 8Gb器件和32Gb器件的翻轉截面Fig.5 Cross sections for 8Gb device and 32Gb device

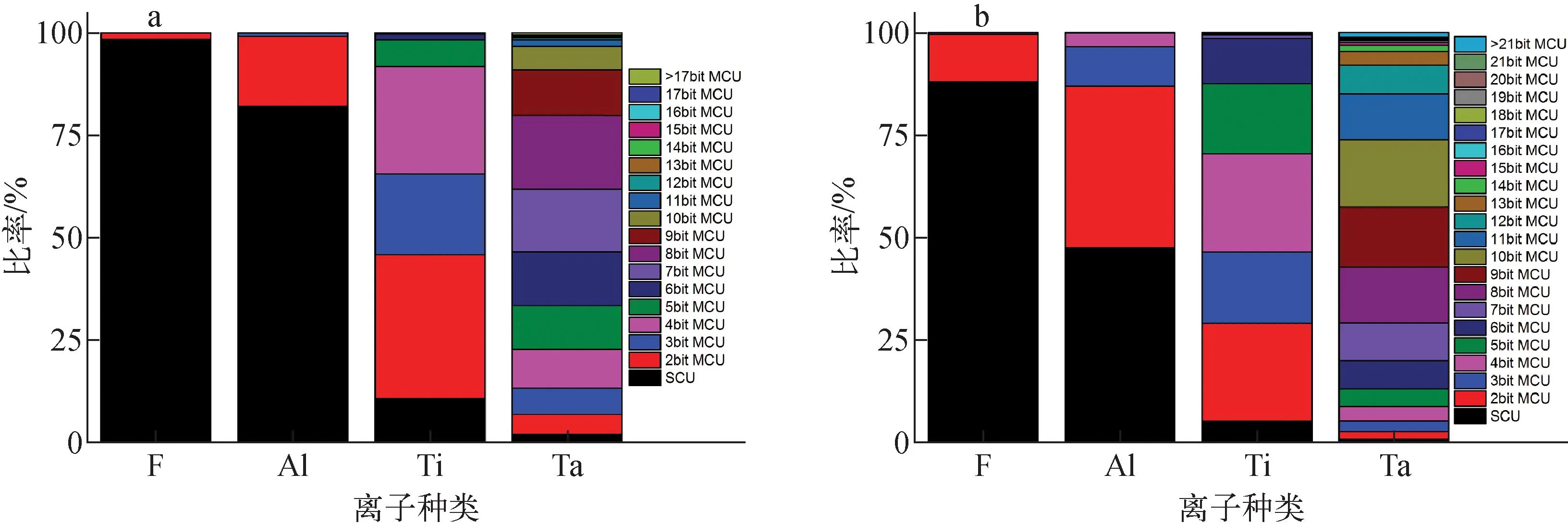

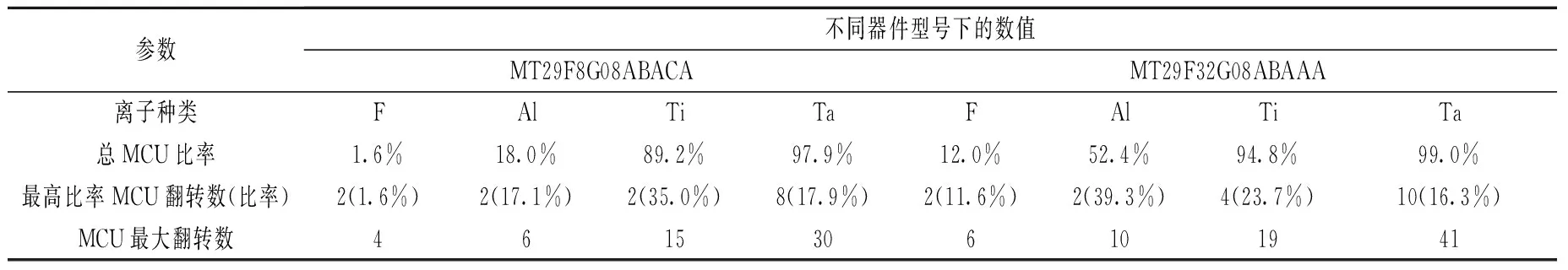

圖6為離子注量為4×106cm-2時,8Gb器件和32Gb器件的多單元翻轉比率。表3列出了多單元翻轉統計信息。從圖6、表3可看出,隨著入射離子LET的增加,總的多單元翻轉比率不斷增大,多單元翻轉比率最大值出現在翻轉數更多的多單元翻轉事件上,單粒子翻轉事件所能包含的最大翻轉數也被不斷突破。

a——MT29F8G08ABACA;b——MT29F32G08ABAAA圖6 不同入射離子輻照時多單元翻轉比率Fig.6 MCU ratios for different heavy ions

表3 多單元翻轉統計信息Table 3 Statistical information of MCU

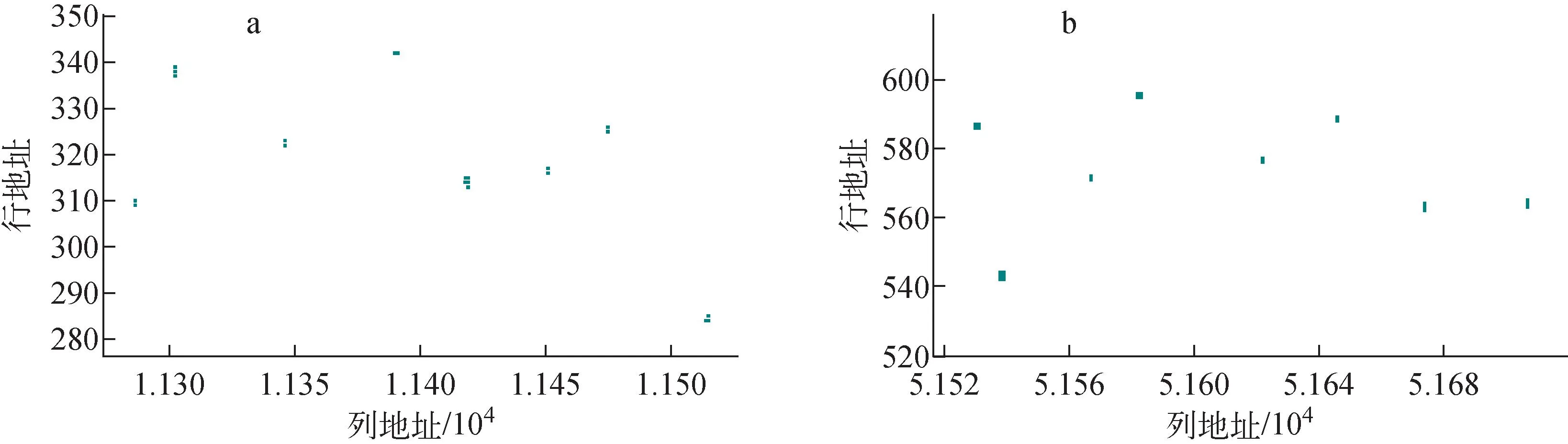

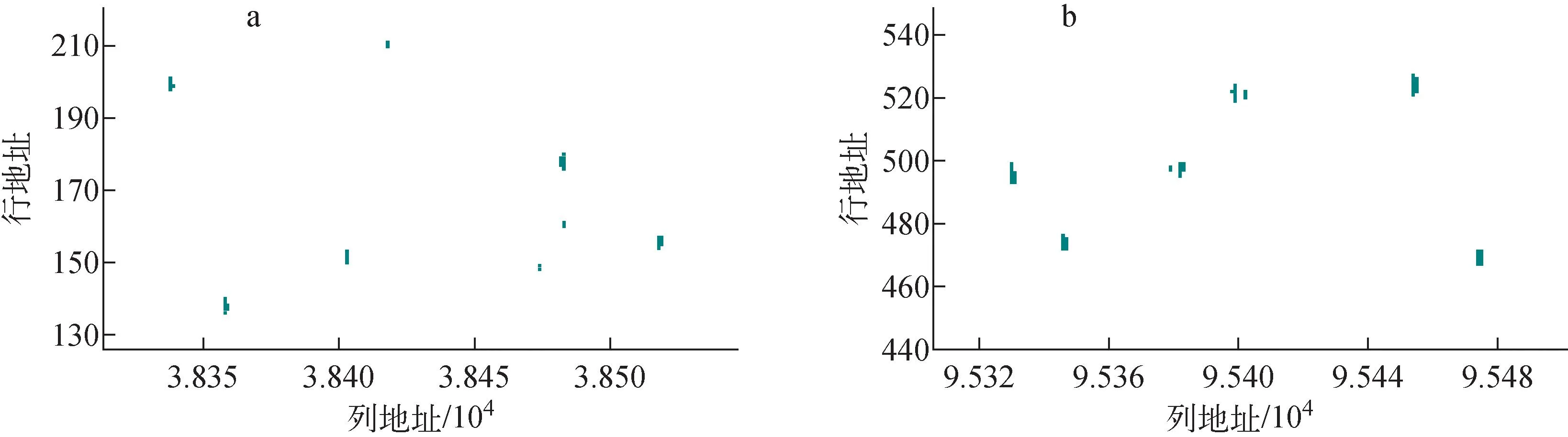

圖7、8分別為Ti離子和Ta離子入射時,兩款器件部分地址的多單元翻轉位圖。Ti離子造成的多單元翻轉拓撲結構基本上呈單列或雙列形式,極少數是行形式,這可能是因為位線間的存儲單元通過STI進行隔離,而同一位線的存儲單元是源漏共用的串聯結構,具有更高的電荷共享效率[1]。Ta離子入射時,多單元翻轉拓撲結構基本上呈雙列形式,少量是列間隔形式。

a——MT29F8G08ABACA;b——MT29F32G08ABAAA圖7 Ti離子注量1×107 cm-2時8Gb器件和32Gb器件的多單元翻轉位圖Fig.7 MCU maps for 8Gb device and 32Gb device at Ti cumulative fluence of 1×107 cm-2

a——MT29F8G08ABACA;b——MT29F32G08ABAAA圖8 Ta離子注量4×106 cm-2時8Gb器件和32Gb器件的多單元翻轉位圖Fig.8 MCU maps for 8Gb device and 32Gb device at Ta cumulative fluence of 4×106 cm-2

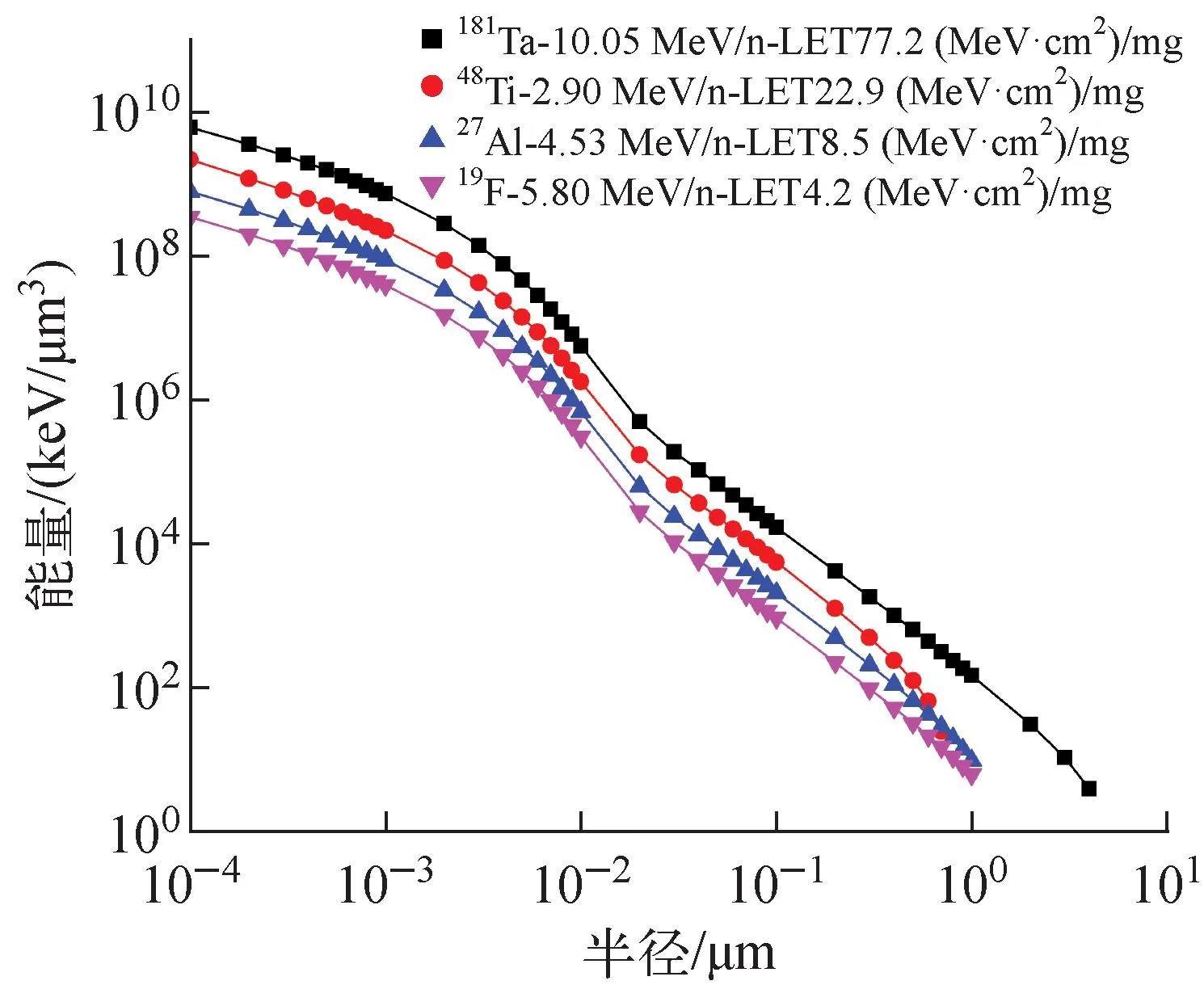

對于多單元翻轉的討論可以從離子電離徑跡入手。Fageehea等[19]發展了離子電離徑跡的解析模型。利用TRIM程序計算了重離子通過介質層和金屬布線層到達浮柵時的能量和LET,代入Fageehea等的解析模型,計算了離子能量沉積密度徑向分布,如圖9所示。可發現,不同離子相同位置處的能量沉積密度隨LET的增大而增大;單核子能量越高,轉移到σ電子的能量越大,離子電離徑跡半徑越大。實驗結果表明,多單元翻轉比率與離子LET呈正相關,表明多單元翻轉的主要影響因素是能量沉積密度,離子電離徑跡邊緣處已不足以造成位翻轉。當1個離子在一定范圍內沉積的能量足以引起多個存儲單元產生嚴重的浮柵電荷損失時,會造成1個多單元翻轉事件。

圖9 不同重離子的能量沉積徑向分布Fig.9 Radial distribution of energy deposition for different heavy ions

NAND Flash存儲陣列采用了位線交錯設計,但由于存儲密度很大,難以像SRAM一樣采用位交錯設計,因此當存儲數據為55 h時,從物理地址來看,1個塊內每兩列串聯結構交替存儲數據0和數據1,如圖10所示。定義重離子電離有效徑跡半徑為重離子入射造成的比率最大的多單元翻轉事件尺寸。以32Gb器件為例,Ta離子入射造成的比率最大多單元翻轉是10 bit,以雙列形式定性估計Ta離子電離有效徑跡半徑約為120 nm。根據圖9中Ta離子位于120 nm處的能量沉積密度反推Ti、Al、F離子的電離有效徑跡半徑分別約為70、40、30 nm,如圖10所示。由于浮柵存儲單元具有非易失性,不加電條件下仍能處于編程或擦除狀態。對Ta離子來說,如果徑跡中心位于初始狀態為編程狀態的存儲單元附近,將會引發雙列形式的多單元翻轉事件,如果徑跡中心位于初始狀態為擦除狀態的存儲單元附近,由于擦除狀態的存儲單元難以發生翻轉,將產生列間隔形式的多單元翻轉事件。對F、Al、Ti離子來說,其電離有效徑跡分別能覆蓋1~2、2~4、4~6個存儲單元。這一定性的分析結論既與實驗得到的位翻轉截面一致,也與多單元翻轉統計結果相一致。另外,從列間隔形式的多單元翻轉事件可推測,在空間應用中,當入射離子LET足夠高,或者1個字節內的相鄰位均為編程狀態時,重離子入射可能會造成同一字節多位翻轉,對數據糾錯帶來更大挑戰。

圖10 32Gb器件存儲陣列上的數據存儲與重離子電離有效徑跡示意圖Fig.10 Data stored in 32Gb memory array and effective ion track

2.3 注量對位翻轉的影響

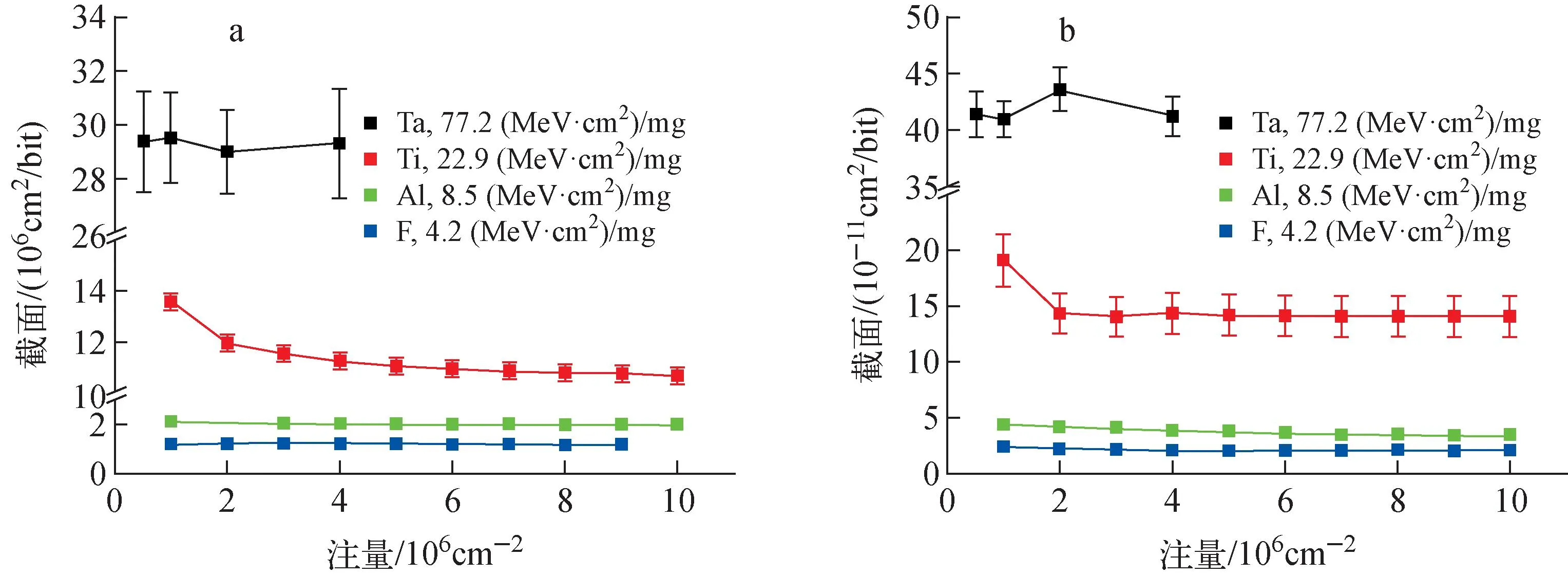

圖11為根據式(3)計算得到的4種離子在不同注量下的位翻轉截面。雖然實驗檢測到的位翻轉比率與注量呈現較好的線性關系,但是隨著注量累積,F、Al、Ti離子對應的位翻轉截面呈現降低趨勢,其中Ti離子對應的位翻轉截面變化最為明顯。

a——MT29F8G08ABACA;b——MT29F32G08ABAAA圖11 不同注量下的位翻轉截面Fig.11 Bit upset cross section as a function of cumulative fluence

從γ射線輻照結果來看,存儲單元的閾值電壓并非隨機分布在存儲陣列上,處于編程狀態閾值電壓分布低壓區的存儲單元傾向于在相鄰或靠近的地址上集中分布,在輻射環境下更容易發生翻轉[20-21]。圖12為不同Ti離子注量下,32Gb器件存儲陣列某塊在行地址上的位翻轉密度。從圖12可看出,輻照初期,翻轉的存儲單元更多處于某些集中的地址。這類存儲單元翻轉截面較大,但是數量較少。隨著注量累積,由于這類存儲單元數量迅速減少,在所有位翻轉中占比越來越小,而其他大量存儲單元的翻轉數增長率變化不明顯,因此分布開始變得更加均勻,從而整體上呈現出位翻轉截面降低的趨勢。

圖12 Ti離子輻照下32G器件第200塊的位翻轉分布Fig.12 Bit upset distribution of the 200th block of 32Gb device under Ti irradiation

這一現象可通過一個簡化的數學模型來解釋。假設更容易發生翻轉的存儲單元的數量是N1,其翻轉截面為σ1,其他存儲單元的數量為N2,翻轉截面為σ2,N1?N2,σ1?σ2,有:

N=N1+N2

(9)

僅考慮存儲單元被擊中1次的情況,根據泊松分布,有:

(10)

當入射離子LET很小,如Al、F離子,σ1很小,σ2約為0,有:

(11)

表明位翻轉截面隨注量累積緩慢變小。當入射離子LET很大,如Ta離子,σ2不再是0,此時N1σ1?N2σ2,e-Φσ1 (12) 因此統計漲落、測量誤差等因素會造成截面變化不明顯甚至波動。當入射離子LET處于中間值,如Ti離子,N1σ1和N2σ2在量級上可比,即有: (13) 此時σ1要大于入射離子LET很小時的σ1,因此相同注量下Ti離子對應的σSEU的變化相比于F、Al離子對應的σSEU更為明顯。 為了研究不同注量下NAND Flash存儲器位翻轉特點及其翻轉截面的變化,以及重離子入射導致的多單元翻轉,以兩款25 nm SLC NAND Flash存儲器為載體開展了重離子實驗研究。 實驗發現重離子入射導致的位翻轉具有隨機性、繼承性、少量短時退火以及可再次編程等特點,表明位翻轉主要是由存儲單元浮柵電荷損失造成。25 nm工藝節點下的浮柵存儲單元對于重離子入射敏感,1個重離子在擊中靈敏體積的情況下足以引起位翻轉,因此當注量遠小于存儲陣列密度時,位翻轉比率隨注量累積基本呈線性變化。 重離子導致兩款器件出現多單元翻轉。多單元翻轉的嚴重程度與入射離子LET正相關,其存在導致單粒子位翻轉截面并未達到飽和,這意味著基于威布爾擬合的單粒子位翻轉截面評估方法可能難以適用于NAND Flash存儲器,或者可能存在較大誤差。由于存儲陣列采用了位線交錯設計,當存儲向量為55 h時,多單元翻轉拓撲結構呈現單列、雙列以及列間隔形式。利用離子電離徑跡模型估算得到離子電離有效徑跡半徑,半徑估計值與實驗得到的位翻轉截面和多單元翻轉統計結果一致。可推測,在空間應用中,當入射離子LET足夠高,或者1個字節內相鄰位均處于編程狀態時,重離子入射會造成同一字節多位翻轉,對數據糾錯帶來更大挑戰。 隨著注量累積,兩款器件的位翻轉截面存在下降趨勢,這是由于處于編程狀態閾值電壓分布低壓區的存儲單元傾向于在相鄰或靠近的地址上集中分布,隨著注量累積,這類存儲單元數量迅速減少,而其他大量存儲單元的翻轉數增長率變化不明顯。這一現象在Ti離子入射時尤為顯著。位翻轉截面與注量的關系意味著較高注量下得到的位翻轉截面可能會低估NAND Flash存儲器在軌翻轉率,利用較低注量獲取位翻轉截面可能會更為保守或者準確地評估NAND Flash存儲器在軌翻轉率。3 結論