一種抗噪聲折疊寬范圍低雜散小數分頻鎖相環

蔡劍茹, 尹勇生, 滕海林, 楊文杰, 孟 煦

(1.合肥工業大學 微電子設計研究所,安徽 合肥 230601; 2.合肥工業大學 教育部IC設計網上合作研究中心,安徽 合肥 230601)

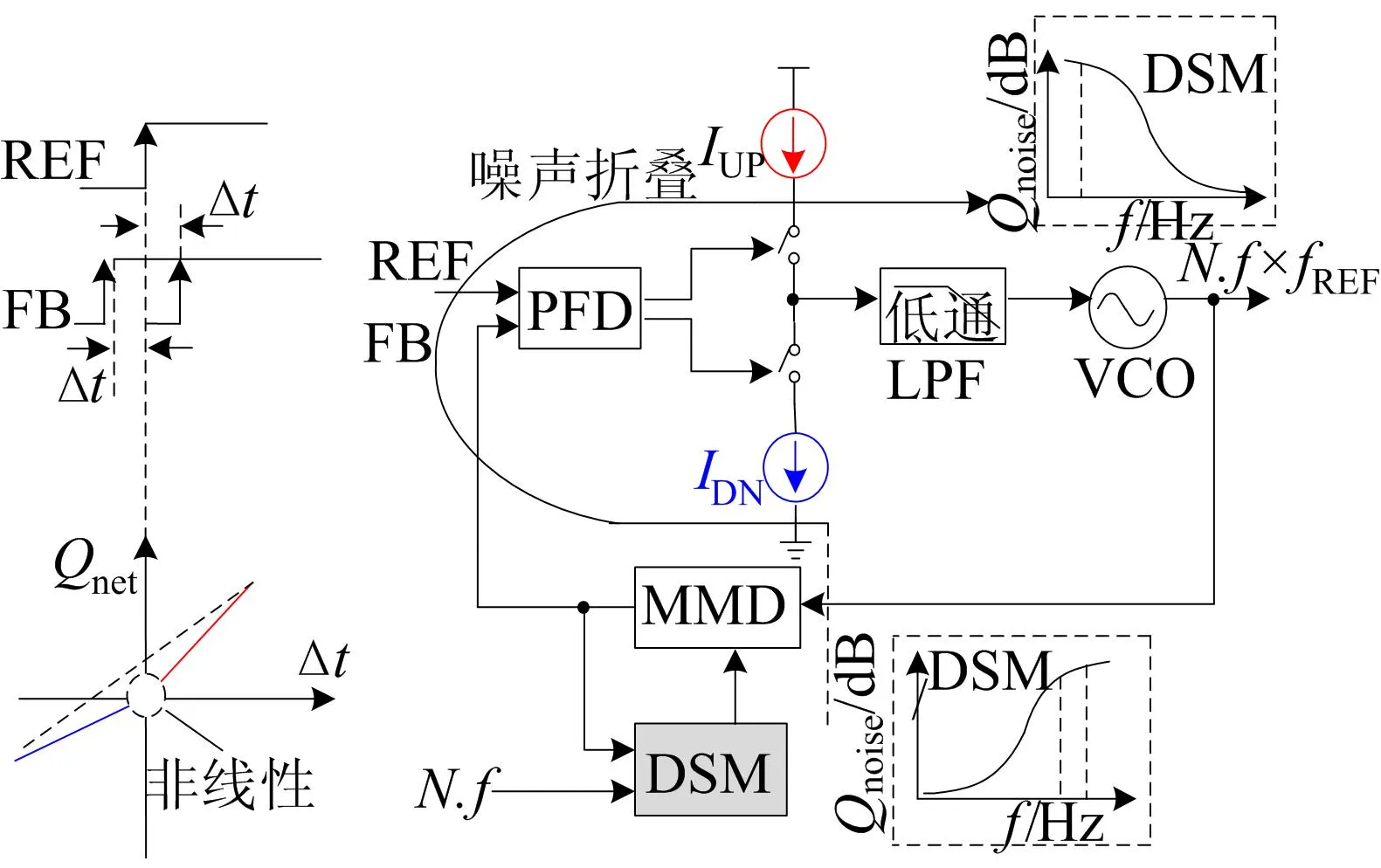

Ⅱ型鎖相環(phase locked loop,PLL)具有良好的性能折衷和技術成熟度,已成為當下各類片上系統中最為常用的時鐘產生電路架構。 基于環形振蕩器(ring oscillator,RO)的設計具有多相位輸出、輸出頻率范圍廣、芯片面積小等諸多優點,受到設計者的重視。 根據輸出頻率精度是否受限于參考源頻率fREF,PLL可以分為整數型和小數型2種類別。 小數型PLL利用和差調制器(delta-sigma modulation,DSM)控制多模分頻器(multi-modulus divider,MMD)的分頻比動態變化,從而在平均效果下實現N.f分頻。 傳統小數型PLL結構如圖1所示。

圖1 傳統小數型PLL結構

靈活的輸出頻率使得小數PLL逐漸替代整數PLL成為時鐘和頻率產生的主流架構。 由于只能實現動態鎖定,小數鎖相環路中的電荷泵(charge pump,CP)會隨著反饋信號的超前或滯后,對環路濾波器進行相應的放電或充電。 從圖1可以看出,當電荷泵電流存在失配ΔICP時,流入環路濾波器的凈電荷量為:

(1)

其中,t0為鑒頻鑒相器(phase frequency detector,PFD)的復位延時。 由式(1)中右邊的第2項可以看出,PFD/CP的輸入輸出特性中存在非線性關系,即非線性環節存在,會將DSM搬移至高頻偏處的量化噪聲重新折疊回低頻偏處,惡化帶內噪聲性能[1-4]。

文獻[5-6]通過刻意偏移PFD/CP的工作區,實現對環路的線性化,但在控制電壓上引入的波動惡化了參考雜散性能;文獻[7]通過提出基于采樣保持的線性化電荷泵及其時序控制電路,在參考信號脈寬發生變化時,仍具有較好的雜散抑制效果,但是時序控制模塊較為復雜;文獻[8]使用連續線性電流替代傳統電荷泵,對參考雜散的改善效果有限;文獻[9]通過使用脈沖偏移電流實現環路的線性化,降低了控制電壓上的波動,但是固定的脈沖寬度僅適用于單一輸出頻率的情況,與RO所能提供的寬輸出范圍相悖。

本文提出一種根據輸出頻率變化、自適應調節偏移脈沖電流寬度的線性化技術,在避免噪聲折疊的同時,始終保持環路良好的參考雜散性能。

1 抗噪聲折疊技術回顧

避開PFD/CP非線性工作區間是有效抑制噪聲折疊的方法,如在PFD充電[5]或者放電[6]路徑的復位端引入一段延時,或是在電荷泵與低通濾波器之間加入直流偏移電流,因而PLL環路會在PFD的輸入端引入反向的偏移以達到平衡,維持鎖定。 PFD/CP線性化技術如圖2所示。 圖2b中,Inet=IUP-(IDC+IDN)。 圖2d中,Inet=IUP-(IPul+IDN)。

圖2 PFD/CP線性化技術

由圖2a可知,若直流偏移電流大小為IDC,則環路鎖定后,為了維持參考電壓即輸出頻率的不變,參考信號REF相對于反饋信號FB的平均值將提前IDCTREF/ICP的時間到達。 根據DSM的設計及行為級仿真結果,當選擇足夠大的IDC,即可保證在FB存在瞬時跳變的情況下,REF仍始終領先。 PFD/CP的輸入輸出特性可表述為:

Qnet(Δt)=IUPΔt-IDCTREF+ΔICPt0

(2)

其中:IUP為充電電流大小。

由式(2)可知非線性的分量得以去除。 由圖2b可知,偏移電流IDC的引入,會使得控制電壓VC上出現約IDCTREF/C2的波動,惡化參考雜散。

由圖2c、圖2d可知,通過將偏移電流改為大小為IPul、寬度為TPul的脈沖電流[9]形式,即通過滿足IPulTPul=IDCTREF的關系,可引入與前文相同的偏移電荷量,實現對環路的線性化;進一步保持脈沖的開啟與參考源大致同步,可使環路控制電壓上的波動大大改善。

2 基于自適應脈寬的線性化技術

上述仿真中的電流脈寬是為當前輸出頻率所定制化選取的。 考慮到DSM在反饋信號FB上所引入的跳變量與輸出信號周期TVCO相關,因此當輸出頻率減小時,所設定的脈沖電流的寬度可能不再足以將環路完全線性化,令噪聲折疊現象不能被完全移除。 相對地,根據PLL輸出的最低頻率設計一個較寬的偏移脈沖電流,雖然可以始終保持環路的線性化,在輸出高頻率時卻令CP額外導通了不必要的時長,同樣導致帶內噪聲性能較理想情況有所下降。

為了實現在輸出頻率變化時,依然能實現合適的偏移量,兼顧去噪聲折疊和適當的CP導通時長,有必要令偏移電流的脈寬實時跟蹤VCO的輸出頻率,因此本文提出自適應脈寬產生電路(pulse generator,PG),如圖3所示,其核心之處在于采用了與VCO相同的延時單元產生所需的脈沖寬度。 若組成振蕩器的延遲單元延遲時間為td,則N級環形振蕩器的工作頻率為:

圖3 窄脈沖產生結構原理

fVCO=1/TVCO=1/(2Ntd)

(3)

因此使用m×2N個延遲單元即可實現m×TVCO長度的延遲,且由于與PLL共享了控制電壓,所產生的延遲具有良好的抗PVT波動特性。

3 電路設計及仿真結果

本文設計的小數分頻PLL結構如圖4所示。

圖4 小數分頻PLL結構

環路內嵌低壓差線性穩壓器(low dropout regulator,LDO)[10]提升了振蕩器對電源噪聲的抑制能力,從而可以簡化振蕩器的設計。 仿真顯示,設計的DSM在反饋路徑上引起的瞬時跳變范圍約為3.5TVCO,因此在脈寬產生電路中應輸出約1.8TVCO的延遲以線性化環路。 鎖定檢測(locked detector,LD)[11]電路與PFD輸出信號的相位差比較,當兩者相位差維持低于設定值時,開啟偏移脈沖電流產生模塊。 本文偏移電流的大小等于電荷泵電流大小,簡化了整體設計考量。

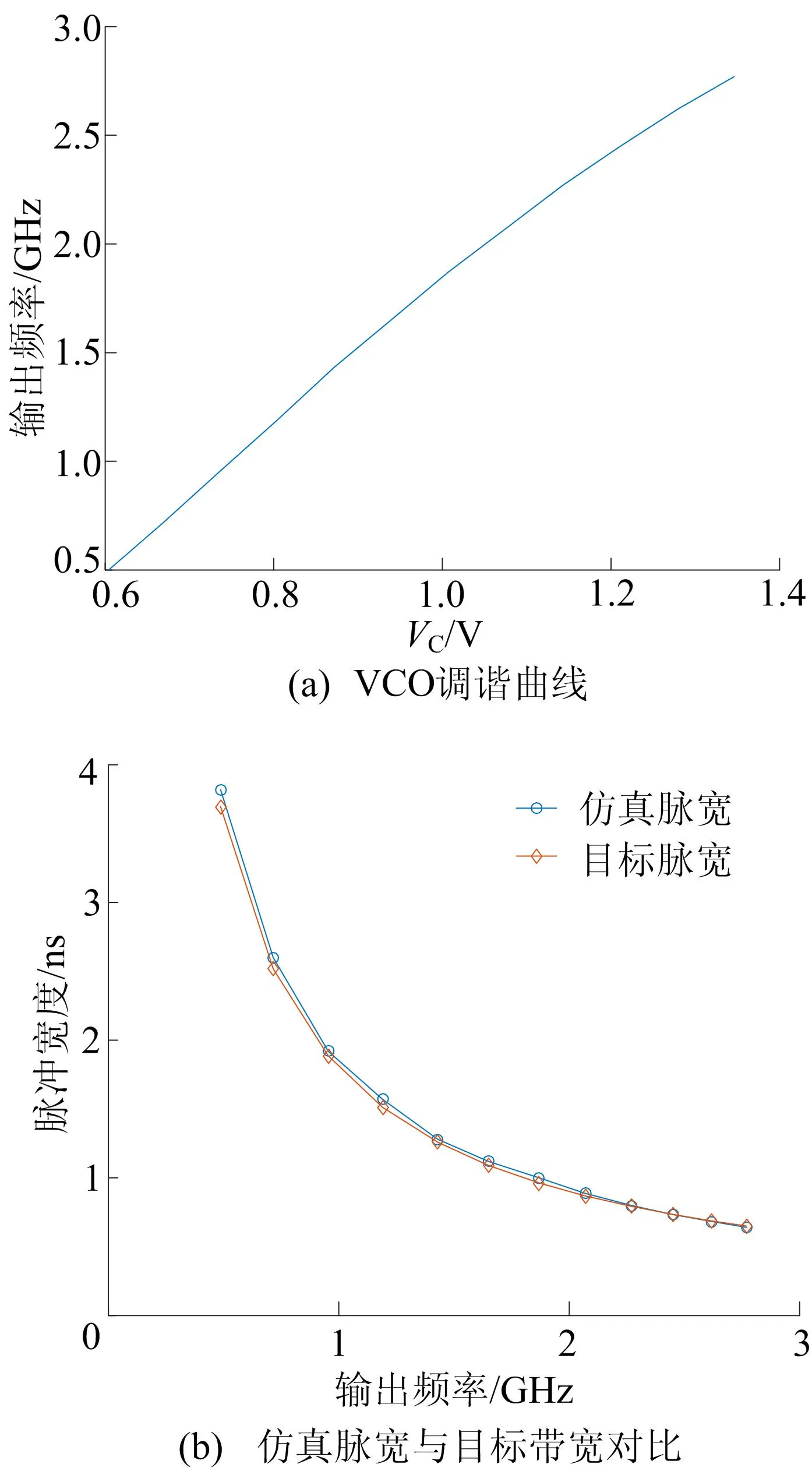

因為環路結構具有優越的電源噪聲抑制能力,所以在VCO的設計中采用9級單端反相器級聯的形式,多相位的輸出亦為后續的應用提供充足的便利性。 脈沖產生模塊仿真結果如圖5所示。 由圖5a可知,當控制電壓VC從0.60 V變為1.35 V時,輸出頻率覆蓋0.6~2.7 GHz,VCO增益KVCO為3 GHz/V;當VC為1.05 V時,輸出目標頻率為2.0 GHz,功耗為7.5 mW。

圖5 脈沖產生模塊仿真結果

由式(3)可得,偏移脈沖電流的脈寬應由約32個(1.8×2×9)延遲單元構成,但如此數量的延遲單元會引起面積的大幅增加及功耗的上升。 以反相器放電為例,考慮到反相器放電過程中的總寄生電容Ctot和MOS管的等效導通電阻Rn[12],即

(4)

(5)

其中:Wp、Lp分別為PMOS管的柵寬和柵長;Wn、Ln分別為NMOS管的柵寬和柵長;m為每一級反相器的NMOS與PMOS的并聯個數;Wn/Ln為NMOS的寬長比;Kn為NMOS的場效管增益系數;ID,sat指MOS管處于飽和區時的電流大小;Cox為單位面積柵氧化層電容大小。 圖5a中,Wp=700 nm,Wn=300 nm,Lp=Ln=130 nm,m=50。

單級反相器所引入的延遲時間td=0.7RnCtot,實則為一個與NMOS晶體管和PMOS晶體管寬度W的比值相關的量。 這使得可以在實現目標脈寬的32個延遲單元中采用等比復制技術,如將m縮小為原值的1/50,進而實現脈寬產生電路面積和功耗大大降低。 本文通過在振蕩器和延遲單元中采用尺寸相同、數量不同的方式,進一步提高復制的精度。 由圖5b可知,在VCO的輸出頻率范圍內,基于1/50等比復制單元所產生的脈寬始終與1.8TVCO的目標寬度極為接近,兩者誤差最大僅為3.75%。VC為1.05 V時所消耗的功耗也僅為14.7 μW,相對于非等比復制的結構,功耗降低了50倍。

DSM使用MASH1-1-1結構的3階DSM調制器。 使用基于脈沖吞咽計數器的多模分頻器,輸入頻率為55.25 MHz時,通過分頻比的調整,可輸出范圍為0.6~2.7 GHz的信號。 環路中內嵌的LDO結構的非對稱性有利于實現LDO的低功耗。 當VC=1.05時,LDO的電源噪聲抑制能力約為60 dB。 電荷泵的電流大小為8 μA,充電電流設置失配電流單元,失配電流單元選取0.08、0.08、0.16、0.32 μA,分別代表1%、1%、2%、4%的失配,模擬電荷泵范圍為1%~8%的電荷泵失配的情形。

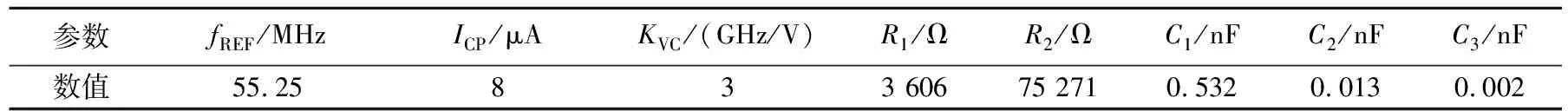

表1 PLL設計參數

最終的PLL設計參數見表1所列。 需要指出的是,相對于常規設計,本文充分考慮了線性化技術在CP中引起的額外導通時間,并通過增加CP電流的方式達到預期的帶內噪聲。

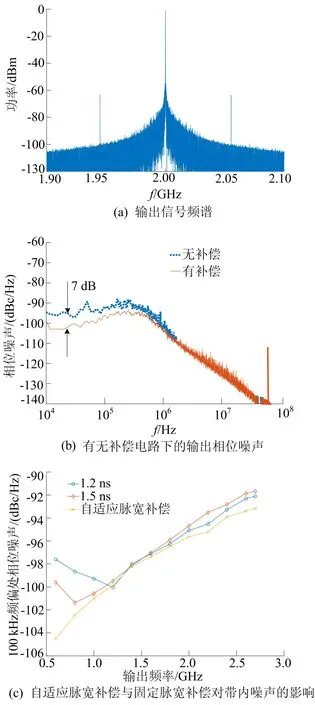

輸出頻率為2.0 GHz且CP中存在8%失配情形下,鎖相環的各項仿真性能如圖6所示。

圖6 自適應脈寬補償性能仿真結果

由圖6a可知,在Cadence Spectre下,對電路進行瞬態仿真后得到輸出頻譜,此時參考雜散約為-63 dBc。 由圖6b可知,通過Cadence Spectre仿真提取電路各模塊的參數和性能指標后,帶入系統仿真軟件CppSim得到相位噪聲曲線,通過脈沖偏移電流線性化環路后,帶內噪聲性能優化了7 dB,噪聲折疊現象得以避免。 由圖6c可知,通過使用固定脈寬(1.2、1.5 ns)與使用自適應脈寬2種線性化方案下帶內(@100 kHz)相位噪聲的對比,所提出的自適應脈寬的線性化方案在全部的輸出頻段內均可以避免噪聲折疊現象,且通過維持最優的脈沖寬度,在輸出高頻時達到了相對優化的帶內噪聲性能。 文獻對比結果見表2所列。

表2 文獻對比結果

4 結 論

本文設計了一個具有自適應抗噪聲折疊能力的寬輸出范圍小數分頻PLL。 通過等比復制技術所設計的脈寬產生電路能夠在工藝、電壓、溫度變化的情況下,始終適應PLL的工作頻率,以最優的電流脈寬實現對環路的線性化,避免噪聲折疊現象,且維持良好的參考雜散性能。 所提出的自適應脈寬產生方案對于其他結構的設計同樣適用。