基于DWA 算法的DAC 芯片譯碼電路設計

陳彬彬,藍浩宇,程振輝,曾智勇

(北方工業大學,北京,100144)

0 序言

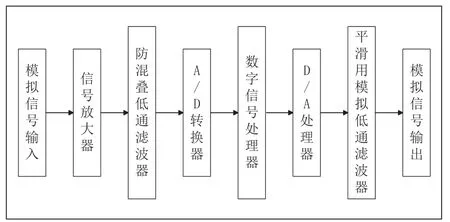

當今社會,隨著電子技術的快速發展,越來越多的信號需要使用計算機來處理,在自然界中我們所能接觸到的信號大多是模擬信號,像溫度的升高和降低,壓力的增加和減少等變化所產生的信號都是模擬信號,但是計算機只能處理數字信號,所以在進行數字信號處理的過程中,我們都是先采用模數轉換裝置(ADC)將采集到的模擬信號轉化成數字信號,然后對這些信號經過一系列的數字信號處理(DSP),但由于能被我們聽懂的依然是模擬信號(比如聲音信號),所以最終我們還要將處理完的數字信號通過數模轉化裝置(DAC)再轉化成模擬信號,這就是數字信號處理系統(如圖1 所示)的核心內容。隨著電子產品的不斷更新,各個領域對數字信號處理系統的要求也越來越高,ADC 和DAC 作為數字信號處理中最關鍵的部分,它們的設計和優化就變得格外重要,本文主要針對DAC 的譯碼電路進行設計,不涉及實體電路的搭建,使用ModelSim 和Quartus II 軟件進行聯合仿真,驗證思路的正確性和可行性。

圖1 數字信號處理系統的框圖

DAC 的全稱是Digital to Analog Converter,即數模轉換器,它是一種可以實現將數字量轉換成模擬量的電路結構[9]。作為最基本且最重要的混合信號構建模塊,DAC 由N-2N數字譯碼電路和模擬等分壓或等分流電路組成,所輸入的N個數字碼(bN-1,…,b2,b1,b0)經過譯碼電路生成2N個開關信號去控制模擬電路中的等壓或等流電路開關,從而輸出相應的模擬信號,輸出電壓表達式如下:

其中k為比例放大系數,Vref為分壓電路的總輸入電壓。

在數字碼發生變化的瞬間,DAC 模塊會產生完全不同的電壓(或電流)輸出,這會導致輸出的模擬信號中出現噪聲。消除噪聲的解決方案之一是使用溫度計碼,溫度計碼的使用對譯碼電路而言,當輸入的數字碼數值增加1 的時候,所輸出的譯碼結果中會多一位1。另外,在芯片加工過程中,同樣大小的電阻或電容都有一定的誤差,也就是等壓(或等流)電路之間存在一定的工藝誤差,如果輸出碼所控制的模擬電路固定不變,則會產生較大的工藝匹配誤差帶入到輸出模擬信號中,為了減少這種誤差,一般采用數據權重平均算法(DWA)來平均使用分壓電路。

在實際生產和應用中,通信系統的設計和研究直接在硬件上實現起來不僅復雜而且昂貴,所以現代通信技術的系統分析通常使用計算機仿真來進行,這樣一來可以在很大程度上降低設計的難度和成本。隨著Verilog 等設計語言的出現,大大簡化了包括譯碼電路在內的現代通信技術的設計難度,并且隨著 Quartus II 和 ModelSim 等軟件的發展,采用計算機仿真技術來進行系統設計,仿真和調試越來越普遍。本文通過使用 Quartus II 和 ModelSim 平臺,采用Verilog語言進行隨機信號的產生及動態平均信號的代碼實現和結果測試(即圖1 D/A 轉換器的譯碼電路部分)。

1 DAC 譯碼電路的設計思路及系統組成

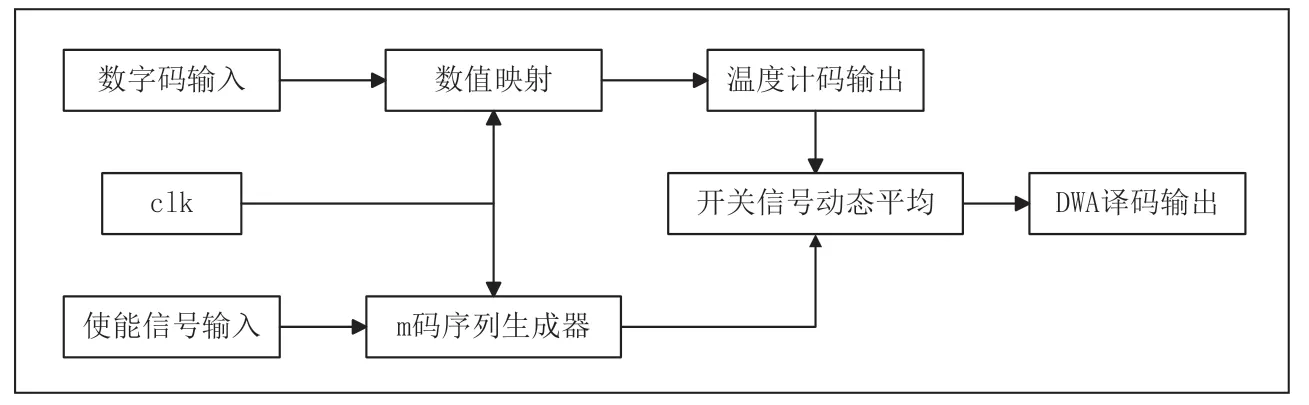

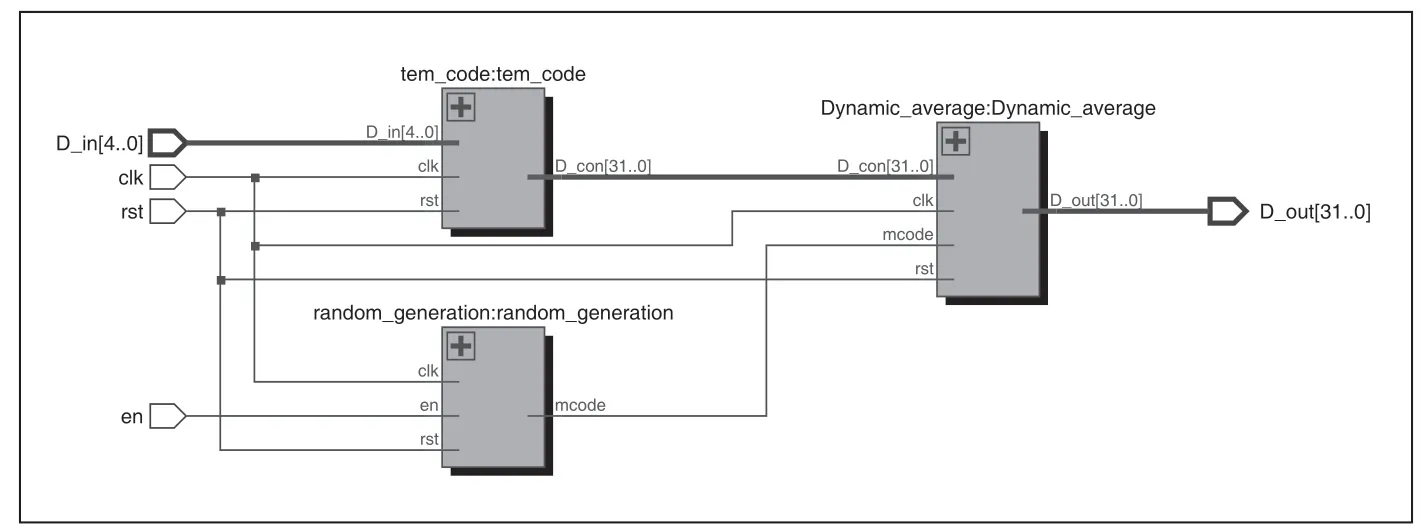

本文所設計的是用于5 位二進制輸入信號的DAC 芯片開關控制信號生成電路,它可以將串行輸入的五位數字碼,以數值映射的方式譯成不同的溫度計碼,然后利用隨機碼生成器所生成的隨機碼序列借助桶形移位器對溫度計碼進行動態平均,最終并行輸出動態平均后的開關控制信號,該信號可用于控制模擬等分壓或等分流電路中電壓源或者電流源的開斷,可以達到良好的動態性能。本文所設計的譯碼電路主要由三部分組成,分別為溫度計碼生成模塊,本地偽隨機碼發生器模塊(生成m 序列)和動態平均模塊。總體設計思路如圖2 所示。

圖2 DAC 譯碼電路總體設計框圖

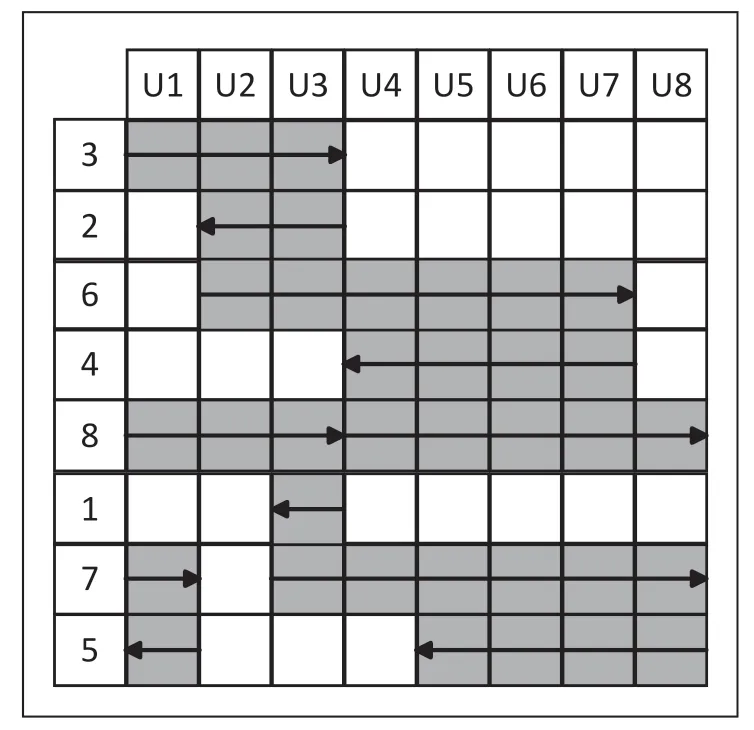

下面分別介紹每個模塊的工作原理和輸出信號,在溫度計碼生成模塊中,串行輸入的5 位數字碼會被譯成32 位的溫度計碼,作為原始的開關選擇信號。在偽隨機碼發生器模塊中,偽隨機碼發生器會根據給定的本源多項式利用線性反饋移位寄存器生成一個m 序列,該序列基本符合隨機數的要求。在時鐘信號的控制下,開關選擇信號和m 序列分別進入不同的寄存器,被鎖存。在規定的指令下,鎖存器被打開,開關選擇信號和m 序列進入到動態平均模塊中,這里的動態平均模塊相當于一個桶形移位器(原理圖如圖3 所示),在時鐘信號的觸發下,開關選擇信號會根據m 序列的值進行移動。m碼為1時開關控制信號輸出整體左移一位,為0 時整體右移一位,循環時將上一次輸出值的下一位作為起始位再進行循環移位,最后并行輸出完成權重平衡之后的開關控制信號,該信號可輸入到模擬等分壓或等分流電路中控制電壓源或者電流源的開斷。因為偽隨機碼產生的低電平和高電平的比例大致相同,所以最終的開關控制信號在一定的區間內來回移動,從而能夠平均使用到每一個電流源,避免了個別電流源的閑置或長期占用。同時,溫度計碼的使用可以保證當數字輸入碼每增加“1”時,都只會多打開一個單位電流源,避免了出現大量的電源開關在同一時刻被開啟或者關斷而引起很大的數字干擾,有利于使整個電路達到良好的動態性能[1]。

圖3 開關控制信號的循環圖示

2 溫度計碼生成模塊的設計

首先來介紹一下溫度計碼的組成方法,溫度計碼類似于一串比特流,它只由“0”和“1”來構成,溫度計碼的特殊之處在于,在這串比特流中,“1”全部出現在低位,“0”全部出現在高位,而且“0”和“1”都是連續出現的,不能出現“0”和“1”相間排列的情況,即只能寫成00000001、00000111、01111111 或者 11111111 的形式。溫度計碼的大小只能通過增加“1”的位數或者減少“1”的位數來改變,就像溫度的變化一樣,故由此得名。

溫度計碼在本文所設計的DAC 譯碼電路中充當的是開關控制信號的作用,用于控制DAC 的模擬電路部分中電流源的開斷。以常見的二進制加權型電流舵型 DAC 為例,這種DAC 譯碼電路每一位的權值按照2 的冪遞增,每一位數字碼所控制的電流的大小按照權值的依次遞增。例如對于一個10 位的二進制加權型電流舵DAC,它的最高位和最低位的電流比值是1024∶1,但是以現在的工藝很難達到如此高的匹配精度,尤其是在轉換的半量程處,即開關控制信號從011111111111 變化為100000000000 時,大量的電流源同時開斷會使得輸出的電流出現毛刺,從而影響DAC 的動態性能[1]。溫度計碼的發明和設計能夠較好地改善二進制加權型電流舵型 DAC 的缺點,提高DAC 的分辨率。這樣設計出的DAC 譯碼電路不僅可以綜合二進制加權型DAC 結構簡單、占用版圖面積小的優點,而且溫度計碼的結構也提升了動態性能,從而在精度和面積上都得到了優化[1]。

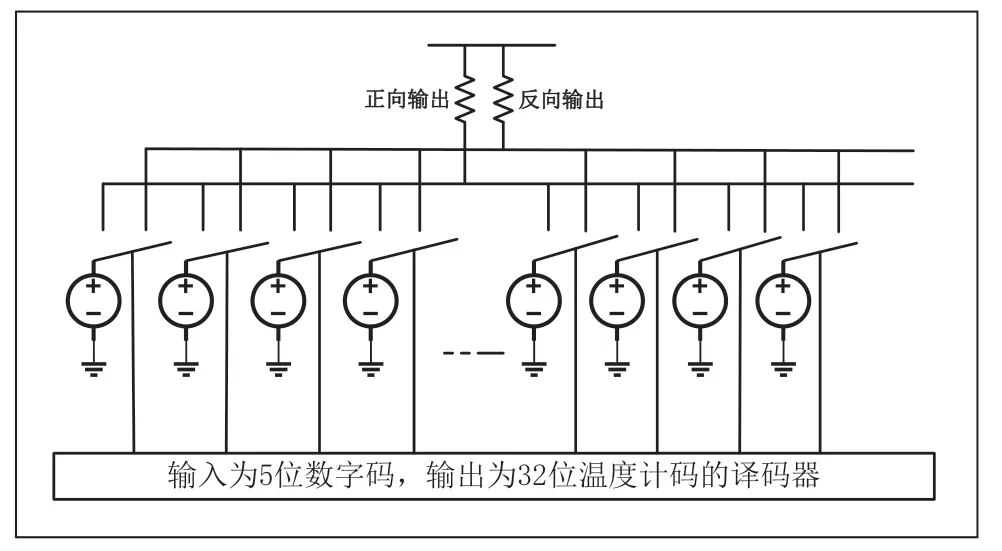

圖4 是一個5 位溫度計碼型 DAC 的結構簡圖。圖中每個電流源所控制的電流值是相同的,每一個電流源都有一位數字開關用以控制電流源輸出電流的方向(正相或負相)。控制這些開關的信號是由五位二進制輸入碼到溫度計碼譯碼器提供的[1]。

圖4 5 位溫度計碼型 DAC 的結構簡圖

3 本地偽隨機碼發生器模塊的設計

本文所介紹的本地偽隨機碼發生器模塊的作用是產生m 碼序列,首先介紹一下什么是m 序列,m 序列是最長線性反饋移位寄存器序列的簡稱,又叫做偽隨機碼,是一種可以預先確定并可以重復地產生和復制、又具有隨機統計特性的二進制碼序列[8]。它容易產生且具有一定的隨機性,在一定條件下可以作為隨機碼被使用,是目前廣泛應用的一種偽隨機序列。

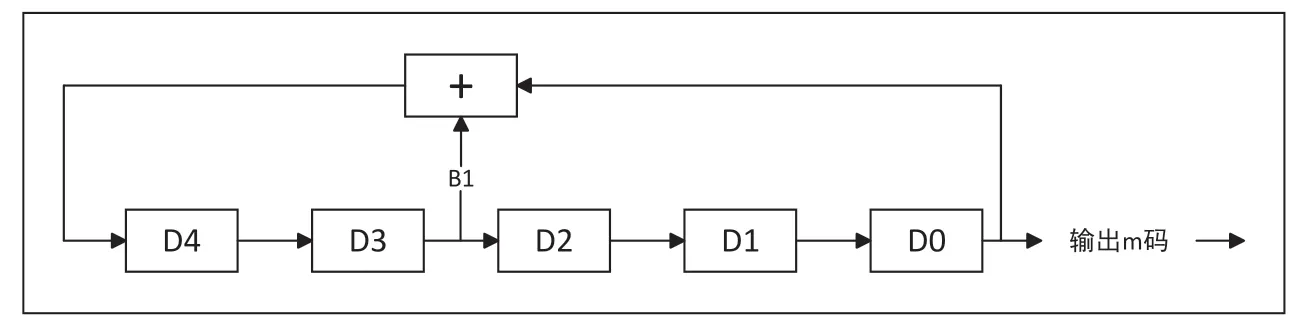

圖5 是由5 級移位寄存器構成的偽隨機碼序列發生器。寄存器的狀態取決于時鐘控制下輸入的信號,例如第2 級移位寄存器的狀態取決于第3 級移位寄存器輸出的信號,B1 是反饋線路,在程序上為異或操作,因此一般形式的表達式為:

圖5 m 序列的實現結構

偽隨機碼的verilog 代碼說明:

因為rst 為全局異步復位信號,低電平有效,所以最開始將移位寄存器相位復位成5'b11111,即:

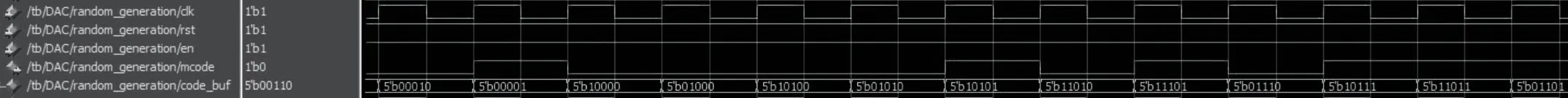

當時鐘的上升沿信號來臨時,如圖6 所示,m 序列發生器中的每一位值進行右移操作,最高位的值由初始次高位值和初始最低位值進行異或操作后得到,最后將每一次的最低位值賦給輸出變量,進行輸出。同時也可以看出m 序列中高電平和低電平出現的時刻并沒有很強的規律性而且它們所占的比例大致相同,所以基本確定該序列有一定的隨機性,可以作為偽隨機碼被使用。

圖6 m 碼序列仿真結果

4 動態平均模塊的設計

本文所設計DAC 譯碼電路的動態平均模塊主要利用的是數據權重平均算法(DWA),該算法的基本思想是通過滾動開關信號的方式來平均的使用電流源,避免某些電流源被經常使用,而某些電流源被經常閑置,從而降低由于工藝造成的不匹配性導致單位電流源之間電流值不匹配的影響,以達到很好的動態性能[1]。

該模塊的具體實現方法是,基于數據權重平均算法(DWA)的原理,設計了一個方向可調換的桶行移位器(如圖3 所示),該移位器可以根據要求改變信號移動的方向和位數,而且在單個時鐘周期內能使任何位數的數據完成移位或循環。由于它的移位操作具有圓形特性,故有 “桶形移位器”之名 。在該設計模塊中,桶行移位器利用本地偽隨機碼發生器模塊所生成的m 碼序列對溫度計碼生成模塊輸出的溫度計碼(即開關控制信號)進行滾動移位,m 碼為1 時開關控制信號輸出整體左移,m 碼為0 時整體右移,循環時將上一次輸出值的下一位作為起始位再進行循環移位。由于偽隨機碼具有一定的隨機性,而且通過仿真結果(如圖6 所示)可以看到m 碼的高電平和低電平所占的比例大致相同,而且在設計時默認每一次都只移動一位,所以可以保證開關控制信號是在一定區間內均勻的滾動,從而達到平均使用DAC 模擬電路模塊中電流源的目的。本文所設計的桶形移位器的移動方式如圖3 所示,該圖以8位控制信號為例,按照從上到下的順序描述了信號移動的過程,最前面一列的數字表示移動的位數,最上面的一行數字表示一共有8 位信號參與移動,箭頭表示移動的方向。

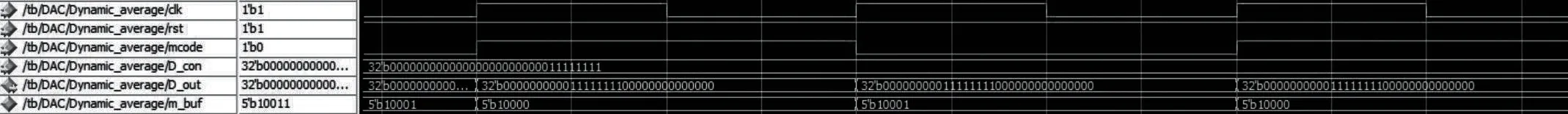

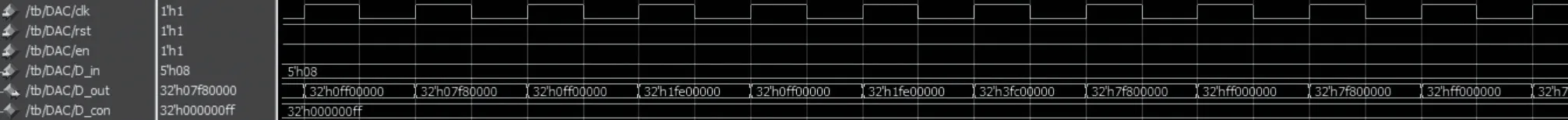

動態平均模塊輸出的是完成權重平衡之后的開關控制信號,其仿真結果如圖7 所示。

圖7 動態平均模塊仿真結果

由于開關控制信號移動的方向是由動態偽隨機碼決定的,也就是說模擬電路模塊中被打開或者被關閉的電流源或者電壓源的位置也是動態變化的,但由于使用了溫度計碼,不會出現大量的開關在同一時刻做出開啟或者關斷的情況,這樣的設計可以保證不僅所有的電源都能夠被動態平均使用,而且整個DAC 譯碼電路的動態性能也能得到提升。

5 仿真結果分析

將用ModelSim 編寫的基于DWA 算法的DAC 芯片譯碼電路的設計代碼和測試文件與Quartus II 相關聯,仿真出譯碼電路從輸入到輸出的時域波形(如圖8)和總體的硬件電路圖(如圖9 所示)。圖6 為m 序列發生器產生的偽隨機碼序列,可以看出序列中高低電平所占的比例大致相同,說明該序列具有一定的隨機性,且由于該序列可以決定開關控制信號的滾動方向,這樣一來可以保證在一個穩定范圍內,開關控制信號將動態平均地使用到每一個電源。圖8為溫度計碼生成模塊產生的溫度計碼的時域仿真波形,可以看出當輸入的五位二進制數值的大小加“1”或減“1”時,輸出的溫度計碼中“1”的個數增加或者減少一位,且“1”的個數是從低位到高位連續增加的,實現了溫度計碼的正確輸出。圖9 為動態平均模塊輸出完成權重平衡之后的開關控制信號,可以看到m 序列的值可以控制溫度計碼的移位,實現了基于DWA 算法的DAC 芯片譯碼電路設計。本實驗未涉及模擬電路模塊(等分壓或等分流電路)的設計。

圖8 溫度計碼模塊仿真結果

圖9 系統綜合及實現結果圖

使用Quartus II 的RTL Viewer 功能進行仿真,可以看到圖9 是仿真搭建的硬件電路圖,圖10 是該電路圖的時序仿真結果。

圖10 DAC 譯碼電路總體仿真結果

6 結語

本文主要介紹了基于DWA 算法的DAC 芯片譯碼電路的設計過程,首先根據DAC 譯碼電路的要求構建設計思路,因為傳統的二進制加權型譯碼電路具備結構簡單、占用版圖面積小的優點,思路清晰且易于實現,所以決定在該電路的設計基礎上進行缺點的優化。然后通過分析和對比,為了解決加權型譯碼電路由于技術限制所導致的工藝不匹配的問題,決定采用溫度計碼的方式設計譯碼電路,由于溫度計碼在編碼結構上的獨特性,這里用其作為開關控制信號,可以很好的解決在控制信號變化前后由于大量的電源頻繁開斷可能導致輸出信號出現毛刺的問題。最后基于DWA 算法的原理,以桶形移位器為基礎設計了動態平均模塊,實現了將以溫度計碼形式輸出的開關控制信號在偽隨機碼的控制下在一定范圍內循環滾動,達到了平均使用電流源的目的,同時也提升了DAC 的動態性能。

本電路在設計思路的基礎上編寫了Verilog 代碼,利用ModelSim 和Quartus II 的平臺進行了仿真。通過將仿真結果與設計思路進行對比以及對生成的模塊進行功能測試,邏輯功能基本得到了實現,實驗結果與預期值相符合,證明了仿真成功。