面向高性能眾核處理器的超頻DDR4訪存結構設計

高劍剛,李 川,鄭 浩,王彥輝,胡 晉

(1.國家并行計算機工程技術研究中心,北京 100190;2.江南計算技術研究所,江蘇 無錫 214083)

0 引 言

存儲系統是高性能計算機系統結構中的重要組成部分。國內超算系統神威·太湖之光[1]、天河2A[2]采用DDR3/4內存技術,接口速率2133 Mbps~2400 Mbps。國外超算系統Summit[3]、Sierra[3]采用處理器芯片DDR4與加速芯片HBM2[4](high-band width memory)的內存組合方式,DDR4接口速率2666 Mbps。TOP500排名第一的超級計算機Frontier[5]內存系統為DDR4和HBM2e,DDR4接口速率3200 Mbps。作為傳統存儲并行互連技術,DDR4在高性能計算機中應用廣泛。

DDR4應用于超算系統主要有兩種方式,一是標準內存條插裝[6],二是存儲顆粒嵌入PCB(printed circuit board)表面貼裝。嵌入式貼裝典型系統是神威·太湖之光[7],該方式可以釋放貼裝高度方向空間,也有助于減少由接插器件導致的信號畸變,但是,對DDR4訪存結構設計和信號完整性設計[8]要求很高。

業界關于DDR4的研究有訪存分析[9]、接口電路物理設計優化[10]、鏈路串擾分析[11,12]等,針對嵌入式互連結構[13]的研究偏少。在信號完整性問題分析中,DDR4地址組總線和數據組總線眼圖仿真較少聯合分析兩大類信號以及數據碼型對信號傳輸的影響[14,15]。本文以DDR4嵌入式表面貼裝應用為背景,設計了一種高密度串推結構,根據結構特點進一步提出了基于碼型的仿真分析方法。并對仿真發現的地址組信號概率性出錯問題進行了結構優化分析和測試驗證。

1 串推結構設計

DDR4信號可以分為命令地址控制信號(后文簡稱為地址組信號)和數據信號兩大類[16],以單端信號為主,只有時鐘信號和數據選通信號是差分方式。地址組信號經處理器驅動后,依次經過多片存儲顆粒,最后到達端接器件。數據信號采用點到點拓撲結構,即處理器與每片存儲顆粒直連,信號雙向傳輸。

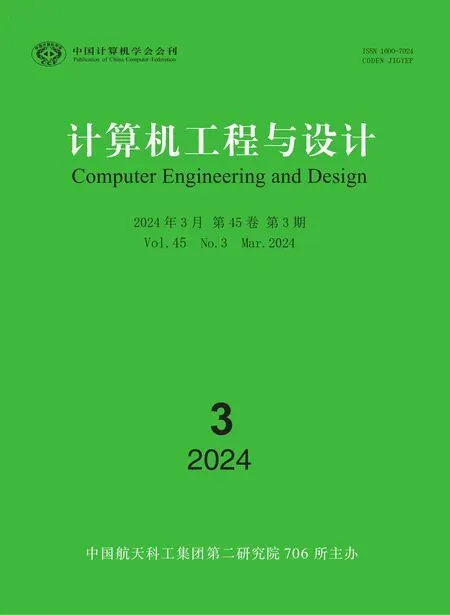

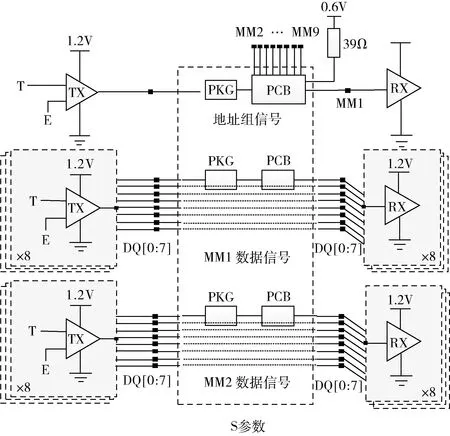

根據信號拓撲特點,針對高性能處理器高頻應用,即一套存儲控制器與9片存儲顆粒(8片信息存儲+1片傳輸校驗)互連,考慮高效利用板面布局空間,同時控制數據信號點到點互連長度,設計如圖1所示串推結構。

圖1 串推結構及管腳陣列俯視圖

在該串推結構中,地址信號從處理器出發,依次連接印制板上、下表面的存儲顆粒MM1和MM2、MM3和MM4……最后到達端接電阻R。印制板上、下表面存儲顆粒管腳陣列重合,以MM1和MM2的管腳俯視圖為例,MM1管腳A1至N1與MM2管腳A9至N9完全重合,管腳A2至N2與A8至N8重合,以此類推。同一地址信號在MM1和MM2之間存在兩種互連方式:單孔互連和雙孔互連。單孔互連結構中,信號通過同一個孔與兩片存儲顆粒信號管腳相連,共孔的管腳主要為兩個顆粒的第3列和第7列。因為3、7兩列管腳引盤至共孔,空間充足。雙孔互連結構中,信號先經過MM1和MM2中靠近處理器一側的引盤孔,再印制線互連至遠離處理器一側的引盤孔。圖中虛線把存儲顆粒管腳分為上下兩個區域,顆粒上半部分是數據組信號管腳(DQ標識區域),顆粒下半部分是地址組信號管腳(AC標識區域),地址組和數據組兩類信號管腳在空間上無交疊。

采用該串推結構,存儲顆粒在印制板兩側面對面貼裝,可以提高布局密度,同時有效控制數據信號布線距離。由于地址組信號引盤孔陣列與數據組信號引盤孔陣列無交疊,地址組與數據組可以實現同層無交叉布線,布線密度大幅提升。

根據該結構進行布局布線設計,9片存儲顆粒數據組線長各顆粒組等長,最長線組為180 mm。地址組信號以時鐘信號為目標進行等長設計,處理器至到首片顆粒段線長等長。印制板板厚3.5 mm,信號孔孔徑0.25 mm,盤徑0.45 mm,隔離盤大小為0.65 mm,信號孔連接盤只在印制板兩個表面和布線層保留。

2 碼型仿真

2.1 傳統總線仿真

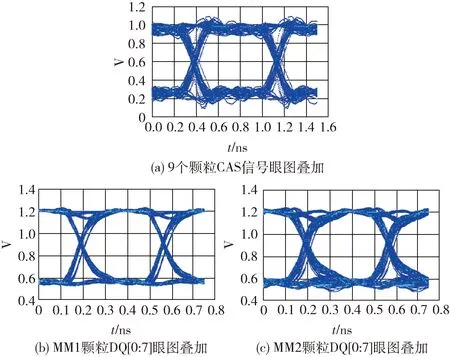

DDR4總線設計仿真分析中,常用做法是:基于三維電磁場仿真分析軟件建模提取包括封裝段和PCB段的地址總線、數據總線物理通道的散射參數(S參數)模型,然后在電路仿真軟件中搭建包含通道S參數、存儲控制接口電路IBIS(input/output buffer informational specifation)模型以及存儲顆粒接口電路IBIS模型的鏈路拓撲,并根據數據地址信號類別以及信號速率設置恰當的激勵參數、端接參數和分析求解參數,最后在接收端觀察信號仿真眼圖是否符合規范要求。

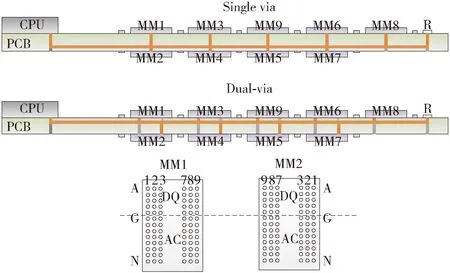

圖2為DDR4總線鏈路仿真拓撲,圖中TX表示地址組信號或數據組信號的發送端接口電路,RX表示地址組信號或數據組信號的接收端接口電路。T為發送端加載的激勵波形,E為發送端接口電路使能控制電平,PKG和PCB分別代表封裝段物理設計和印制板段物理設計,可以是物理結構參數也可以是表征傳輸特性的S參數。在地址組信號仿真中,PCB段的S參數體現了地址組信號的串推特性,信號通過封裝管腳進入PCB后,可以在9個不同存儲顆粒位置接收觀測,同時采用片外端接方式上拉至0.6 V。數據信號鏈路仿真通常以存儲顆粒的8個數據位為一組,每個數據位分別添加發送端電路接口模型和接收端電路接口模型。組內8個數據信號在發送端同時使能并加載一定速率的偽隨機激勵波型,在接收端觀察組內串擾狀態下的鏈路眼圖質量。

圖2 DDR4總線鏈路仿真拓撲

圖3 串推結構設計總線仿真結果

2.2 碼型分析仿真

傳統的總線仿真結果顯示設計裕量充足,但不足以化解該結構的設計風險。

結構中PCB板的厚度約為常規內存條的2.5倍,信號孔長度即是內存條信號孔的2.5倍。由于信號孔的寄生電感與信號孔長度強相關[16],如式(1)所示

(1)

式中:Lvia為孔寄生電感,單位nH。h為孔長,d為孔直徑。孔長度增加,寄生電感隨之增加。

相互靠近的有電流通過的電感器件,電流變化與電感之間互感的疊加作用,會有額外的電壓產生,如式(2)所示

(2)

式中:L為信號孔之間的互感,i為通過信號孔的電流。

考慮到數據信號速率高,信號翻轉時電流變化較大,地址組信號又是多負載多分支結構,而且地址組信號接收端沒有片上端接,所以數據信號翻轉對地址信號的影響是該結構面臨的不確定因素,而傳統總線仿真不能排除該不確定因素的影響。

為了充分化解設計風險,提出碼型分析方法。選擇離終端上拉電阻較遠的MM1、MM2存儲顆粒和地址組信號中空閑度相對小的CAS信號進行詳細分析。

建立印制板兩側面對面貼裝顆粒兩組數據通道和地址信號物理關聯鏈路,通過改變MM1顆粒和MM2顆粒數據信號鏈路的發送端激勵波形表征不同速率和碼型的數據信號翻轉特性,采用如圖4所示的碼型分析鏈路拓撲,分析地址信號采樣正確率是否受到影響。

圖4 碼型分析拓撲

2.3 靜態碼型仿真結果

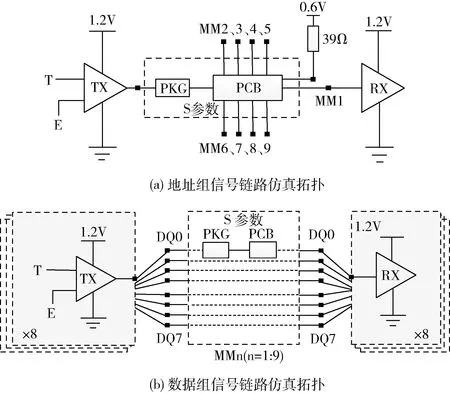

靜態碼型是指數據信號無翻轉電流,這時仿真鏈路中MM1和MM2的數據信號鏈路無激勵波形加載,CAS仿真結果參考傳統總線中的仿真結果。

根據DDR4存儲顆粒數據手冊要求,數據速率2666 Mbps~3200 Mbps對應的單端地址組信號的直流電平要求為:高電平大于VREF+65 mv,低電平小于VREF-65 mv;交流電平要求為:高電平大于VREF+90 mv,低電平小于VREF-90 mv。其中,VREF為參考電壓,通常為0.6 V。在參考電壓處的建立/保持時序根據速率不等,最小為145 ps~130 ps。

從圖3(a)CAS信號9個顆粒位置的疊加眼圖來看,在數據鏈路為靜態碼型情況下,信號內眼圖的高、低電平距0.6 V有接近300 mv的電壓差,即約210 mv的電平裕量,在參考電壓0.6 V的時序寬度遠大于290 ps。而實際工作時,每個顆粒的CAS信號采樣電平和時序裕量是按照單顆粒的信號眼圖來判別,而不是9個位置的疊加眼圖,所以采樣裕量大于等于眼圖所示裕量。由分析可以推測:靜態數據碼型環境下的CAS信號采樣裕量充足,無識別出錯可能。

2.4 同向翻轉碼型仿真結果

同向翻轉分為同向1010翻轉和同向0101翻轉。同向1010翻轉是指MM1和MM2兩個顆粒的兩組數據信號同一時刻翻轉方向一致,碼型為“10101010”,數據速率為2666 Mbps。同向0101翻轉對應數據翻轉速率2666 Mbps不變,碼型為“01010101”。

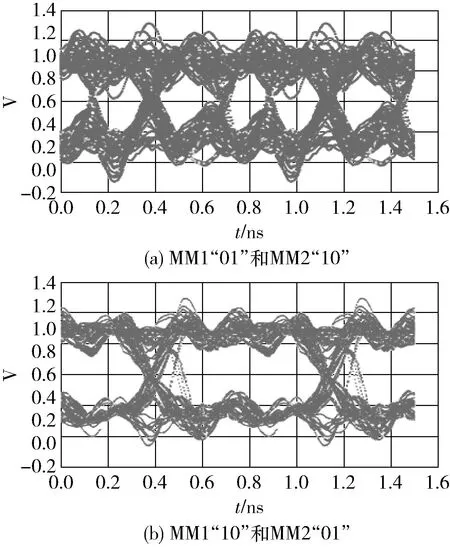

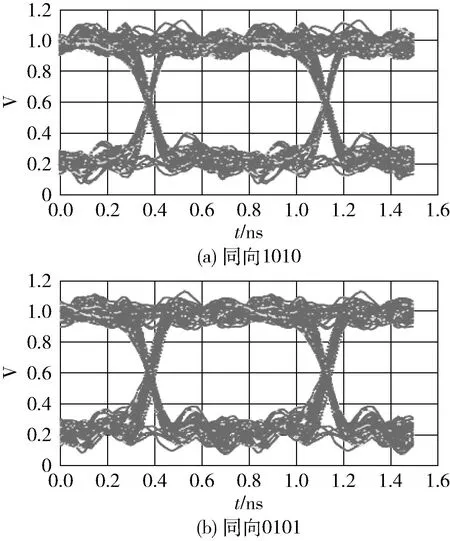

在CAS鏈路添加與靜態碼型鏈路相同的發送、接收端電路模型參數,兩種同向翻轉對應的9顆粒位置CAS信號疊加眼圖如圖5所示,圖5(a)為同向1010翻轉對應眼圖,圖5(b)為同向0101翻轉對應眼圖。

根據圖5結果,在兩組數據信號同向翻轉時,CAS信號疊加眼圖顯示的電平窗口與靜態碼型相比,都有一定幅度的縮小。1010同向翻轉對應的電平裕量略小,且交流輸入低電平裕量接近于0。9個顆粒位置有實際采樣電平裕量為零的可能,但不能確定與功能性信號識別出錯強相關。

2.5 反向翻轉碼型仿真結果

反向翻轉是指MM1顆粒和MM2顆粒的數據信號在同一時刻翻轉方向相反,也分兩種情況進行分析。第一種情況:MM1顆粒數據信號碼型“01010101”,MM2顆粒數據信號碼型“10101010”,簡稱MM1“01”和MM2“10”,數據翻轉速率2666 Mbps。第二種情況:數據翻轉速率2666 Mbps不變,調換MM1和MM2兩個顆粒的數據信號碼型,MM1顆粒數據信號碼型“10101010”,MM2顆粒數據組信號碼型“01010101”,簡稱為MM1“10”和MM2“01”。

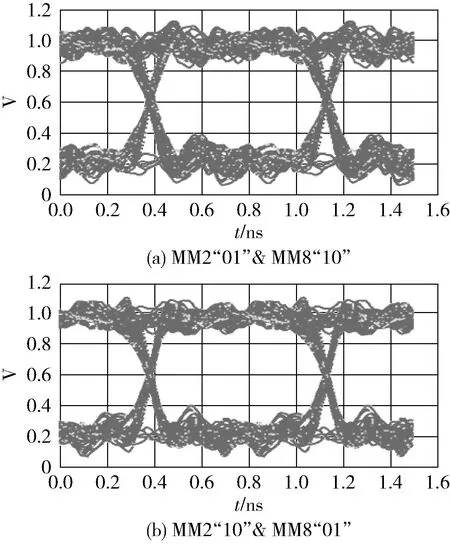

在CAS鏈路添加與靜態碼型鏈路相同的發送、接收端電路模型參數,兩種反向翻轉對應的9顆粒位置CAS信號疊加眼圖如圖6所示,圖6(a)為MM1“01”和MM2“10”對應眼圖,圖6(b)為MM1“10”和MM2“01”對應眼圖。

圖6 反向翻轉對應CAS信號疊加眼圖

根據圖6結果,MM1“01”和MM2“10”對應的CAS信號疊加眼圖高低電平交叉,無論是電平還是時序都達不到手冊要求,信號極有可能出現功能性識別錯。MM1“10”和MM2“01”對應的CAS信號疊加眼圖顯示采樣時序裕量充足,電平裕量略小。

進一步分析MM1“01”和MM2“10”對應的CAS信號可能出錯的顆粒位置,圖7為該反向翻轉環境4個顆粒位置的CAS波形。

圖7 MM1“01”和MM2“10”對應四顆粒CAS信號波形

從圖7這4個顆粒位置CAS波形可以看出,MM1和MM3的CAS波形反射幅度大,高、低平穩電平處的反射方向都指向參考電平,且超出了接口電平要求,在這兩個顆粒位置易出現信號識別錯。MM4顆粒高電平在較寬的采樣時序范圍內也存在識別出錯可能。

經分析,靜態碼型、兩種同向翻轉和兩種反向翻轉碼型對CAS信號有不同程度影響。靜態和同向翻轉對CAS信號采樣裕量影響較小,反向翻轉會導致CAS波形產生明顯畸變。反向翻轉中的特定碼型,即MM1“01010101”和MM2“10101010”,使得CAS信號在兩個以上顆粒位置出現高電平和低電平識別出錯。也就是說,當印制板上、下表面對貼的兩個顆粒的數據信號反向翻轉時,命令/地址信號會在多個顆粒位置出現電平識別出錯。

從布局布線設計來看,CAS信號線與MM1和MM2數據信號線處于不同信號層,同層信號線間串擾可能性小。在縱向上,兩類信號都經過了板厚較大的通孔,結合前文對孔間干擾的分析,減小孔間耦合成為優化設計的方向。

3 優化設計及仿真

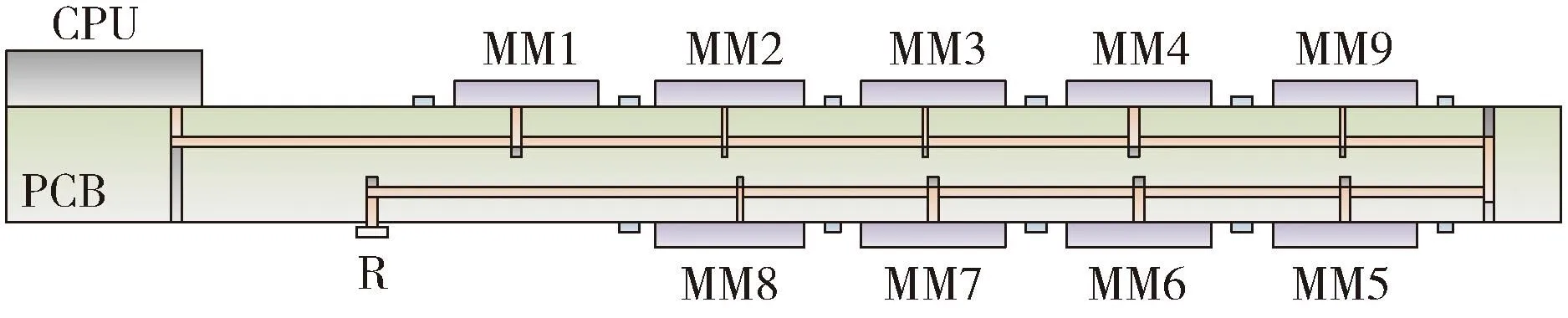

3.1 雙盲折疊串推結構

從優化通孔串擾的目的出發,設計如圖8所示的折疊串推結構。該結構與圖1的串推結構相比,地址組信號串推順序有了明顯變化。地址組信號從處理器出發,依次經過MM1至MM4、MM9校驗顆粒、MM5至MM8,最后到達端接器件R。除此之外,PCB表面正、反貼顆粒的引盤孔在PCB厚度方向上無重疊。該結構增加了上下表面顆粒信號引盤孔的物理隔離距離,并且不改變原有的布局密度以及布線距離。

圖8 折疊串推結構

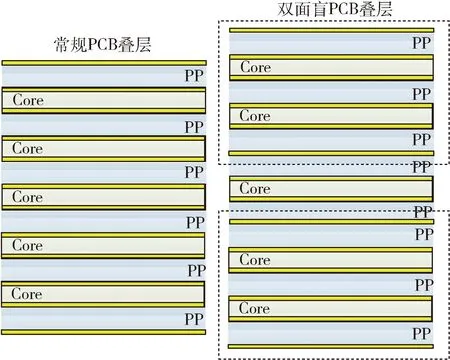

常規PCB疊層工藝無法實現對貼顆粒的引盤孔陣列物理隔離,因此提出一種雙面盲PCB疊層結構,兩種疊層設計對比如圖9所示。

圖9 常規PCB工藝VS上面盲PCB工藝

印制板通常由基材、半固化片、表面銅箔組成。基材如圖9中Core所示,是材料廠商提供的兩面具有一定光滑度的銅箔和夾心介質材料組合體;半固化片如圖中PP所示,是基材間填充的介質材料。常規印制板工藝中,表面銅箔位于PCB的兩個表面。由布線和供電需求確定基材、半固化片的規格和數量后,一次層壓成型再進行整板鉆孔處理是常規印制板工藝特點。

在雙面盲PCB疊層中,除了印制板表面銅箔外,在基材中間也有兩層銅箔,這兩層銅箔在虛線框的區域內分別起到了下表面銅箔和上表面銅箔的作用。雙面盲PCB疊層工藝共有3次層壓,第一次和第二次分別對兩個虛線框內的Core、PP和表面銅箔進行層壓,第三次對從上至下整個區域進行層壓。盲孔的實現依靠前兩次層壓之后的鉆孔工藝,對于虛線框內的結構,第一、二次層壓之后的鉆孔相當于常規工藝,第三次層壓之后,之前的通孔結構成為盲孔。整板的通孔設計需求在第三次層壓之后鉆孔實現,不受前兩次層壓影響。

雙面盲結構中的基材數量可以根據布線需求進行調整,由于不受激光盲孔鉆孔深度的限制,可以實現多層盲孔互連。兩個虛線框中間區域基材,可以用作電源供電層,電源層的基材數量和厚度不影響上盲和下盲區域的鉆孔厚徑比。

根據折疊串推結構和雙面盲疊層進行設計優化,盲孔孔徑可以由0.25 mm減小至0.15 mm,減小幅度40%,得益于鉆孔厚度的大幅減小。

針對優化設計版本進行鏈路仿真分析,優化結構中的MM2和MM8顆粒分布位于印制板的上、下表面,Pin坐標重合,因此選擇MM2和MM8顆粒的數據信號和地址信號CAS的進行碼型干擾分析。

3.2 2666 Mbps仿真結果

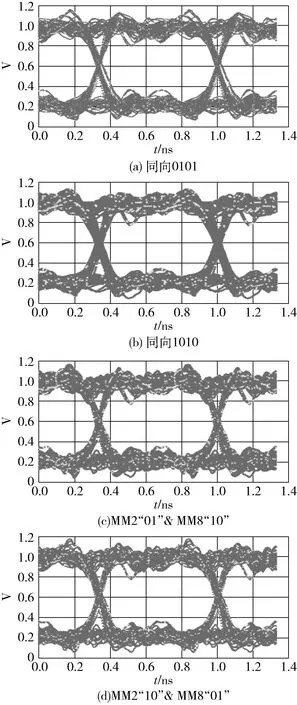

MM2和MM8數據信號在2666 Mbps速率下同向翻轉時,CAS信號疊加眼圖如圖10所示。圖10(a)為同向1010翻轉對應眼圖,圖10(b)為同向0101翻轉對應眼圖。

圖10 2666 Mbps同向翻轉對應CAS疊加眼圖

MM2和MM8數據信號在2666 Mbps速率下反向翻轉時,CAS信號疊加眼圖如圖11所示。圖11(a)為MM2“01”和MM8“10”對應眼圖,圖11(b)為MM2“10”和MM8“01”對應眼圖。

圖11 2666 Mbps反向翻轉對應CAS疊加眼圖

優化設計后同向翻轉和反向翻轉疊加眼圖與優化前相比,電平裕量有了顯著提高,采樣電平和時序裕量充足,信號功能性識別出錯概率極小。

3.3 3000 Mbps仿真結果

把MM2和MM8的數據信號速率從2666 Mbps提升至3000 Mbps,觀察CAS疊加眼圖。兩種同向翻轉和反向翻轉對應的CAS疊加眼圖如圖12所示。

圖12 3000 Mbps同向和反向翻轉對應CAS疊加眼圖

根據圖12的眼圖結果,即使數據速率大幅提升,CAS眼圖的電平裕量和時序裕量仍然充足,信號功能性識別出錯概率小。雙面盲折疊串推結構相比優化前的通孔串推結構,在高速率數據碼型干擾環境下CAS信號質量大幅提升,識別出錯問題得以解決。另外,優化結構中的數據信號由于孔徑變小,孔分支長度減小,信號質量也會得到一定程度的改善。

4 應用測試

優化后的雙面盲折疊串推結構應用于神威E級原型機運算板,在處理器的功能調試和運算板的工程測試中,DDR4信號傳輸性能和訪存功能得到全面的測試驗證。

DDR4測試中,包括讀/寫訓練測試、課題訪存功能測試和信號波形測試。讀/寫訓練測試是指在與讀/寫速率適配的時序參數條件下,處理器與存儲顆粒之前通過一系列訓練步驟,建立可存可取的讀操作與寫操作運行環境。訓練步驟包括初始化、讀使能、數據選通與時鐘邊沿對齊、組內數據去偏斜等。課題訪存功能測試與memtest原理一致,通過針對顆粒存儲空間的大量讀/寫操作,統計內存中可能的出錯位置及操作項,測試內存工作的穩定性。課題功能包括地址遍歷、連讀連寫、不同碼型數據的讀寫測試等。信號波形測試,即選擇少量待測信號,焊接測試夾具,連接實時示波器進行實時波形捕獲,確認信號速率和波形質量。由于時鐘信號可以直觀反映數據速率,同一顆粒的數據選通信號和數據信號波形疊加可以識別捕獲波形對應操作是讀還是寫,所以DDR4波形測試中這3種信號較常見。

存儲顆粒標稱速率為2666 Mbps,在標稱速率下,系統512個處理器所有DDR4存儲互連通路中讀/寫訓練全部通過,重復運行各類內存穩定性測試程序,包括長時間拷機課題,無報錯。數據速率提升至3000 Mbps時,結果一致,讀/寫訓練全部通過,課題運行仍然無報錯。

3000 Mbps運行時讀/寫測試波形如圖13所示。這里讀/寫操作的數據選通信號波形都采用兩個時鐘周期的導沿模式,導沿編碼為1110,由于數據選通信號是差分信號,導沿之后的采樣區間擺幅是數據信號的兩倍。兩幅圖中,導沿之后擺幅較大的是數據選通信號波形,無導沿且擺幅較小的是數據信號波形。

圖13 3000 Mbps讀、寫數據和時鐘波形

圖13(a)中,數據選通信號與數據信號在高低電平切換處無相位差,為讀操作波形。圖13(b)中,數據選通信號與數據信號在高地電平切換處存在半個數據位寬的相位差,為寫操作波形。兩圖中,數據選通信號和數據信號疊加波形下方是周期性的時鐘信號波形,時鐘頻率1.50 GHz,可知數據速率為3000 Mbps。從讀、寫操作數據波形來看,數據信號在超頻條件下傳輸質量良好。

5 結束語

本文從多路DDR4存儲顆粒嵌入式工程應用出發,設計了一種高密度DDR4串推結構,提出基于不同激勵碼型的仿真分析方法,分析該結構中數據組信號特定翻轉碼型影響地址組信號識別問題,進一步優化設計了基于雙面盲疊層結構的折疊串推結構,有效解決了該問題。實測波形顯示,該結構超頻條件下的DDR4波形質量良好,并且具有較高的系統訪存功穩定性。目前已推廣應用于神威E級原型機等多臺套大型計算裝備,技術效益良好。