航空用高速連接器信號(hào)反射抑制與優(yōu)化設(shè)計(jì)

駱燕燕,楊碩,*,潘曉松,趙緒懷,張莉

1.河北工業(yè)大學(xué) 電氣工程學(xué)院,天津 300130

2.國網(wǎng)重慶市長壽供電分公司,重慶 401220

3.中壹發(fā)展八五零電子有限公司,石家莊 050000

4.石家莊市科恒電子有限公司,石家莊 050000

隨著信息技術(shù)的快速發(fā)展,高速連接器已經(jīng)成為解決設(shè)備間高速互聯(lián)問題的關(guān)鍵元件[1-2],廣泛應(yīng)用于軌道交通、航空航天及醫(yī)療器械等領(lǐng)域。在航空領(lǐng)域中,高速連接器是現(xiàn)代飛機(jī)電氣線路互聯(lián)系統(tǒng)(Electrical Wiring Interconnection System,EWIS)的必備元件,擔(dān)負(fù)著在機(jī)載電氣電子設(shè)備間傳遞高速信號(hào)、傳輸電能及電磁能量的重任[3]。

高速連接器在傳遞信號(hào)時(shí),受內(nèi)部或外部環(huán)境影響,容易出現(xiàn)信號(hào)完整性問題。信號(hào)完整性問題是指由互連線引起的一切信號(hào)質(zhì)量問題[4],它與互聯(lián)系統(tǒng)中的傳輸線效應(yīng)、電磁干擾以及寄生參數(shù)有關(guān)[5]。高速連接器的信號(hào)完整性問題包括信號(hào)反射、信號(hào)間串?dāng)_及信號(hào)衰減等[6],其中信號(hào)反射會(huì)引起信號(hào)過沖、信號(hào)振鈴等問題[7],對(duì)信號(hào)質(zhì)量影響較大且發(fā)生頻率較高。了解信號(hào)反射的成因及影響因素,有助于在工程中快速找到產(chǎn)生問題的原因和位置[8],具有工程意義。

為了探究信號(hào)反射問題的產(chǎn)生原因及影響因素,國內(nèi)外的研究重點(diǎn)是根據(jù)其影響因素對(duì)高速連接器進(jìn)行優(yōu)化設(shè)計(jì),主要包括三方面:①優(yōu)化高速連接器的結(jié)構(gòu)。Zhou等[9]研究發(fā)現(xiàn)損傷層對(duì)回波損耗有影響,提出了一種不影響質(zhì)量的消除損傷層的化學(xué)處理方法;Wang等[10]發(fā)現(xiàn)信號(hào)反射問題與連接器表面的腐蝕膜有關(guān);尹治宇[11]和張志遠(yuǎn)[12]通過優(yōu)化連接器插針與PCB板連接處的結(jié)構(gòu)、焊點(diǎn)的大小、公頭與母座接觸部分及插針彎折處結(jié)構(gòu),改善了信號(hào)反射問題;Wu等[13]利用襯底預(yù)埋線,將雙軸微纜連接到封裝邊緣,對(duì)信號(hào)反射問題進(jìn)行了優(yōu)化。② 優(yōu)化介質(zhì)材料參數(shù)。黃波[14]提出優(yōu)化隔離各差分對(duì)的介質(zhì)夾層厚度對(duì)特性阻抗進(jìn)行改善;高鵬宇[15]通過仿真發(fā)現(xiàn),選用介電常數(shù)小的材料能優(yōu)化連接器的差分阻抗和插入損耗。③Lundquist[16]提出優(yōu)化連接器長度來改善信號(hào)反射問題;徐曉丹[17]利用添加匹配阻抗的方法對(duì)信號(hào)反射問題進(jìn)行了優(yōu)化;Ben[18]利用在信號(hào)孔周圍增加接地孔的方法對(duì)連接器進(jìn)行了優(yōu)化。

上述對(duì)于高速連接器信號(hào)反射的優(yōu)化設(shè)計(jì)的研究,集中于對(duì)連接器的某一內(nèi)部結(jié)構(gòu)、連接器與外部環(huán)境交界處的結(jié)構(gòu)及介電材料的參數(shù)等進(jìn)行單一優(yōu)化[19-20],而針對(duì)這些因素進(jìn)行綜合考慮的研究較少。在實(shí)際工程中,必須綜合考慮各影響因素的參數(shù)對(duì)信號(hào)反射的影響,使各方面達(dá)到平衡。本文在設(shè)計(jì)仿真方案時(shí),較為全面地考慮了影響信號(hào)反射問題的因素,從頻域和時(shí)域兩個(gè)角度分析信號(hào)反射問題,提出了一種綜合考慮各方面影響因素的優(yōu)化設(shè)計(jì)方法,并且通過測(cè)試實(shí)驗(yàn)證實(shí)了其有效性。

1 信號(hào)反射問題成因

1.1 信號(hào)傳輸過程

高速連接器的信號(hào)傳輸速率通常在10 Gbps及以上,所以傳統(tǒng)的電路理論已不再適用,必須利用分布參數(shù)電路進(jìn)行分析[21],并把信號(hào)從發(fā)射端到接收端的過程,理解為需要一段時(shí)間的“動(dòng)態(tài)”過程[22]。本文在分析信號(hào)傳輸問題時(shí),采用電磁波傳播的理論,使用傳輸線模型對(duì)高速連接器的每對(duì)接觸件進(jìn)行簡化。

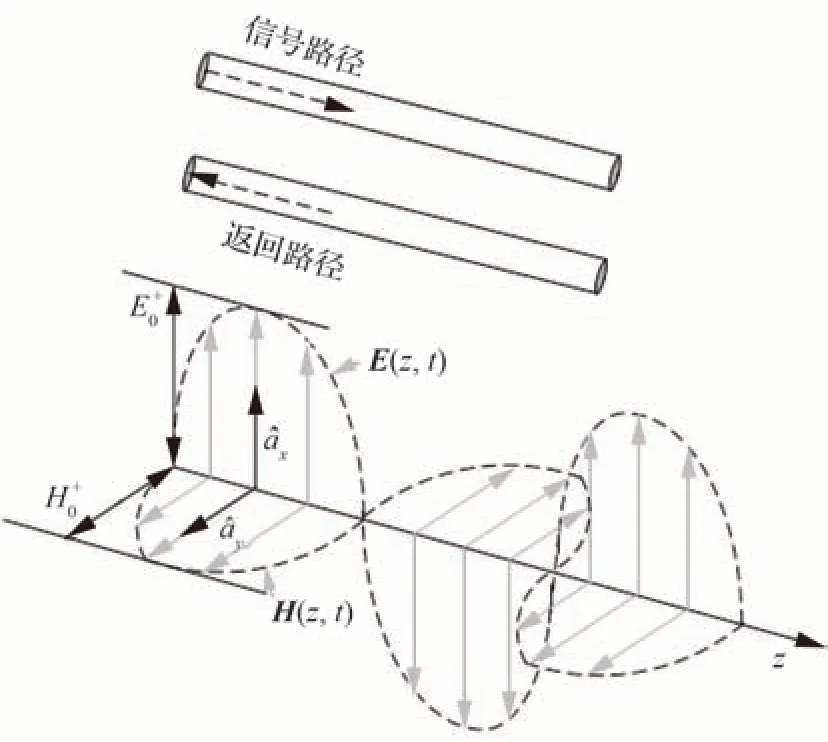

簡單的傳輸線模型由2 條有一定長度的平行導(dǎo)線組成,其中一條為“信號(hào)路徑”,另一條為“返回路徑”[23]。信號(hào)以電磁波的形式在傳輸線上傳輸,在傳輸?shù)哪骋粫r(shí)刻,變化的電場和磁場只存在于傳輸線上的某一區(qū)域,這一區(qū)域隨時(shí)間不斷向前推進(jìn),如圖1 所示。

圖1 沿空間分布的電場和磁場Fig.1 Electric and magnetic fields distributed along space

信號(hào)在傳輸線上處于不同的位置,可能會(huì)感受到不一樣的“環(huán)境”,傳輸線上某處“環(huán)境”的變化,如線徑改變,就會(huì)影響電場和磁場的向前推進(jìn),引起信號(hào)反射。

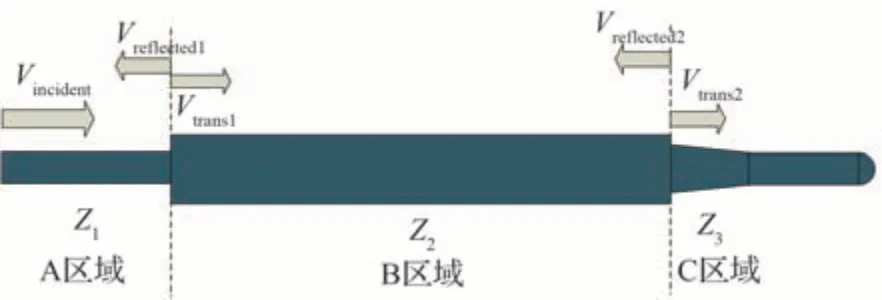

圖2 為接觸件插針示意圖,其可分為A、B、C 3 個(gè)區(qū)域,區(qū)域交界處電壓和電流的關(guān)系為

圖2 高速連接器一個(gè)插針的示意圖Fig.2 Schematic diagram of one pin of the high-speed connector

式中:Vincident為入射電壓;Vreflected為反射電壓;Vtrans為傳輸電壓;Iincident為輸入電流;Ireflected為反射電流;Itrans為傳輸電流。

為了表示信號(hào)反射對(duì)信號(hào)傳輸性能的影響程度,引入反射系數(shù),其等于反射信號(hào)和入射信號(hào)的比值[24],通過進(jìn)一步推導(dǎo),反射系數(shù)為相鄰2 個(gè)區(qū)域瞬時(shí)阻抗的差值與和的比值,表達(dá)式為

式中:ρ 為反射系數(shù);Z 為瞬時(shí)阻抗。

由式(2)可以看出,相鄰2 個(gè)區(qū)域瞬時(shí)阻抗的差值越大,反射系數(shù)絕對(duì)值越大,信號(hào)反射問題越嚴(yán)重;當(dāng)相鄰2 個(gè)區(qū)域瞬時(shí)阻抗的差值為零時(shí),反射系數(shù)為零,此時(shí)不存在信號(hào)反射問題,故傳輸線的阻抗不連續(xù)是產(chǎn)生信號(hào)反射問題的重要且關(guān)鍵原因。

1.2 傳輸線阻抗的影響因素

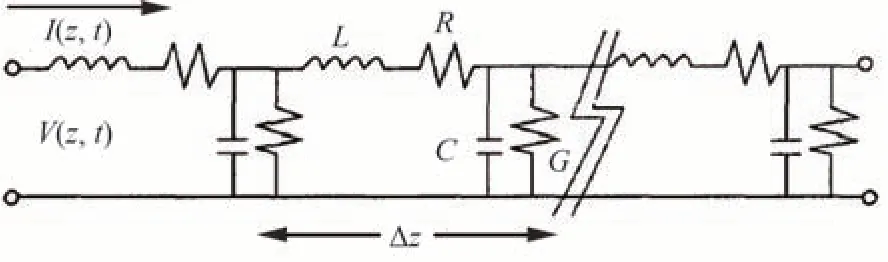

在高頻電路中,傳輸線模型是連續(xù)分布式模型[25],可用多 段RLCG 模型描述[26],如 圖3所示。

圖3 傳輸線的RLCG 模型Fig.3 RLCG model for transmission lines

在應(yīng)用RLCG 模型理論時(shí),傳輸線被分解為無數(shù)個(gè)集總電路元件Δz,為了更接近傳輸線的實(shí)際情況,令Δz 無限趨近于零。

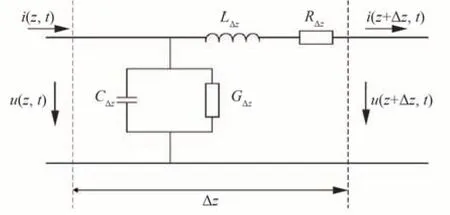

圖4 為集總參數(shù)等效電路模型,其中L 為單位長度的分布串聯(lián)電感,R 為單位長度的分布串聯(lián)電阻,C 為單位長度的分布并聯(lián)電容,G 為單位長度的并聯(lián)電導(dǎo)。

圖4 集總參數(shù)等效電路模型Fig.4 Model of collective parameter equivalent circuit

假定集總參數(shù)模型中每個(gè)微元段Δz 的特性相同,設(shè)Δz 起點(diǎn)的電壓和電流分別為u(z,t)和i(z,t),終點(diǎn)處的電壓和電流分別為u(z+Δz,t)和i(z+Δz,t)。

根據(jù)基爾霍夫電壓定律(Kirchoff Voltage Laws,KVL)和基爾霍夫電流定律(Kirchoff Current Laws,KCL)可列出方程為

令Δz→0,取極限并在兩邊同時(shí)除以Δz,得到的微分方程為

電報(bào)方程是準(zhǔn)確描述傳輸線RLCG 模型的微分方程,是有關(guān)傳輸線阻抗的重要方程。根據(jù)式(4)推導(dǎo)出電報(bào)方程為

式中:V 為傳輸線的電壓降;I 為傳輸線的電流;x為傳輸線長度;t 為時(shí)間。

電報(bào)方程的解為

式中:γ 為傳輸線的復(fù)傳播常數(shù);Z0為傳輸線的特性阻抗。

γ 可以表示為

式中:α為衰減常數(shù),在均勻傳輸 線中,α=0;β為相位常數(shù),與電磁波在介質(zhì)中的傳播速度有關(guān)。

假設(shè)電壓在一條無限長的傳輸線上傳播且電壓已知,將電壓微分后代入電報(bào)方程中求解電流,表達(dá)式為

由阻抗的定義可知,均勻傳輸線的特性阻抗Z0為電壓V(x)與電流I(x)的比值,即

由此可得,在信號(hào)傳輸過程中,特性阻抗與單位長度電感值呈正相關(guān),與單位長度電容值呈負(fù)相關(guān)。因此,任何影響電感值和電容值的因素都會(huì)對(duì)均勻傳輸線的特性阻抗產(chǎn)生影響。

單位長度分布并聯(lián)電容C 可表示為

式中:ε 為電容的相對(duì)介電常數(shù);s 為對(duì)應(yīng)的板面積;k 為靜電力常量;d 為對(duì)應(yīng)的板間距。

根據(jù)式(9)和式(10)可知,特性阻抗與材料特性、電介質(zhì)介電常數(shù)和單位長度電容量有關(guān),與傳輸線的長度無關(guān)。在實(shí)際工程中,線寬變化、路徑彎曲、過孔及器件引腳等都是常見的引發(fā)阻抗變化的因素,都有可能導(dǎo)致高速連接器的信號(hào)反射問題。

2 信號(hào)反射問題的表征參數(shù)

2.1 S 參數(shù)(散射參數(shù))

S 參數(shù)可用來分析連接器特性[27],信號(hào)經(jīng)過高速連接器產(chǎn)生的反射、串?dāng)_和衰減都可用S 參數(shù)來表征。S 參數(shù)可使用矩陣表示為

矩陣中每個(gè)S 參數(shù)的定義為

式中:i 為檢測(cè)端口;j 為入射端口。當(dāng)需要測(cè)量信號(hào)反射特性時(shí),令i=j 即可。

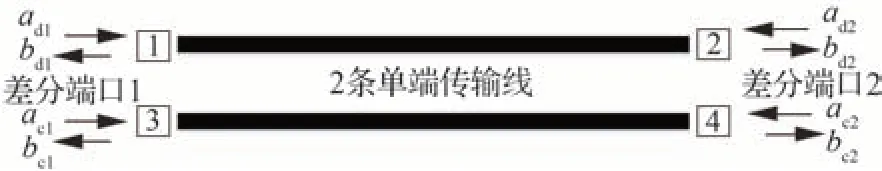

圖5 為高速連接器接觸件的差分二端口網(wǎng)絡(luò),定義a1和a2為差分二端口網(wǎng)絡(luò)的入射波參量,b1和b2為差分二端口網(wǎng)絡(luò)的反射波參量,其中c 表示共模信號(hào),d 表示差模信號(hào)。

圖5 接觸件差分對(duì)的差分二端口網(wǎng)絡(luò)示意圖Fig.5 Schematic diagram of a differential two-port network with differential pairs of contacts

差分對(duì)的S 參數(shù)可用混合S 參數(shù)矩陣進(jìn)行表示,高速連接器差分二端口網(wǎng)絡(luò)混合S 參數(shù)可定義為

式(14)為高速連接器差分二端口網(wǎng)絡(luò)混合S參數(shù)矩陣,為了便于分析,對(duì)該矩陣進(jìn)行拆分,理想差分網(wǎng)絡(luò)的左下角和右上角的元素均為零。

混合S 參數(shù)矩陣的左上角元素反應(yīng)的是差分二端口的差模傳輸特性,常用來表征信號(hào)在高速連接器傳輸過程中的信號(hào)反射和信號(hào)損耗。本文選取Sdd11和Sdd22表征信號(hào)能量被反射回入射端的量,即信號(hào)反射現(xiàn)象。Sdd11和Sdd22為信號(hào)在傳輸過程中的回波損耗,此外,還有表征信號(hào)串?dāng)_、信號(hào)衰減等問題的S 參數(shù),如插入損耗、近遠(yuǎn)端串?dāng)_等。

2.2 差分阻抗

盡管回波損耗包含了傳輸線互聯(lián)時(shí)的所有反射信息,但并不能直觀反映出現(xiàn)阻抗不連續(xù)的具體位置以及阻抗的變化幅度。差分阻抗在一定程度上可用于信號(hào)反射問題在時(shí)域內(nèi)的分析,有助于在工程中查明阻抗突變的位置及阻抗變化幅度。

差分阻抗是2 個(gè)單端奇模信號(hào)在差分對(duì)中傳遞時(shí)感受到的阻抗。所謂奇模信號(hào),是指幅度相同、相位相反的信號(hào),單端奇模信號(hào)在傳遞時(shí)感受到的阻抗為奇模阻抗。差分阻抗是奇模阻抗的2倍,表達(dá)式為

式中:Zdiff為差分阻抗;Zodd為奇模阻抗。

通過以上理論推導(dǎo)可知,回波損耗和差分阻抗可視作頻域和時(shí)域內(nèi)表征信號(hào)反射問題的參數(shù)。從頻域和時(shí)域兩方面分析信號(hào)完整性問題,會(huì)使問題更加清晰。

本文通過分析高速連接器回波損耗和差分阻抗在優(yōu)化量參數(shù)變化下的變化規(guī)律,來研究其信號(hào)反射問題。

3 原模型仿真結(jié)果分析

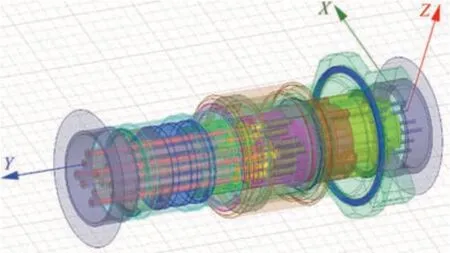

本文選取一款航空航天用的圓形高速連接器作為研究對(duì)象,使用HFSS 軟件對(duì)高速連接器的信號(hào)反射問題進(jìn)行仿真研究,利用有限元方法求解高速連接器的麥克斯韋方程組。

首先,在HFSS 中建立1∶1 的高速連接器三維模型,如圖6 所示。其次,設(shè)置模型各部分的材料屬性。再次,設(shè)置模型的求解類型、邊界條件、端口激勵(lì)、求解頻率和掃頻范圍。最后,檢查所有設(shè)置,無誤后運(yùn)行仿真。由仿真得到原模型的差分阻抗、回波損耗、插入損耗、近端串?dāng)_和遠(yuǎn)端串?dāng)_等參數(shù)的變化曲線。

圖6 高速連接器三維模型Fig.6 3D Model of high speed connector

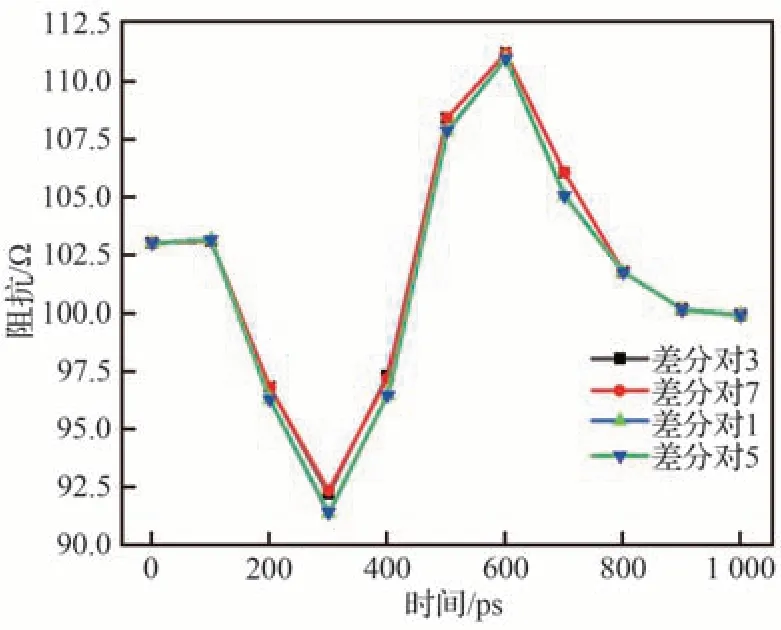

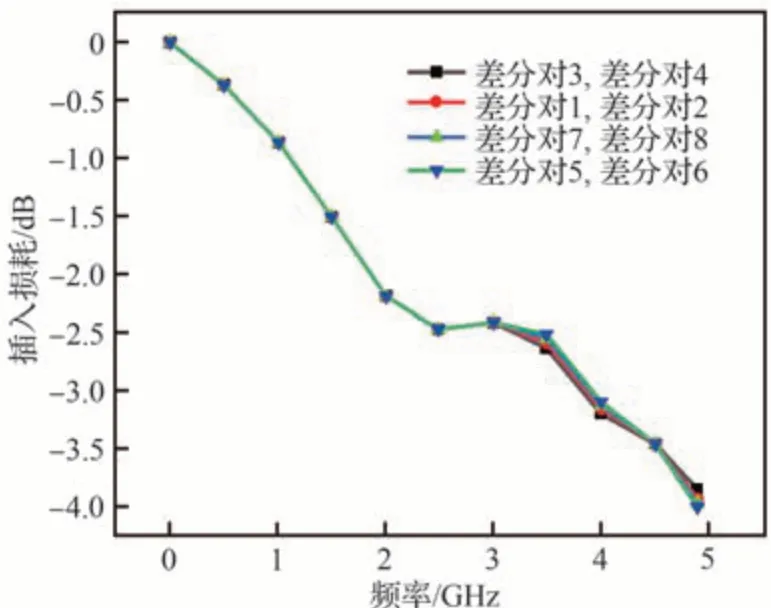

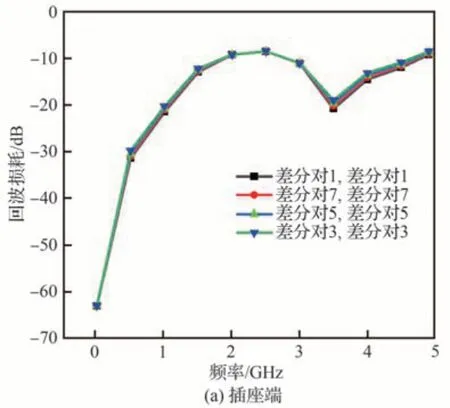

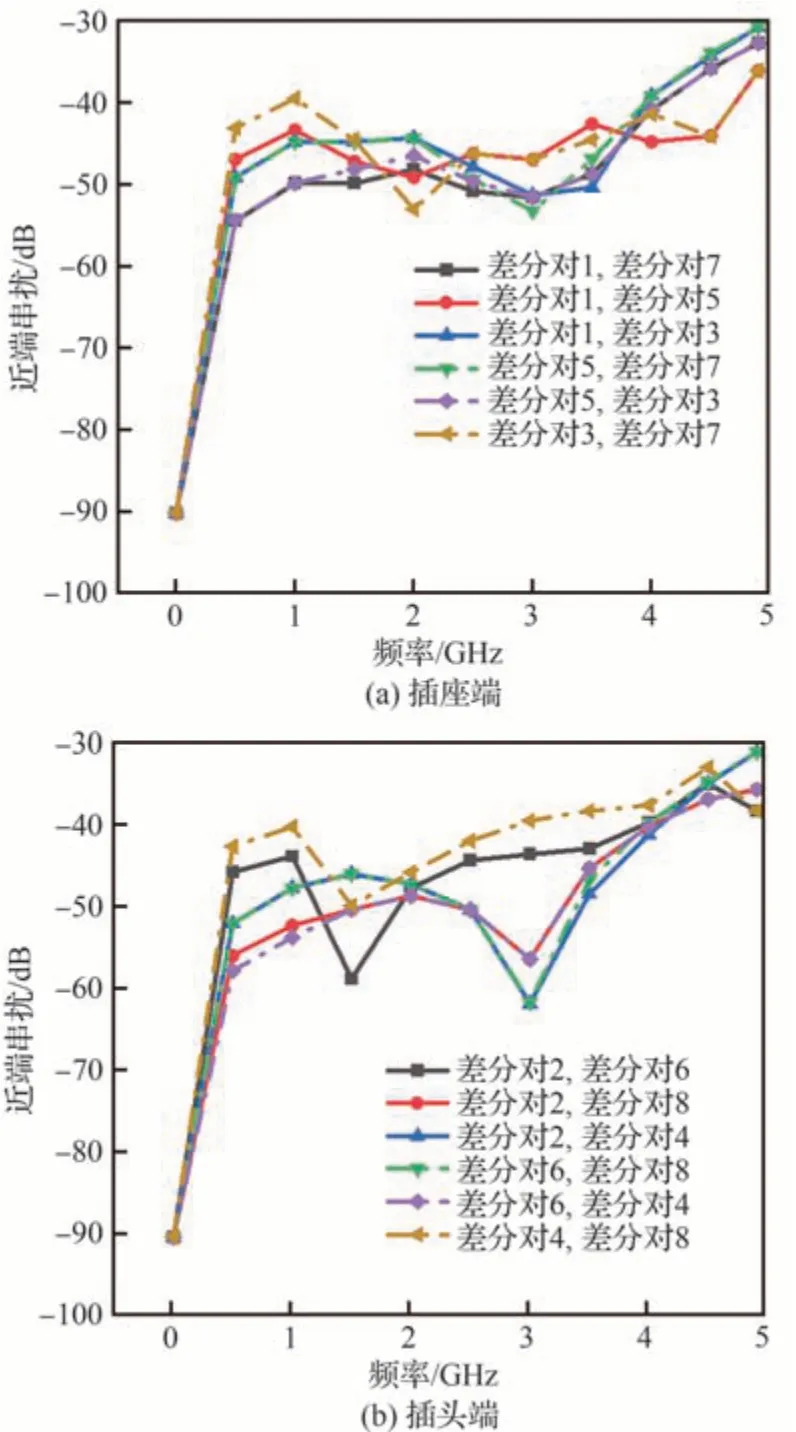

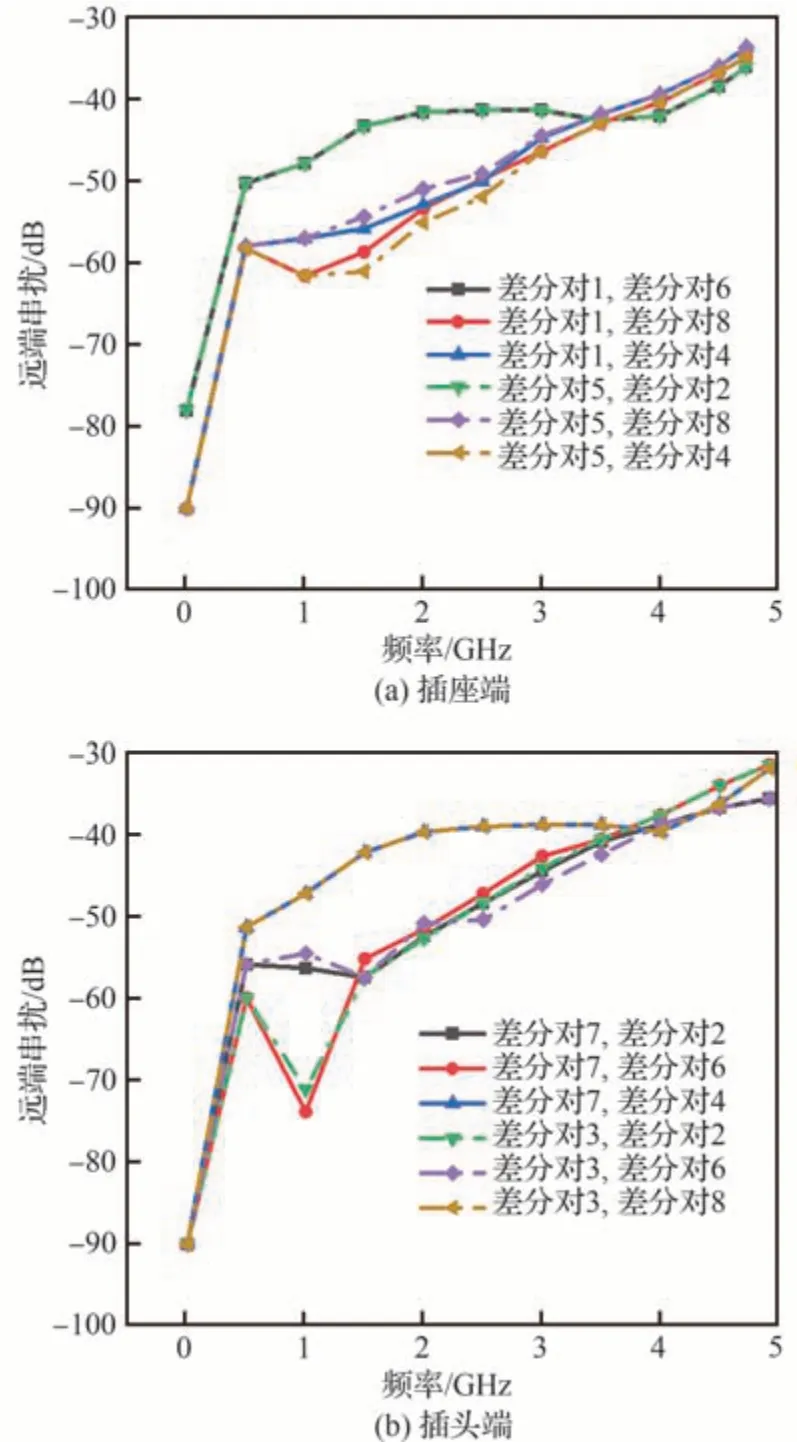

仿真結(jié)果如圖7~圖11 所示,4 個(gè)差分對(duì)的差分阻抗曲線基本重合,其值在91.6~111.9 Ω范圍波動(dòng),略高于規(guī)定范圍(100±10 Ω);插座端的回波損耗基本滿足標(biāo)準(zhǔn)規(guī)定(低于-10 dB),只有在1.8~3 GHz 的頻率區(qū)間最大值達(dá)到-8 dB;插頭端的回波損耗在3.6 GHz 頻率內(nèi)達(dá)標(biāo)(低于-10 dB),在大于3.6 GHz 的頻率區(qū)間,最大值在-6 dB 左右。

圖7 原模型差分阻抗Fig.7 Differential impedance of original model

圖8 原模型插入損耗Fig.8 Insertion loss of the original model

圖9 原模型回波損耗Fig.9 Return loss of original model

圖10 原模型近端串?dāng)_Fig.10 Near-end crosstalk of original model

圖11 原模型遠(yuǎn)端串?dāng)_Fig.11 Far-end crosstalk of the original model

插入損耗在0~3.85 GHz 區(qū)間內(nèi)達(dá)標(biāo),在3.85~5 GHz內(nèi)略高于規(guī)定值(絕對(duì)值小于3 dB)。近端串?dāng)_和遠(yuǎn)端串?dāng)_在5 GHz 頻率內(nèi)都保持在-30 dB 以下,符合標(biāo)準(zhǔn)要求(低于-30 dB)。

由仿真結(jié)果可知,原模型的差分阻抗和回波損耗2 個(gè)參數(shù)的值在某些頻率范圍內(nèi)超出標(biāo)準(zhǔn)范圍,說明該高速連接器在傳遞信號(hào)時(shí)可能發(fā)生信號(hào)反射問題。

4 信號(hào)反射抑制優(yōu)化設(shè)計(jì)

高速連接器在傳輸信號(hào)時(shí),插針線寬、介電常數(shù)、端接線纜線徑等因素都有可能引發(fā)信號(hào)反射。結(jié)合連接器的實(shí)際結(jié)構(gòu),本文對(duì)高速連接器的插針線徑、插針和插孔插合間隙、差分線間距、介質(zhì)厚度等結(jié)構(gòu)參數(shù)和端接電纜線徑、插座端絕緣體材料進(jìn)行優(yōu)化設(shè)計(jì),尋求抑制信號(hào)反射的優(yōu)化方案。

本文研究的高速連接器的4 組差分對(duì)的結(jié)構(gòu)相同且互相對(duì)稱,并且由原模型的仿真結(jié)果可知,4 組差分對(duì)的阻抗曲線、插頭端回波損耗曲線及插座端回波損耗曲線均基本重合。因此,本文只選取其中1 組差分對(duì)與原模型對(duì)比分析,即只分析差分對(duì)1(Diff1)的阻抗和回波損耗S11、S22在優(yōu)化量的參數(shù)變化下的變化規(guī)律。

4.1 接觸件插針線徑優(yōu)化設(shè)計(jì)

由理論分析可知,傳輸線的線徑變化會(huì)影響傳輸線的阻抗連續(xù)性,有可能引發(fā)信號(hào)反射問題。

圖12 為高速連接器插針的結(jié)構(gòu)示意圖,可將其視作圓柱和圓臺(tái)的組合,其中第Ⅱ部分的直徑a=1.27 mm,第Ⅲ部分(較大截面)的直徑b=1.03 mm,第Ⅳ部分的截面直徑c=0.51 mm。

圖12 高速連接器接觸件插針結(jié)構(gòu)圖Fig.12 Diagram of high-speed connector contact pin structure

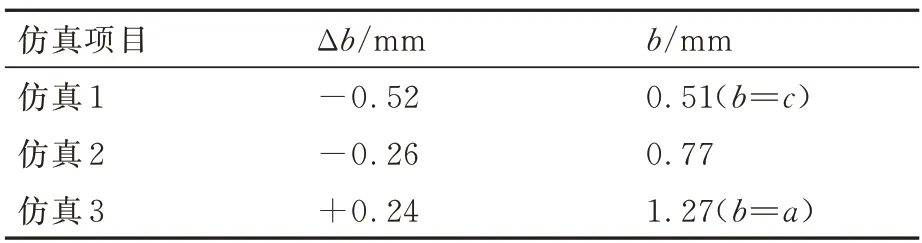

本節(jié)通過改變第Ⅲ部分(錐體下底面直徑)的參數(shù)來研究插針線徑對(duì)信號(hào)反射問題的影響,插針線徑的仿真取值如表1 所示,Δb 為第Ⅲ部分(較大截面)的直徑在原有直徑上的變化值。

表1 插針線徑尺寸的仿真取值Table 1 Simulation of pin diameter size

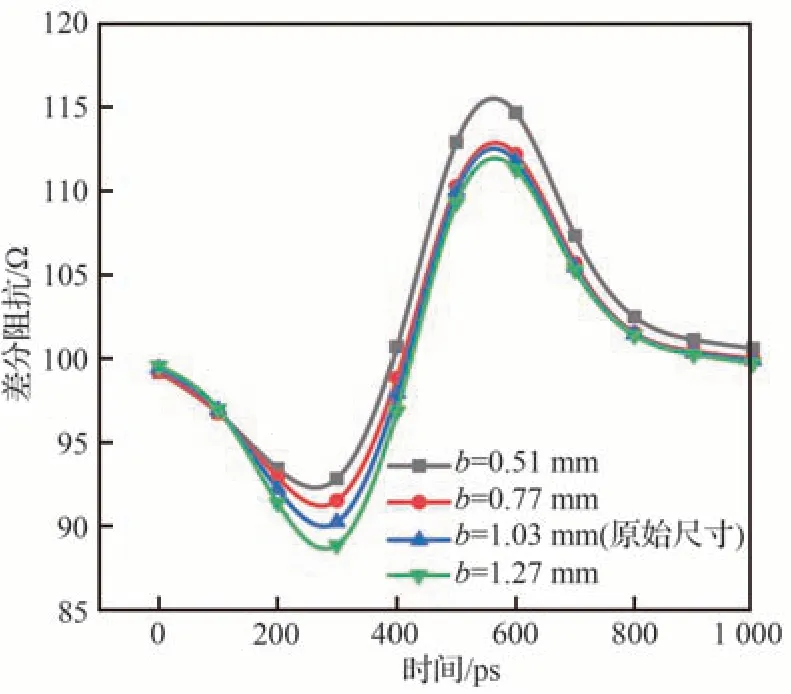

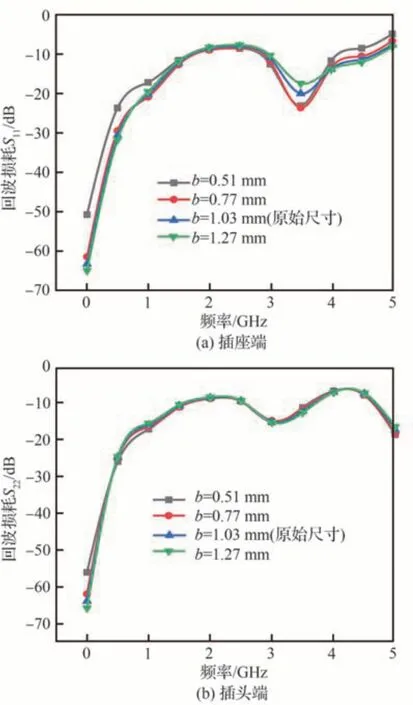

根據(jù)圖13和圖14 的仿真結(jié)果可知,插針錐體的下底面直徑與差分阻抗呈負(fù)相關(guān),與回波損耗也呈負(fù)相關(guān)。當(dāng)b=0.51 mm時(shí),第Ⅱ部分與第Ⅲ部分的線徑差異最大,此時(shí)差分阻抗最大,回波損耗值最大;當(dāng)b=1.27 mm時(shí),第Ⅱ部分與第Ⅲ部分之間為平滑過渡,線徑差異最小,此時(shí)差分阻抗最小,回波損耗值最小。

圖13 不同插針線徑的差分阻抗Fig.13 Differential impedance of different pin diameters

圖14 不同插針線徑的回波損耗Fig.14 Return loss of different pin diameters

因此,插針線徑變化處的線徑差異是影響高速連接器差分阻抗和回波損耗的關(guān)鍵因素,也是引發(fā)信號(hào)反射問題的重要原因。減小插針線徑變化處的線徑差異,能較好地改善高速連接器的信號(hào)反射問題。

4.2 接觸件插針和插孔插合間隙優(yōu)化設(shè)計(jì)

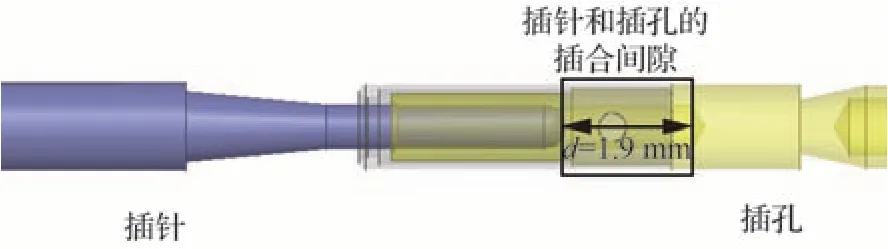

如圖15 所示,高速連接器接觸件的插針頂部和插孔底部在插針和插孔完全插合后有一定長度的插合間隙,間隙的長度為1.9 mm。

圖15 高速連接器插針和插孔的插合間隙Fig.15 High-speed connector pin and jack mating gap

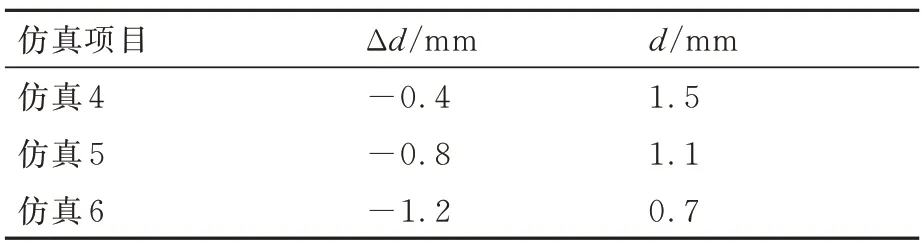

本節(jié)研究接觸件插針和插孔插合間隙對(duì)高速連接器信號(hào)反射問題的影響,通過增加插針長度來實(shí)現(xiàn)插合間隙長度的改變,插合間隙長度的仿真取值如表2 所示,Δd 為插針和插孔的插合間隙在原有間隙上的變化值。

表2 插針和插孔間插合間隙長度的仿真取值Table 2 Simulation values of length of gap between pins and jacks

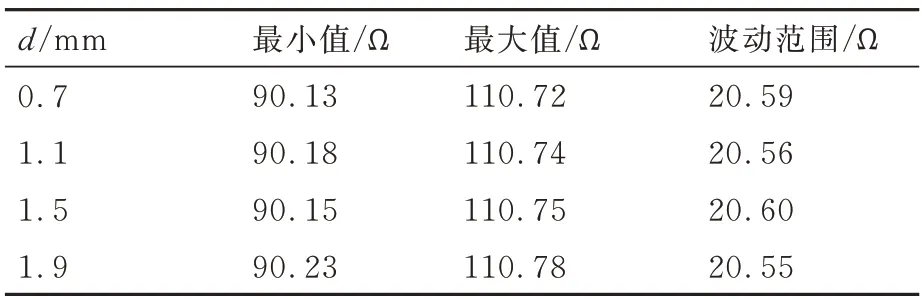

由表3~表5 的仿真結(jié)果可知,插針和插孔間的插合間隙不同時(shí),高速連接器的差分阻抗和回波損耗與原模型相差很小,分別在 0.24%和0.85%以內(nèi),即接觸件插針和插孔間隙對(duì)高速連接器信號(hào)反射問題的影響可以忽略不計(jì)。

表3 不同插合間隙長度的差分阻抗Table 3 Differential impedance of different insertion gap lengths

表4 不同插合間隙長度的插座端回波損耗最大值Table 4 Maximum return loss at socket end of different insertion gap lengths

表5 不同插合間隙長度的插頭端回波損耗最大值Table 5 Maximum return loss at plug end of different insertion gap lengths

4.3 差分線間距優(yōu)化設(shè)計(jì)

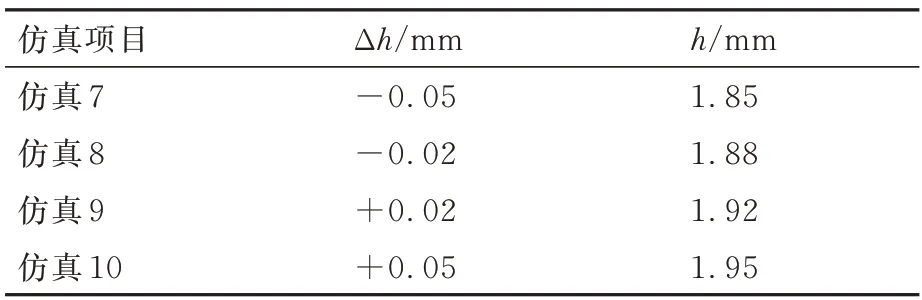

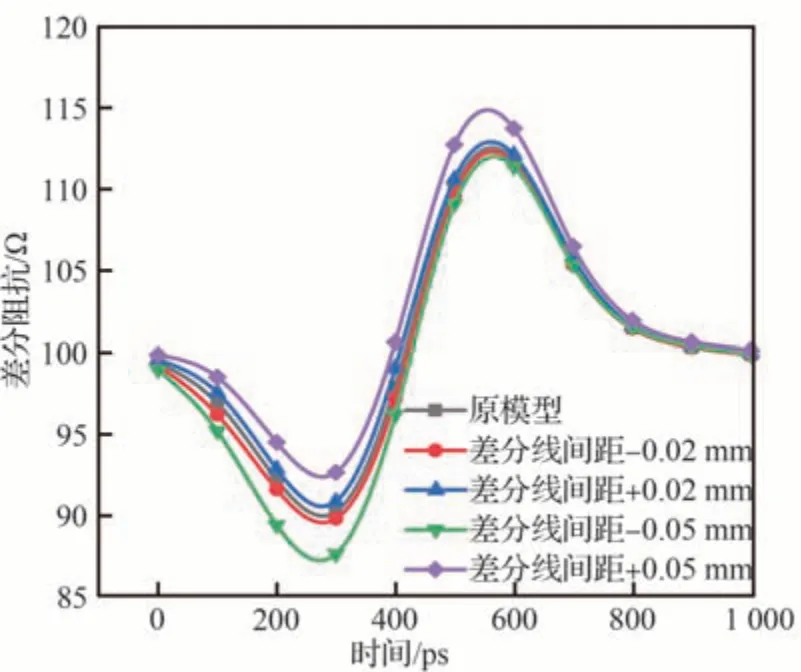

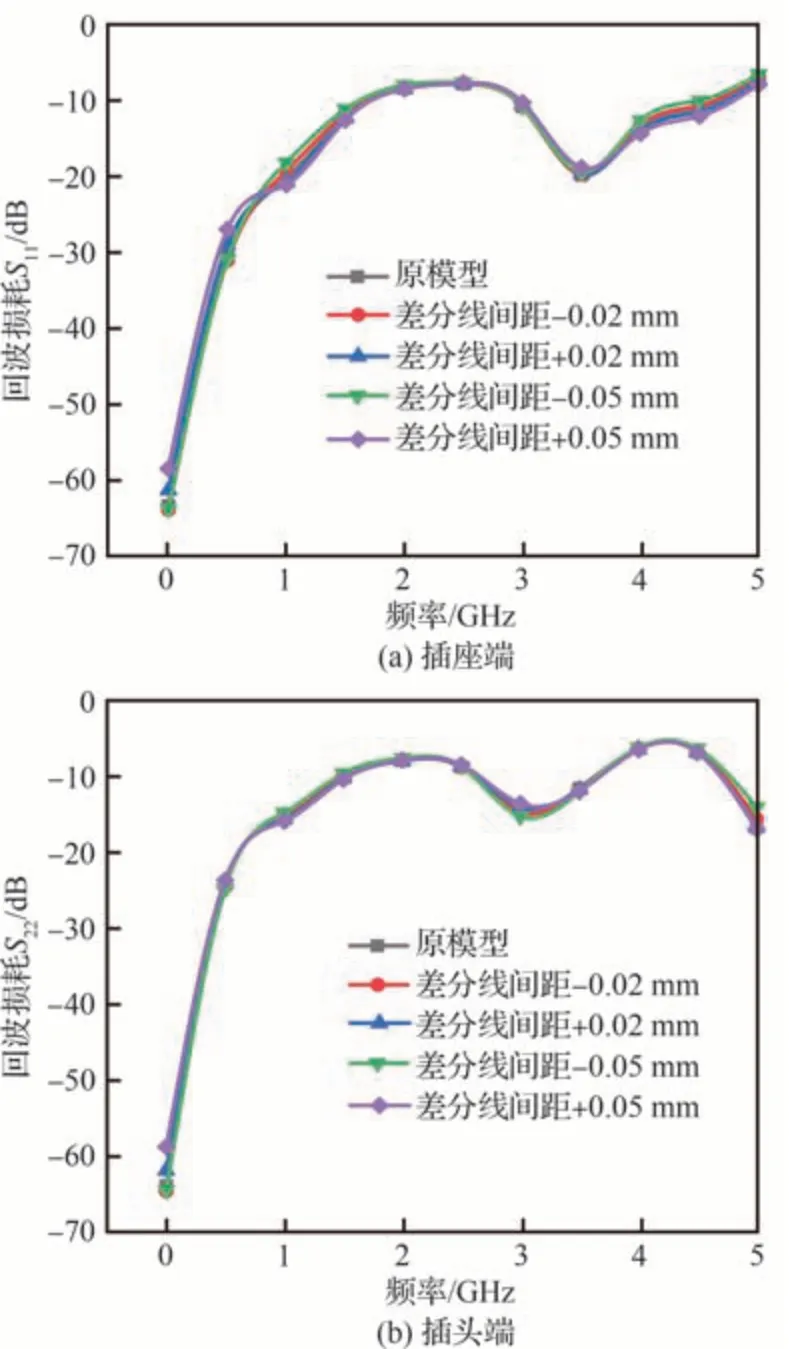

本節(jié)研究差分線間距對(duì)信號(hào)反射問題的影響,差分線間距的原始值為1.9 mm,仿真取值如表6 所示,Δh 為差分線間距在原有間距上的變化值。

表6 差分線間距的仿真取值Table 6 Simulation values of differential line spacing

根據(jù)圖16和圖17 的仿真結(jié)果可知,高速連接器改變差分線間距后的回波損耗數(shù)值與原模型相差0.79%以內(nèi);但在差分線間距增大時(shí),差分阻抗有輕微增大,這是由于差分對(duì)間耦合減弱導(dǎo)致串?dāng)_增大引起的,與信號(hào)反射基本無關(guān),因此可以忽略差分對(duì)間距對(duì)信號(hào)反射問題的影響。

圖16 不同差分線間距的差分阻抗Fig.16 Differential impedance of different differential line spacing

圖17 不同差分線間距的回波損耗Fig.17 Return loss of different differential line spacing

4.4 介質(zhì)厚度優(yōu)化設(shè)計(jì)

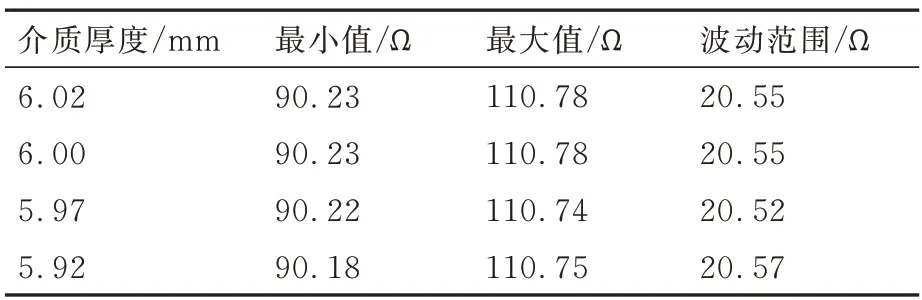

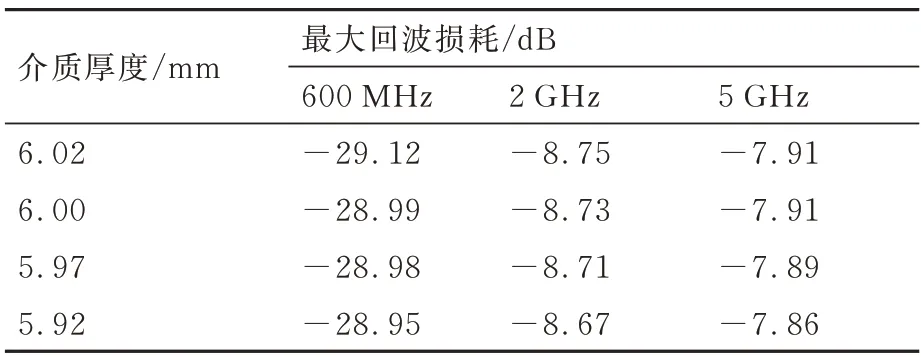

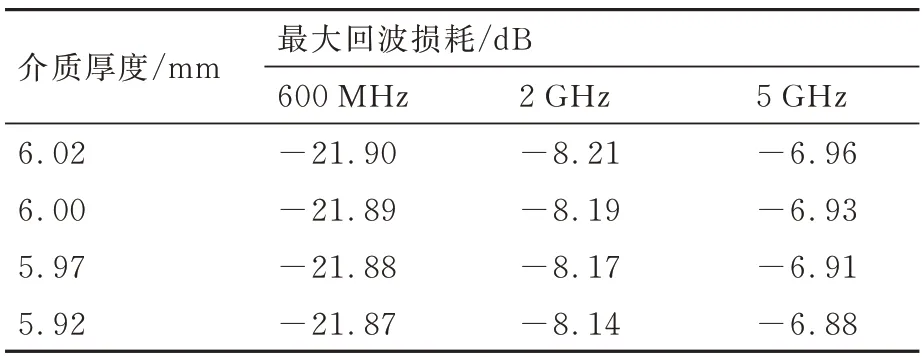

本節(jié)研究介質(zhì)厚度對(duì)信號(hào)反射問題的影響,介質(zhì)厚度的初始值為6.02 mm。對(duì)介質(zhì)厚度進(jìn)行仿真取值時(shí),需確保絕緣介質(zhì)的形狀不變,介質(zhì)厚度取值為6.00 mm、5.97 mm、5.92 mm。

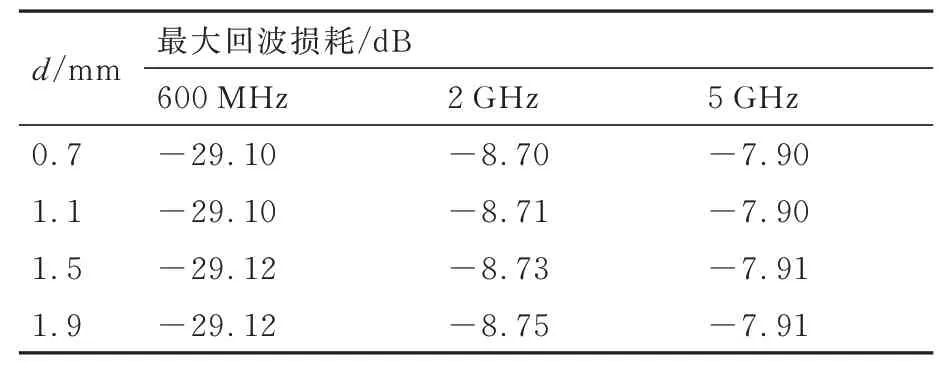

由表7~表9 的仿真結(jié)果可知,當(dāng)介質(zhì)厚度減小0.1 mm時(shí),差分阻抗和回波損耗分別與原模型相差0.09%以內(nèi)和1.1%以內(nèi)。因此,介質(zhì)厚度減小0.1 mm 對(duì)高速連接器信號(hào)反射問題的影響較小,可以忽略。

表7 不同介質(zhì)厚度的差分阻抗Table 7 Differential impedance of different dielectric thicknesses

表8 不同介質(zhì)厚度的插座端回波損耗最大值Table 8 Maximum return loss at socket end of different dielectric thicknesses

表9 不同介質(zhì)厚度的插頭端回波損耗最大值Table 9 Maximum return loss at plug end of different dielectric thicknesses

4.5 端接線纜線徑優(yōu)化設(shè)計(jì)

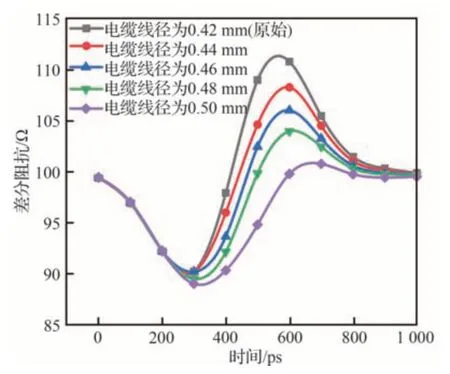

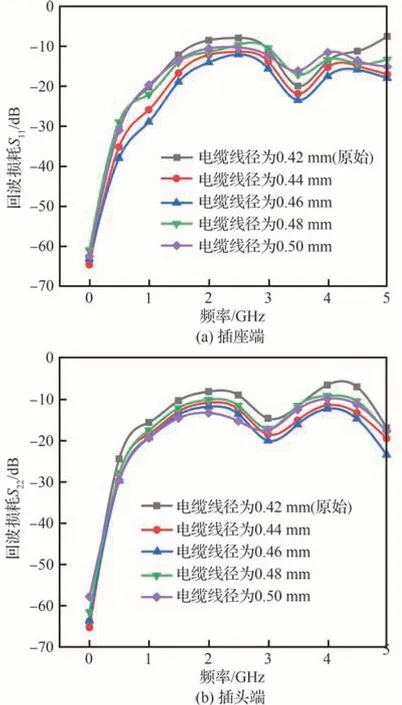

本節(jié)研究端接線纜線徑對(duì)信號(hào)反射問題的影響,端接線纜線徑的初始值為0.42 mm。為了改善原模型插頭端差分阻抗偏高的情況,采用增大端接線纜線徑的方法進(jìn)行優(yōu)化。

本文選用的高速連接器的端接線纜線徑為0.411~0.509 mm,本節(jié)分別對(duì)線徑為0.42 mm、0.44 mm、0.46 mm、0.48 mm、0.50 mm 的端接線纜進(jìn)行仿真分析。

圖18 為不同端接線纜線徑的差分阻抗變化曲線,可以看出,增大端接線纜線徑對(duì)差分阻抗的改善較明顯,對(duì)于線徑0.44 mm 以上的端接線纜,差分阻抗最大值均小于110 Ω,當(dāng)端接線纜線徑為0.5 mm時(shí),差分阻抗最大值僅為101.8 Ω。因此增大端接線纜線徑可顯著改善原模型插頭端差分阻抗偏高的情況。

圖18 不同電纜線徑的差分阻抗Fig.18 Differential impedance of different cable diameters

圖19 為不同端接線纜線徑的回波損耗變化曲線,可以看出,優(yōu)化后的端接線纜的回波損耗數(shù)值相比原模型改善8.6%以上,信號(hào)反射抑制較為明顯。

圖19 不同電纜線徑的回波損耗Fig.19 Return loss of different cable diameters

綜合考慮到經(jīng)濟(jì)性和可行性等要求,選用線徑為0.44 mm和0.46 mm 的端接線纜繼續(xù)進(jìn)行研究。

4.6 插座端絕緣體材料優(yōu)化設(shè)計(jì)

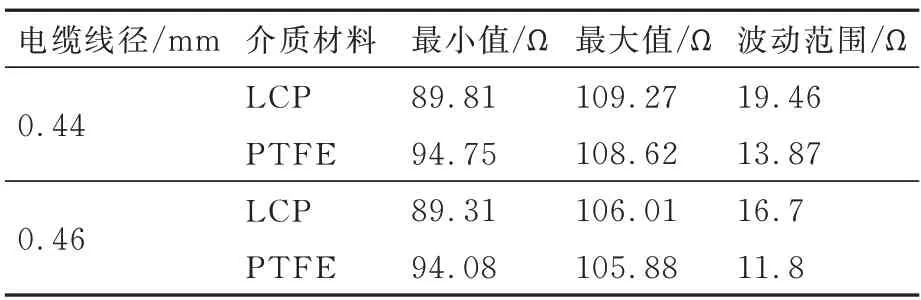

由原模型的仿真結(jié)果可知,本文選用的高速連接器的插座端差分阻抗偏低,本節(jié)采用將高速連接器插座端的絕緣介質(zhì)更換為介電常數(shù)更小的材料的方法進(jìn)行優(yōu)化。

原模型的插座端絕緣體材料為液晶聚合物(Liquid Crystal Polymer,LCP),其相對(duì)介電常數(shù)為3.8,耗散因子tanδ=0.002 6;優(yōu)化的插座端絕緣體材料為聚四氟乙烯(Polytetrafluoroethylene,PTFE),其相對(duì)介電常數(shù)為2.1,耗散因子tanδ=0.001。

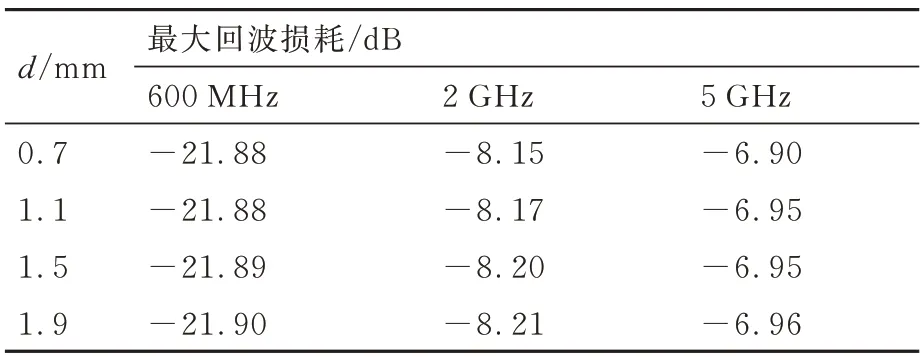

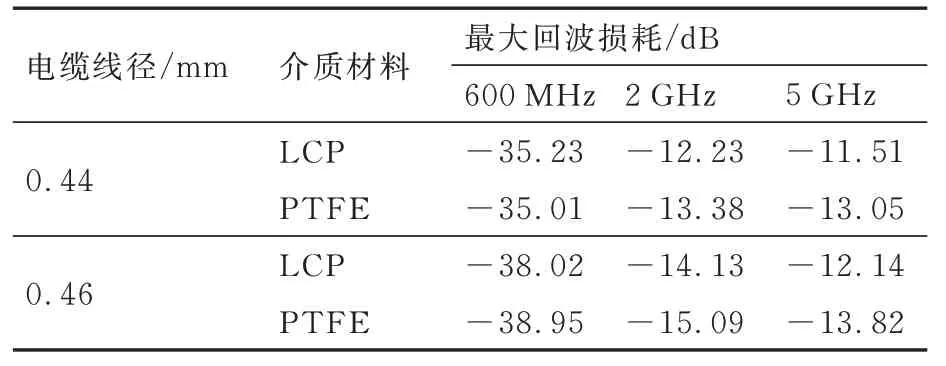

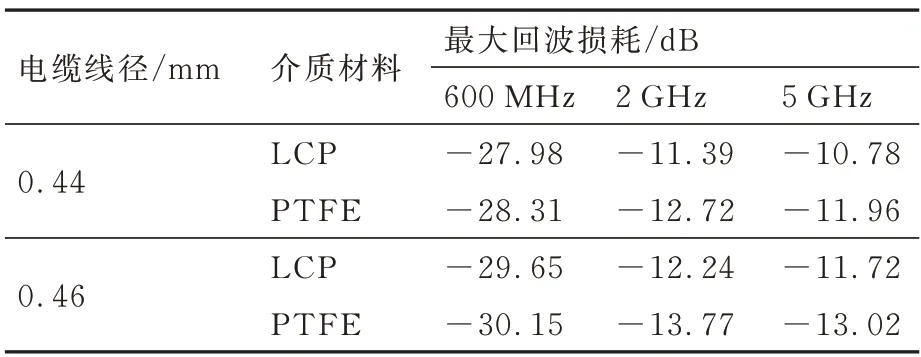

由表10~表12 的仿真結(jié)果可知,當(dāng)插座端絕緣體材料由LCP 更換為PTFE后,差分阻抗最小值增大5.34%以上,且波動(dòng)范圍減小28.7%以上;回波損耗最大值在不同頻率范圍內(nèi)均有所減小,在5 GHz 內(nèi)減小10.9%~13.8%。因此選用介電常數(shù)更小的插座端絕緣材料可以較好地改善信號(hào)反射問題。

表10 不同插座絕緣介質(zhì)材料的差分阻抗Table 10 Differential impedance of different socket insulation dielectric materials

表11 不同插座絕緣介質(zhì)材料的插座端回波損耗最大值Table 11 Maximum return loss at socket end of different socket insulation dielectric materials

表12 不同插座絕緣介質(zhì)材料的插頭端回波損耗最大值Table 12 Maximum return loss at plug end of different socket insulation dielectric materials

5 仿真結(jié)果驗(yàn)證

由于仿真軟件設(shè)置的是理想環(huán)境,而現(xiàn)實(shí)環(huán)境的外界因素干擾較多,因此本文通過測(cè)試實(shí)驗(yàn)來驗(yàn)證仿真結(jié)果的有效性。

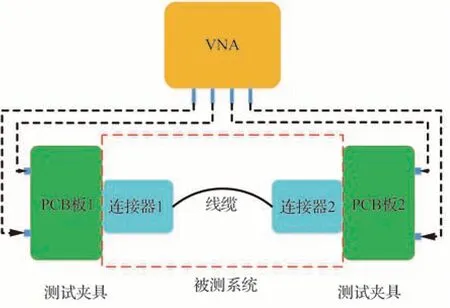

本文選取的高速連接器適用于“板對(duì)線”的連接結(jié)構(gòu),即高速連接器在實(shí)際工作時(shí),插座端連接“板”,插頭端連接線纜。測(cè)試實(shí)驗(yàn)使用是德科技有限公司生產(chǎn)的E5071C 型號(hào)的矢量網(wǎng)絡(luò)分析儀,在設(shè)計(jì)測(cè)試電路時(shí),需滿足的基本條件:①測(cè)試電路中連接器的接線方式與其實(shí)際使用時(shí)的接線方式一致;② 矢量網(wǎng)絡(luò)分析儀在使用時(shí),需經(jīng)過特制的PCB 測(cè)試夾具和被測(cè)系統(tǒng)相連。

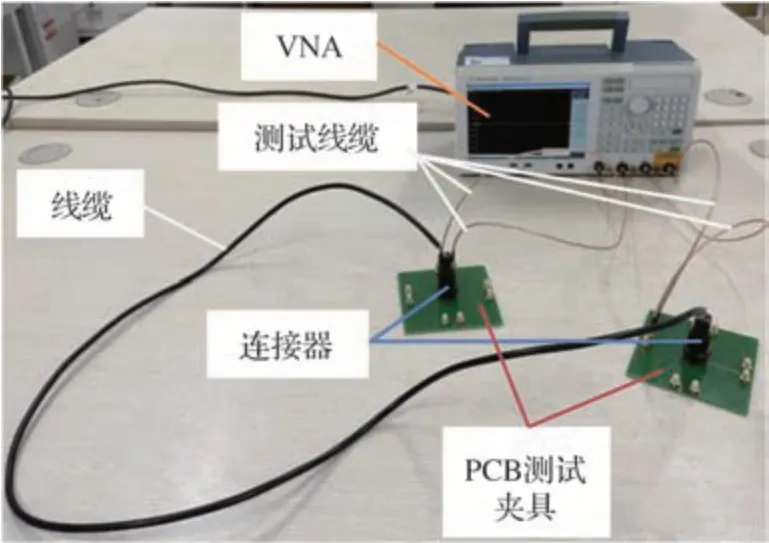

在上述條件的約束下,設(shè)計(jì)了2 個(gè)連接器的測(cè)試電路,如圖20 所示,即2 個(gè)連接器的插座端分別固定在2 個(gè)PCB 測(cè)試夾具上,插頭端之間用超六類線纜相連;被測(cè)系統(tǒng)由2 個(gè)連接器及插頭端之間的線纜組成,并經(jīng)過PCB 測(cè)試夾具與矢量網(wǎng)絡(luò)分析儀相連,圖21 為測(cè)試電路的實(shí)物圖。

圖20 測(cè)試電路原理圖Fig.20 Schematic diagram of the test circuit

圖21 測(cè)試電路實(shí)物圖Fig.21 Physical diagram of the test circuit

本節(jié)在進(jìn)行仿真結(jié)果和實(shí)測(cè)結(jié)果的對(duì)比分析時(shí),選取其中1 對(duì)差分對(duì)。

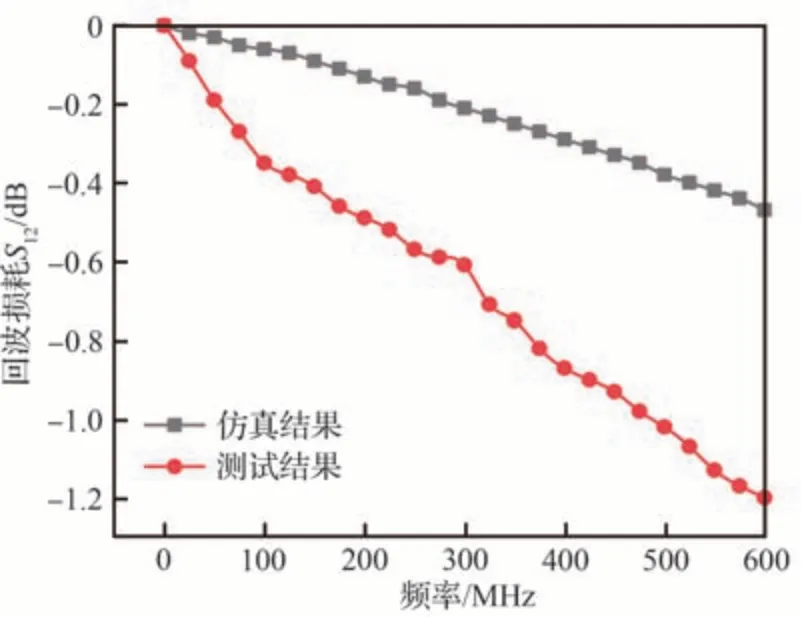

圖22 為插入損耗的測(cè)試結(jié)果與仿真結(jié)果的對(duì)比圖,測(cè)試結(jié)果等于2 個(gè)高速連接器的插入損耗與線纜的插入損耗之和,仿真結(jié)果為單個(gè)高速連接器的插入損耗。在600 MHz時(shí),插入損耗測(cè)試結(jié)果的最大值為-1.219 dB,仿真結(jié)果的最大值為-0.463 dB,基本符合預(yù)期。

圖22 插入損耗測(cè)試結(jié)果與仿真結(jié)果對(duì)比Fig.22 Comparison of insertion loss test results and simulation results

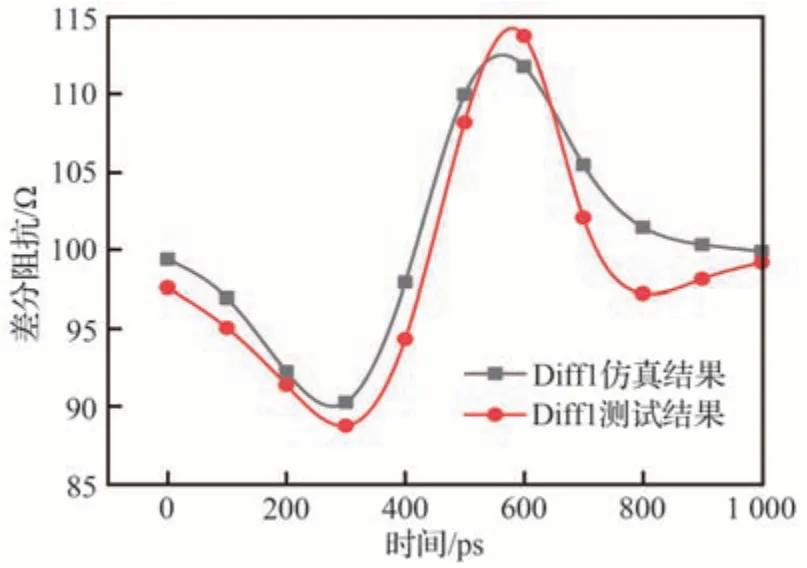

圖23 為差分阻抗的仿真結(jié)果和測(cè)試結(jié)果的對(duì)比,可以看出,測(cè)試結(jié)果在87.9~113.1 Ω 范圍內(nèi),仿真結(jié)果在91.6~111.9 Ω 范圍內(nèi)。差分阻抗的測(cè)試結(jié)果和仿真結(jié)果的極值相差1.1%以內(nèi),但測(cè)試結(jié)果的波動(dòng)范圍略大。

圖23 阻抗測(cè)試結(jié)果和仿真結(jié)果對(duì)比Fig.23 Comparison of impedance test results and simulation results

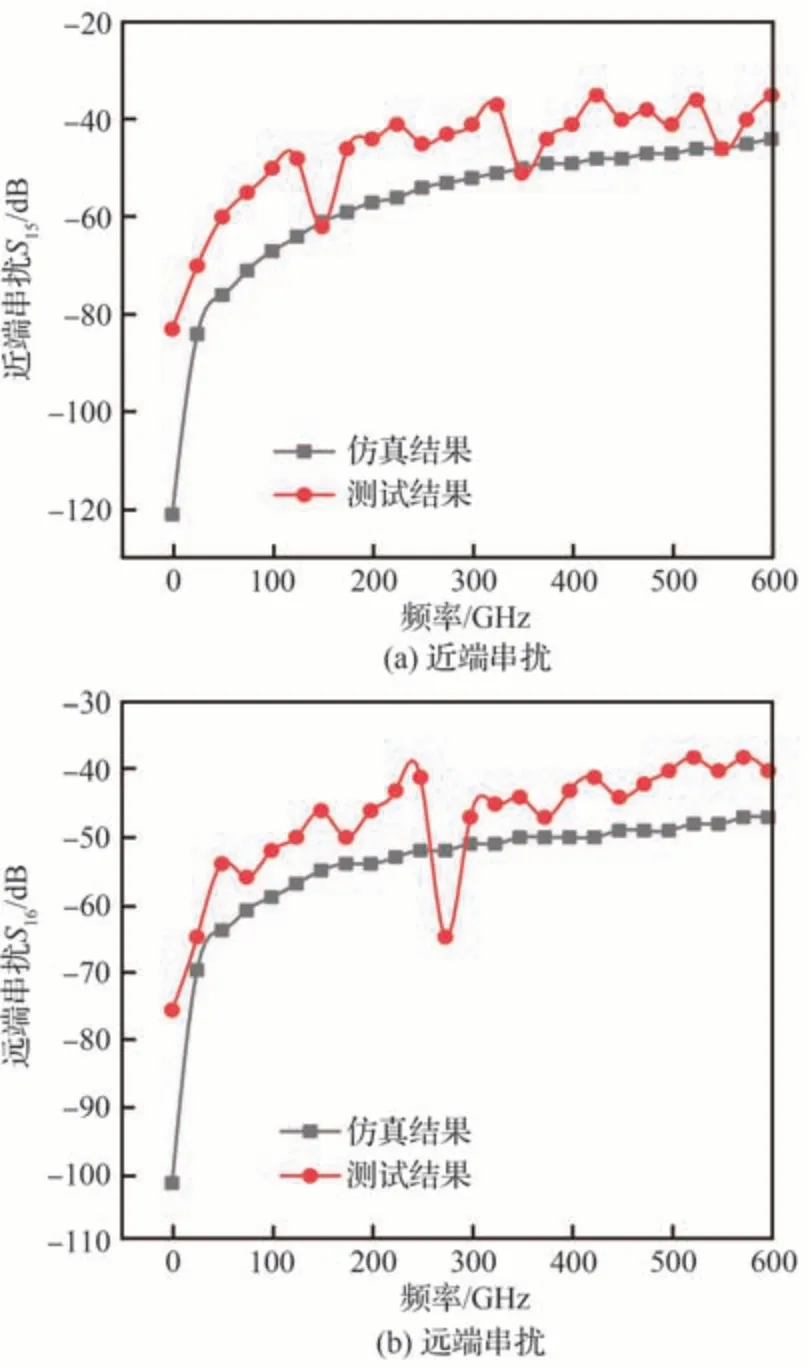

圖24 為近遠(yuǎn)端串?dāng)_的仿真結(jié)果和測(cè)試結(jié)果對(duì)比,測(cè)試結(jié)果的曲線有上下波動(dòng)的情況,整體趨勢(shì)隨頻率的增大緩慢向上,與仿真結(jié)果一致。測(cè)試結(jié)果雖略大于仿真結(jié)果,但整體數(shù)值仍小于-30 dB,符合要求。

圖24 串?dāng)_的測(cè)試結(jié)果與仿真結(jié)果對(duì)比Fig.24 Comparison of test results and simulation results of crosstalk

仿真結(jié)果與測(cè)試結(jié)果存在誤差的原因考慮為:①測(cè)試實(shí)驗(yàn)使用2 個(gè)連接器組合測(cè)試的方法,被測(cè)件增多導(dǎo)致誤差變大;② 仿真環(huán)境中設(shè)置的材料屬性、邊界條件等參數(shù)與實(shí)際環(huán)境有差異;③PCB 測(cè)試夾具在設(shè)計(jì)制作時(shí)的焊接可能會(huì)導(dǎo)致插針輕微損傷,連接點(diǎn)不穩(wěn)定;④ 測(cè)試環(huán)境中有干擾等。總體來說,誤差在較小范圍內(nèi),可以證實(shí)仿真結(jié)果的有效性。

6 信號(hào)反射抑制優(yōu)化方案

根據(jù)以上仿真結(jié)果,當(dāng)端接電纜線徑為0.44~0.46 mm,插座端絕緣體材料更換為PTFE后,高速連接器差分阻抗的最大值減小至110 Ω 以下,最小值增大2.72%以上,波動(dòng)范圍減小31.7%~41.8%;回波損耗在不同頻率范圍內(nèi)的最大值均有所減小,整體數(shù)值改善約9.8%~12.3%,信號(hào)反射問題得到顯著改善。

表13 為端接電纜線徑為0.44 mm和0.46 mm、插座端絕緣體材料為PTFE時(shí),5 GHz內(nèi)插入損耗的最小值和串?dāng)_的最大值,可以看出,優(yōu)化后的高速連接器插入損耗的最小值分別為-3.31 dB和-3.12 dB,相比原模型有改善;近遠(yuǎn)端串?dāng)_的最大值均小于-30 dB,在標(biāo)準(zhǔn)范圍內(nèi)。

確定高速連接器信號(hào)反射抑制的優(yōu)化方案:在滿足連接器電氣性能、經(jīng)濟(jì)性等要求下,減小插針線徑變化處的線徑差異,增大端接線纜線徑及選用介電常數(shù)較小的插座端絕緣體材料。

7 結(jié)論

1)提出了一種在工程中改善高速連接器信號(hào)反射問題的優(yōu)化設(shè)計(jì)方法:在滿足連接器電氣性能、經(jīng)濟(jì)性等要求下,減小插針線徑變化處的線徑差異,增大端接線纜線徑及選用介電常數(shù)較小的插座端絕緣體材料。

2)在工程中改善高速連接器信號(hào)反射問題的優(yōu)化設(shè)計(jì)結(jié)果表明:插針線寬變化處的差異值越大,回波損耗值越大,信號(hào)反射問題越嚴(yán)重;增大端接電纜線徑后,阻抗不連續(xù)的情況得到改善,差分阻抗最大值減小,回波損耗值減小;換用介電常數(shù)更小的插座端絕緣材料,差分阻抗波動(dòng)范圍減小,回波損耗數(shù)值減小。

3)所提出的優(yōu)化設(shè)計(jì)優(yōu)化效果明顯,差分阻抗的最大值減小至110 Ω 以下,最小值增大2.72%以上,波動(dòng)范圍減小31.7%~41.8%;回波損耗在不同頻率范圍內(nèi)的最大值均有所減小,整體數(shù)值改善約9.8%~12.3%,信號(hào)反射問題得到顯著改善。

4)通過測(cè)試實(shí)驗(yàn)證實(shí)了仿真結(jié)果的有效性,同時(shí)也說明了優(yōu)化設(shè)計(jì)方法的可行性。

5)本文提出選用介電常數(shù)更小的插座端絕緣材料可以改善信號(hào)反射問題,但是如何確定插座端絕緣材料的介電常數(shù)范圍仍然需要研究。