高增益高驅動能力的基準電壓緩沖芯片的設計

摘" 要: 為了解決當前CMOS基準電壓緩沖器在驅動大電容負載電路時所面臨的可靠性問題和性能瓶頸,提出一種高增益高驅動能力的基準電壓緩沖芯片。該芯片采用CMOS緩沖放大器,結構包括折疊式共源共柵輸入級、軌至軌Class AB輸出級和推挽輸出緩沖級。設計中加入了修調電路、Clamp電路及ESD防護電路。芯片面積為2 390 μm×1 660 μm。在SMIC 0.18 μm CMOS工藝下進行了前仿真、版圖繪制及Calibre后仿真。前仿結果顯示:當負載電容為10 μF時,電路實現了126 dB的高開環增益和97°的相位裕度,同時PSRR超過131 dB,噪聲為448 nV/[Hz@100 Hz]及1 nV/[Hz@100 Hz]。后仿結果與前仿結果基本一致。總體結果表明,該電路具有高增益、高電源抑制比及低噪聲等特點,同時擁有很高的輸出驅動能力。因此,所提出的基準電壓緩沖芯片可以用于驅動如像素陣列等具有大電容負載的電路。

關鍵詞: 基準電壓緩沖芯片; CMOS電壓緩沖運算放大器; ESD防護電路; 芯片版圖; 高增益; 高驅動能力

中圖分類號: TN402?34; TN722?34" " " " " " " " " "文獻標識碼: A" " " " " " " " " 文章編號: 1004?373X(2024)16?0033?06

Design of reference voltage buffer chip with high?gain and high?driving capability

WANG Mincong, LIU Cheng

(School of Microelectronics, Shanghai University, Shanghai 201800, China)

Abstract: In allusion to the reliability issues and performance bottlenecks encountered by the current CMOS reference voltage buffer when driving large?capacitance load circuits, a reference voltage buffer chip with high gain and high driving capacity is proposed. The chip employs a CMOS buffer amplifier, featuring a folded cascode structure at the input stage, a rail?to?rail Class?AB structure at the output stage, and a push?pull output buffer stage. In the design, the trimming circuits, Clamp circuits, and ESD protection circuits are incorporated. The chip area is 2 390 μm×1 660 μm. The pre?simulation, layout design, and post?simulation with Calibre are conducted under the SMIC 0.18 μm CMOS process. The pre?simulation results demonstrate that with a load capacitance of 10 μF, the circuit can realize a high open?loop gain of 126 dB, a phase margin of 97°, and a PSRR exceeding 131 dB. The noise levels are 448 nV/[Hz]@100 Hz and 1 nV/[Hz]@100 kHz. The post?simulation results are consistent with the pre?simulation results. The overall results demonstrate that that the circuit has characteristics such as high gain, high power suppression ratio, and low noise, as well as high output driving capability. Therefore, the proposed reference voltage buffer chip can be utilized to drive circuits such as pixel arrays with large capacitive loads.

Keywords: reference voltage buffer chip; CMOS voltage buffer operational amplifier; ESD protection circuit; chip layout; high gain; high driving ability

0" 引" 言

在當前的圖像傳感器和顯示器等電子設備中,電壓參考緩沖器扮演著至關重要的角色[1?6]。它不僅為像素陣列提供穩定的工作電壓,還直接影響到設備的性能表現。隨著電子設備的發展,對于基準電壓穩定性和精確性的要求不斷提高,高性能的基準電壓緩沖器的需求變得日益迫切。在電子產品市場上,性能優異的基準電壓緩沖器無疑是提高產品競爭力和市場占有率的關鍵因素之一。因此,為滿足市場需求和應對競爭壓力,高性能的基準電壓緩沖器的研究與設計具有重要意義。

近年來,電壓參考緩沖器的研究主要集中在降低功耗、提高性能等方面。文獻[1]中提出了一種基于差分翻轉電壓跟隨器的AB類緩沖放大器,解決了功耗較大的問題,但是增益不高。文獻[2]中提出了一種與基準電壓電路配合的超低電流CMOS模擬電壓緩沖器,確保閉環增益的精度優于0.01%,但其帶負載能力比較弱。文獻[3]中提出了一種互補輸入和改進輸出的超低功耗的高速CMOS電壓緩沖器,但其噪聲很高。

由于像素陣列通常具有大量的像素,因此緩沖器需要具備足夠的輸出電流能力和帶大負載能力。此外,在像素陣列的高靈敏度應用中,噪聲問題更加突出。因此,緩沖器還應具備低噪聲特性,以保證圖像的清晰度和準確性。另外,良好的電源抗干擾能力能確保芯片長時間穩定的運行。基于此,本文設計一款擁有低噪聲、高增益、高驅動能力等優異性能的基準電壓緩沖芯片。該設計所突出的特點是在復雜的載荷條件下依舊能夠達到優異的性能指標,以及解決了芯片在實際使用過程中可能遇到的ESD事件和過壓問題。

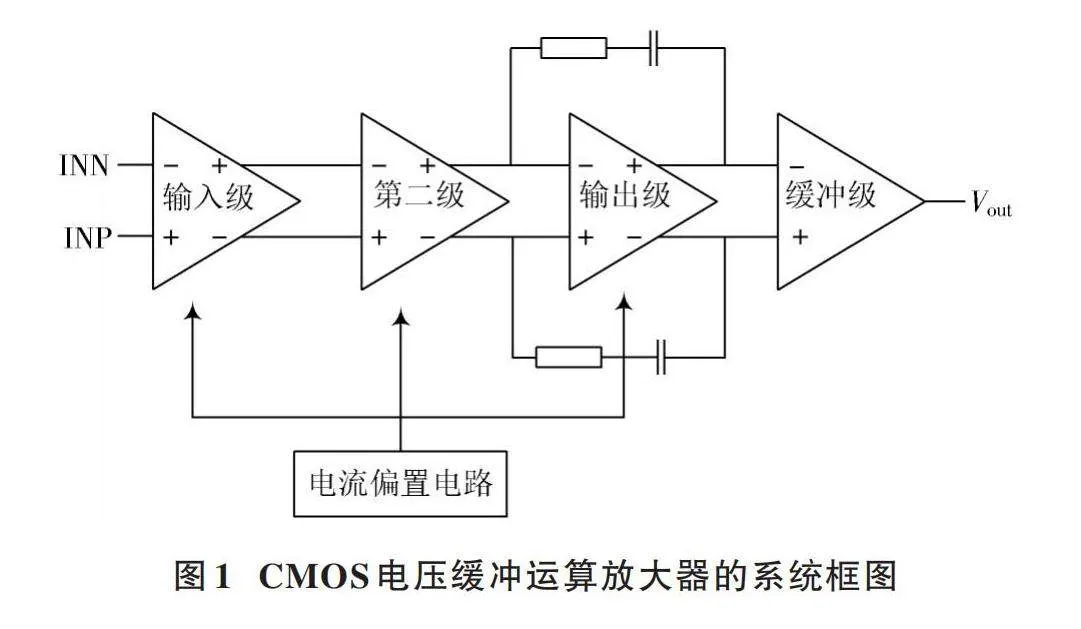

1" 系統級設計

CMOS緩沖放大器由輸入級、第二級、輸出級、緩沖級和偏置電路5個電路模塊組成,整體設計架構如圖1所示。該電路的穩定性主要通過跨接在共源共柵晶體管輸出端與運放輸出級之間的2個米勒電容來保證,從而切斷前饋路徑并消除右半平面的零點。將其接成電壓跟隨電路即可作為基準電壓緩沖芯片,為后級電路提供基準電壓。此外,還可以根據具體電路要求,接成同向放大、反向放大和加減電路等運算放大結構,以滿足調整參考電壓的需求。

2" 電路設計分析和前仿真

2.1" 電路設計

2.1.1" 電流偏置電路設計

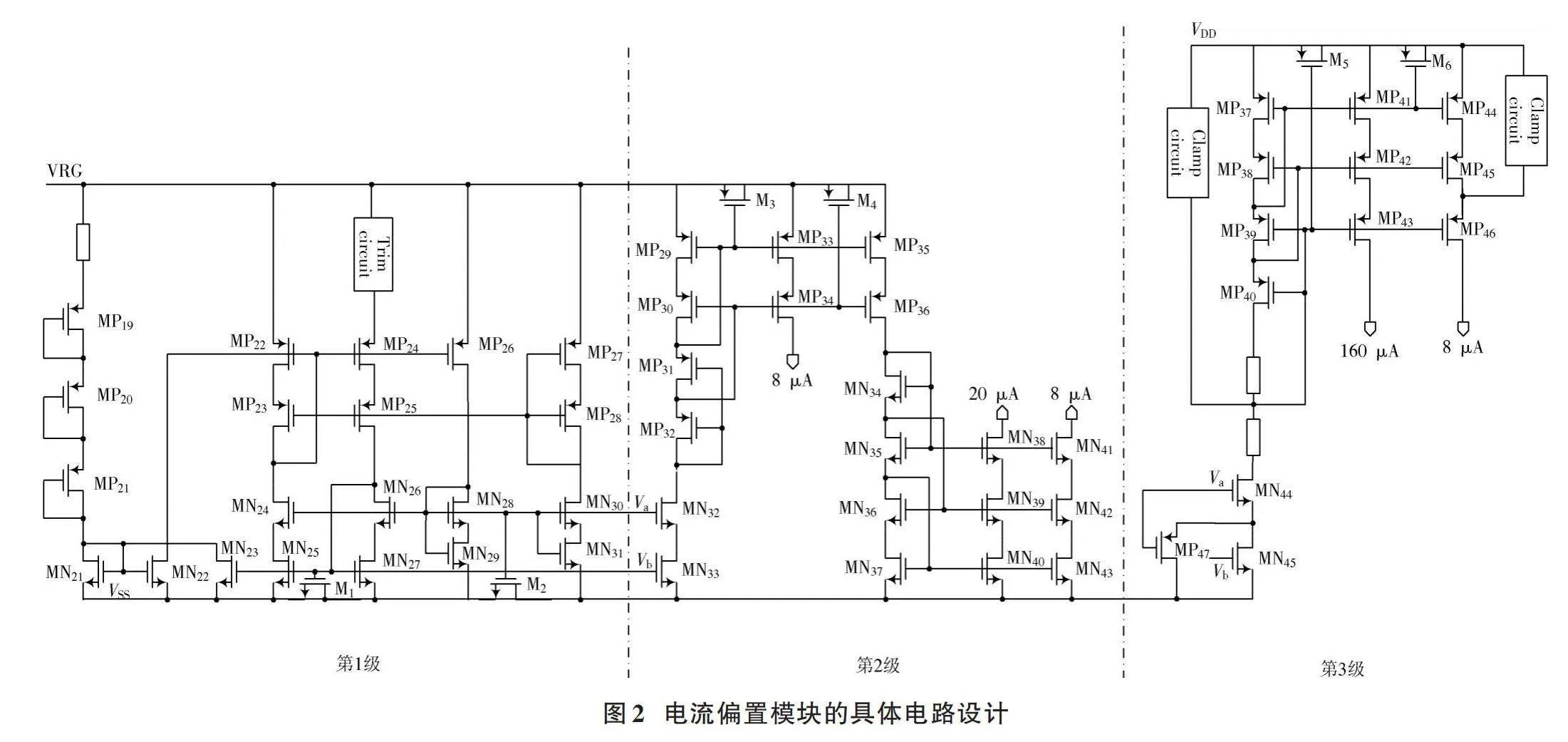

電流偏置電路用于給運放主體電路模塊提供偏置電流,主要思路是利用低壓共源共柵電流鏡作電流復制。

電流偏置模塊的電路設計如圖2所示。

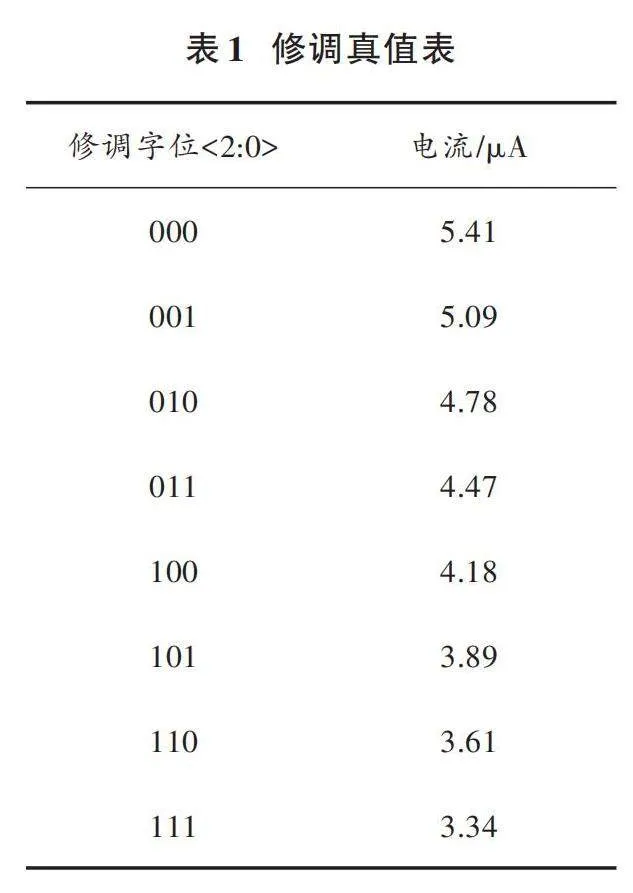

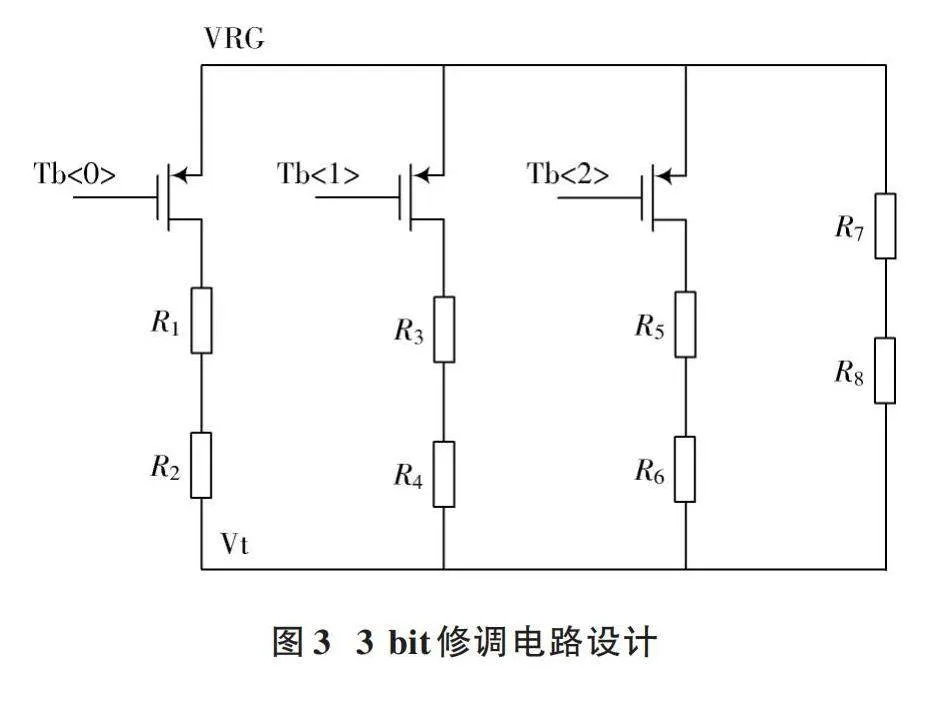

電流偏置電路分為三級,第一級產生電壓偏置,第二級產生小電流偏置,第三級產生大電流偏置。特別要說明的是,在第一級中設置了一個3 bit修調電路,具體電路設計如圖3所示。每一條支路由一個MOS管串聯兩個電阻來形成偏置電流,通過控制MOS管的柵極電位可以改變修調電路產生的偏置電流大小,并在測試時用于參數校準和信號校正。修調真值表如表1所示。

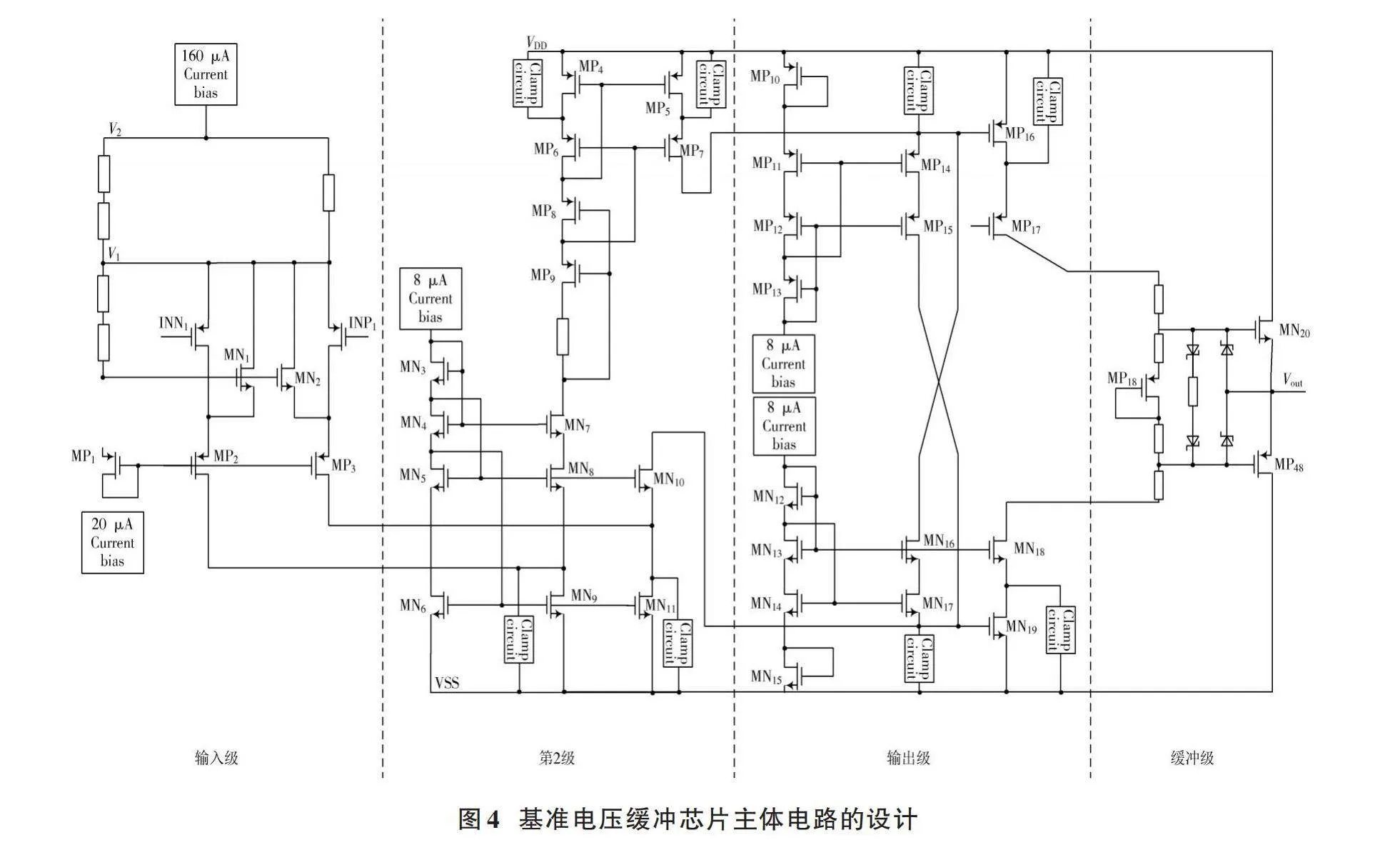

2.1.2" 主體電路設計

圖4所示為基準電壓緩沖芯片主體電路的設計。其總體運放由四級電路構成:輸入級采用PMOS管作輸入對。第二級采用共源共柵結構,構成了折疊式共源共柵的運放,可以實現較高的電壓增益和較大的帶寬,同時擁有較強的驅動能力。MN1、MN2作為啟動電路在電路穩定工作后立即關斷,使電路實現快速啟動的功能。

借助輔助定理計算圖4所示電路的電壓增益。

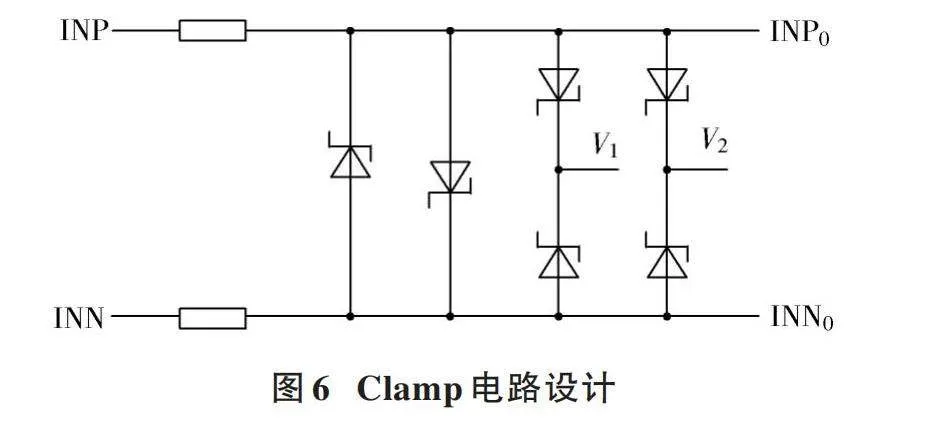

其中[Gm≈gMN1],而[Rout]為折疊式共源共柵極與共源共柵極輸出阻抗的并聯,采用典型值時近似等于:

[Rout≈gMP7rOP7rOP5//gMN10rON10?gMP2rOP2rON1//rON9] (1)

則電壓增益為:

[A1=gMN1Rout]" " " " "(2)

輸出級采用軌至軌Class AB結構[1,7],可以抑制交越失真現象,同時能夠在輸出接近供電電壓時進行穩定的放大,保持輸出信號的完整性,還可以提供較大的輸出電流以驅動較大的負載。為了減小輸出級電路的靜態電流受電源電壓影響的程度,采用MP14、MP15和MN16、MN17構成浮動電流源結構,為輸出級MP16、MP17和MN18、MN19提供電壓偏置,通過線性跨導環來確定靜態偏置電流。同時提供P管和N管輸出管柵極之間的一個電壓差值,使兩管同步導通,一起上拉下推。此輸出級的跨導[Gm≈gMP16+gMN19],輸出阻抗采用典型值時可以近似等于:

[Rout≈gMN18rON18rON19//gMP17rOP17rOP16]" (3)

增益[A2=GmRout]。

緩沖級采用Class B推挽輸出結構[8],由MN20、MP48兩個互補MOS管組成,分別處理信號的正半周期和負半周期,并可以進一步增強輸出級的電流驅動能力,使得整體電路能夠更好地驅動較大的負載。在整個工作周期內沒有靜態偏置電流,從而有效地減小能量損耗,降低靜態功耗。

故該緩沖放大器的總增益表示為[A=A1?A2]。

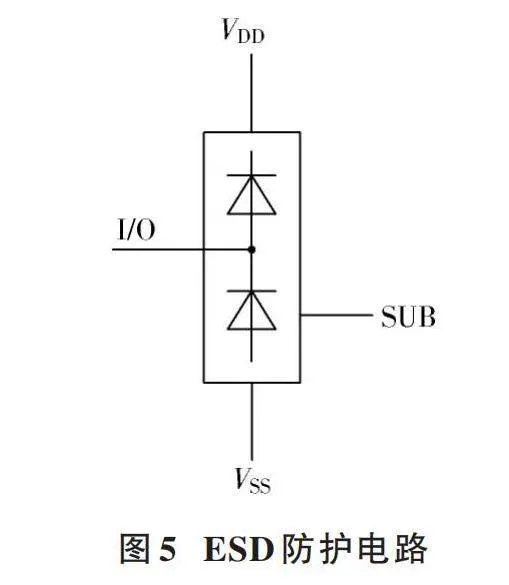

2.1.3" 全芯片靜電放電及過壓保護電路設計

ESD(靜電放電)是一種突發的、短暫的高能量事件。在實際的電子系統中,人體帶來的靜電或由外部各種因素導致的設備之間的靜電放電會對電子元器件造成損壞或者造成其性能退化[9?10]。為了提高電路的可靠性和穩定性,保護關鍵器件不受損壞,降低電路受到外部干擾的風險以及后期維護成本,本芯片在引腳I/O接口處設計了ESD防護電路,結構如圖5所示。高電壓將鉗位二極管導通,電流流經VDD,靜電放電將鉗制電流泄入地,實現正負電壓雙向的ESD防護。

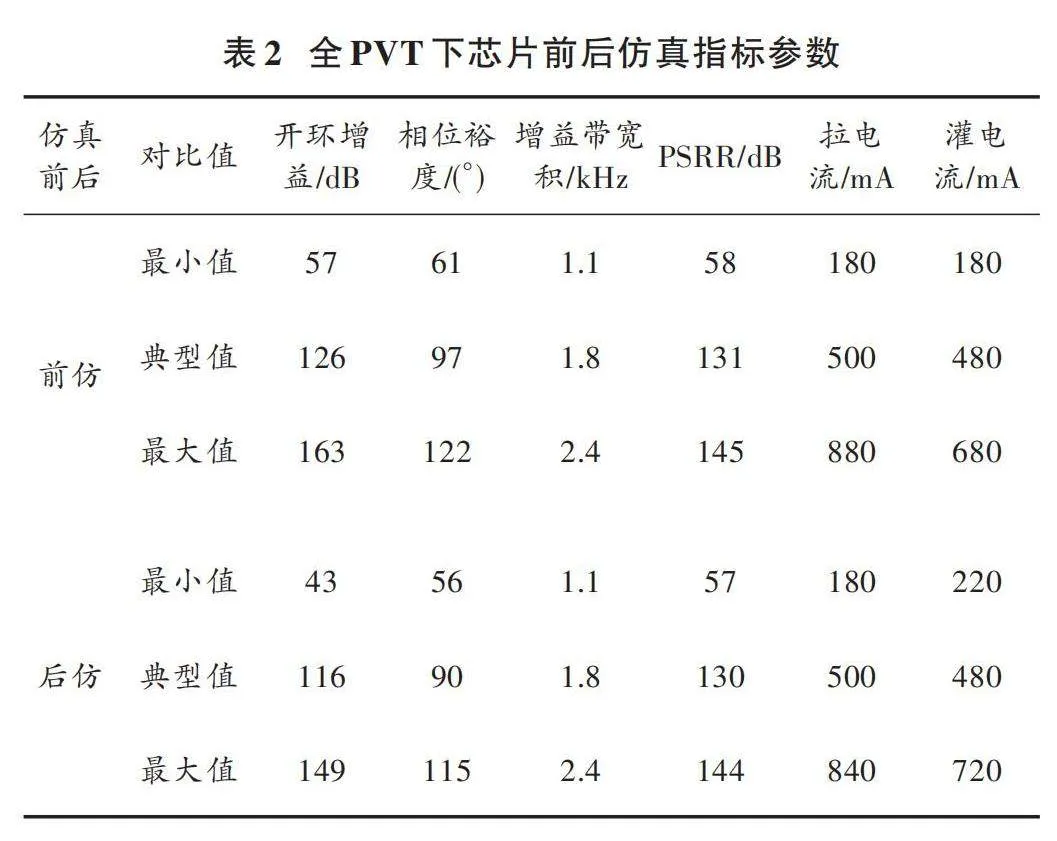

Clamp電路通常用于限制信號電壓的幅值,防止輸入信號的電壓超過一定的閾值,同時保護后續電路免受過大的電壓沖擊或干擾,確保電路中的敏感部件不會受到過電壓的損害,是一種過壓保護技術[11?12]。在實際使用過程中,電路容易受到來自于噪聲、ESD事件等突發性峰值信號的干擾,Clamp電路可以幫助限制這些峰值信號的幅值,在一定程度上保持信號的完整性,確保電路正常工作。本文芯片中,在輸入級設計的Clamp電路結構如圖6所示,利用穩壓二極管的反向擊穿特性來限制差分輸入的電壓差,以及限制V1、V2與INP0、INN0之間的電壓差在一個擊穿電壓范圍內。其他電路部分的Clamp電路由一組二極管連接的MOS串聯構成。

2.2" 電路前仿真結果

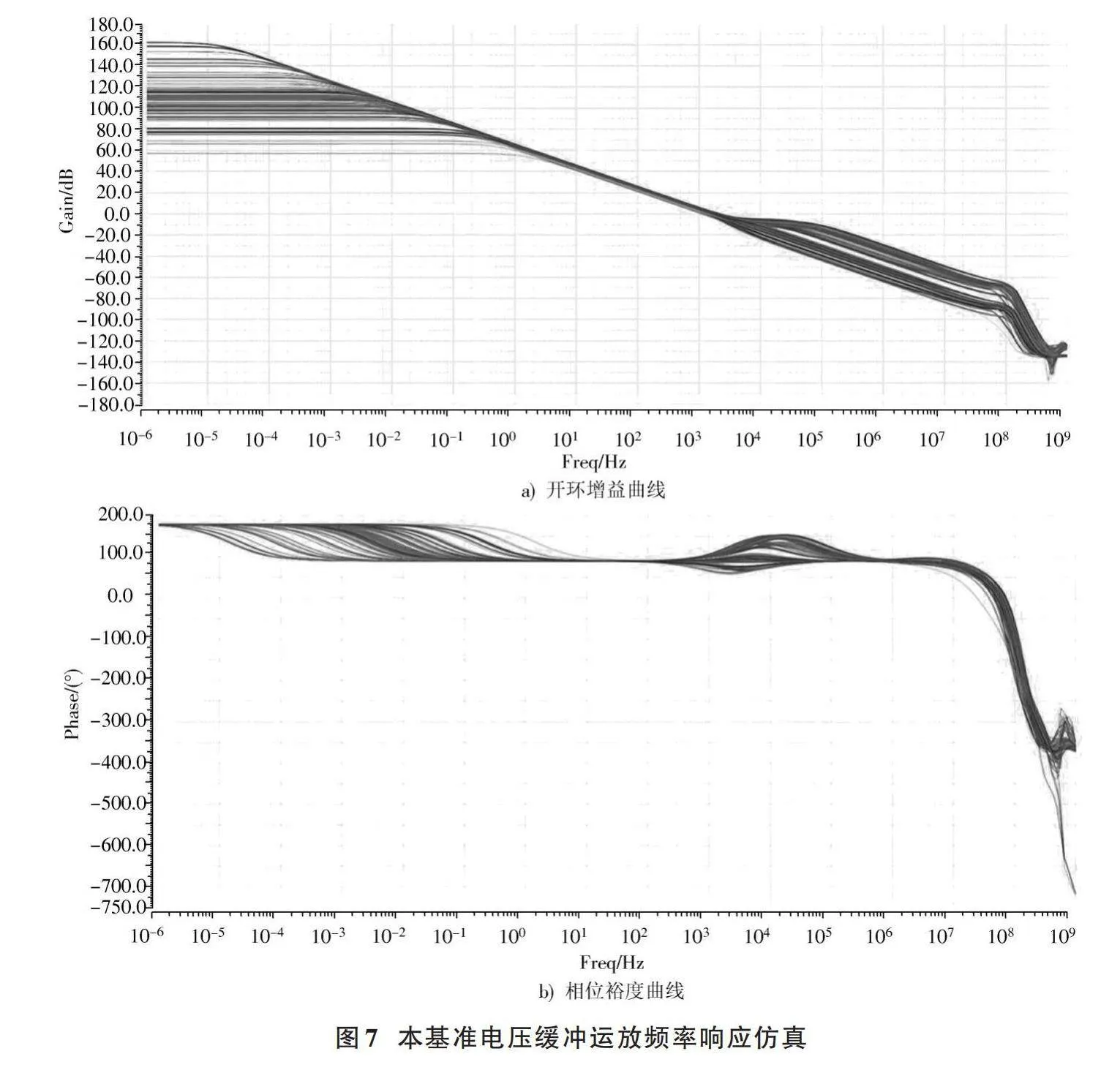

整體芯片由±5 V雙電源供電,工藝角遍歷tt、ss、ff,溫度遍歷-40~125 ℃,電容負載遍歷Cload=1 μF、10 μF,電流負載遍歷Iload=10 mA、100 mA,仿真環境分別模擬拉電流和灌電流兩種方式,進行全PVT的仿真。本基準電壓緩沖運放頻率響應仿真結果如圖7所示。

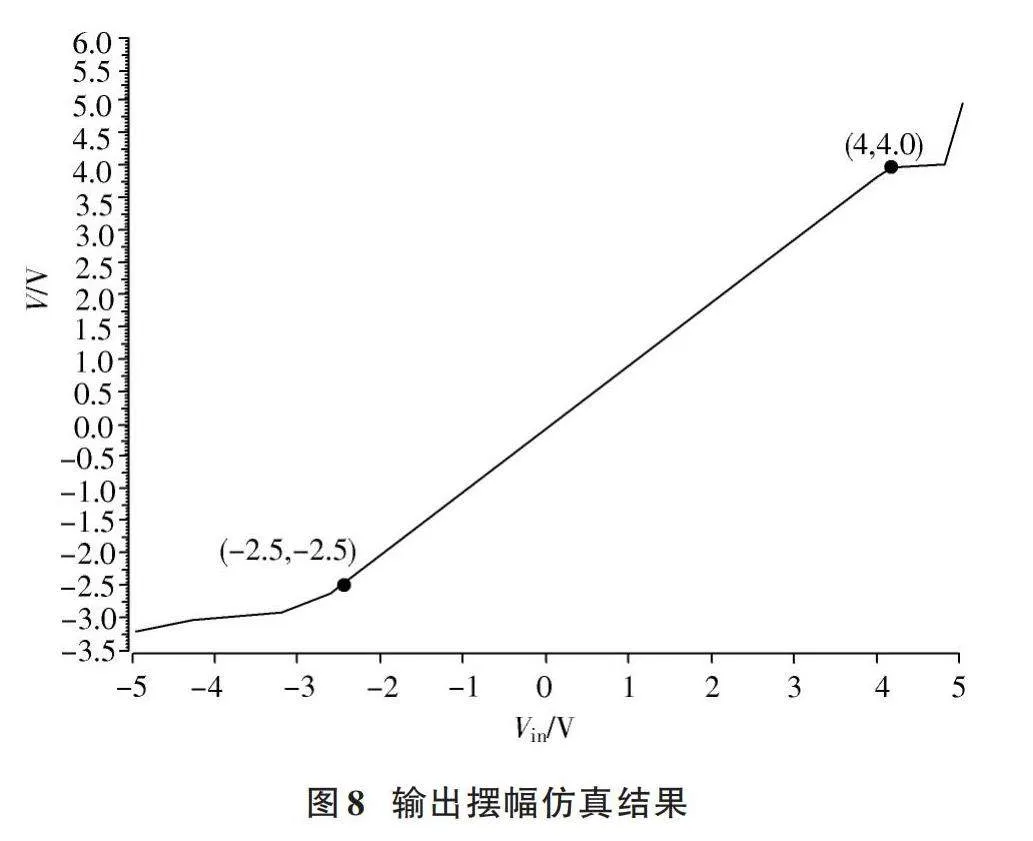

輸出擺幅仿真結果如圖8所示。

仿真結果顯示:輸出擺幅為-2.5~4 V。其中運放開環增益最小值為57 dB,最大值為163 dB,典型情況下為126 dB;相位裕度最小值為61°,最大值為122°,典型情況下為97°。

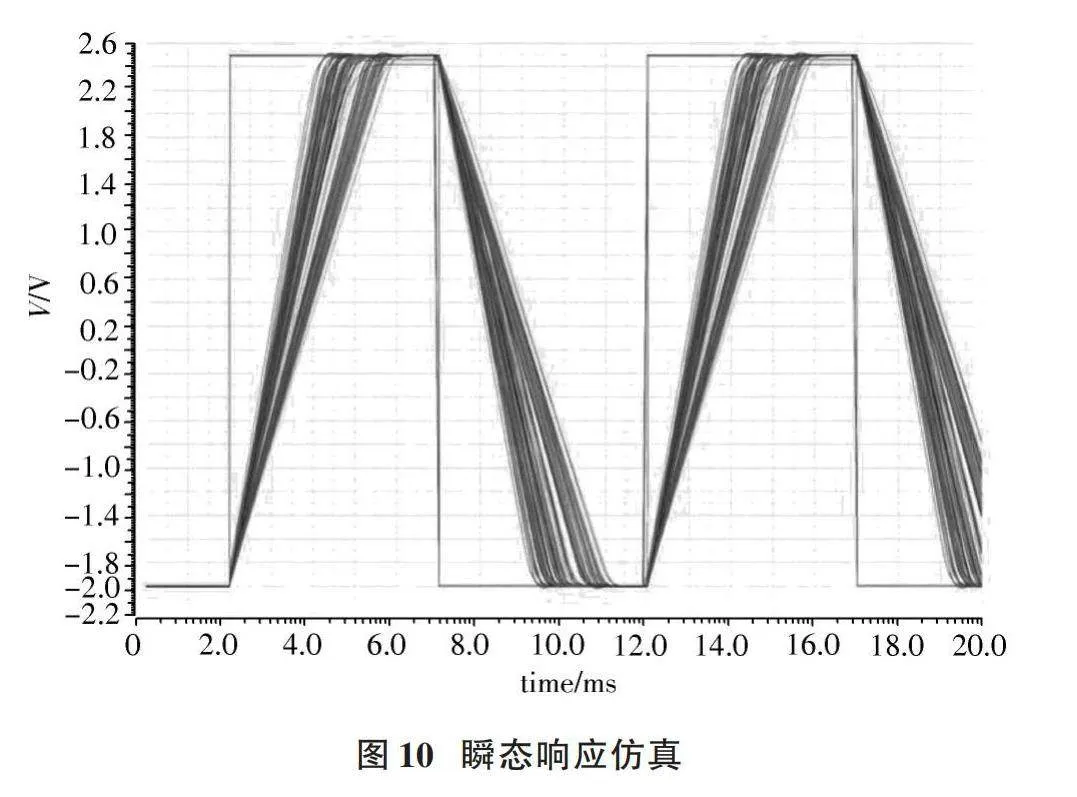

電源抑制比仿真結果如圖9所示。由圖9可知,電源抑制比最小為58 dB,最大為145 dB,典型值為131 dB。瞬態響應仿真結果如圖10所示。典型值下拉電流為500 mA,最低為180 mA,最高可達880 mA。灌電流最低為180 mA,最大可達680 mA,典型值下為480 mA。噪聲為448 nV/[Hz@100 Hz]、1 nV/[Hz@100" kHz]。

3" 版圖設計和后仿真

3.1" 芯片版圖設計

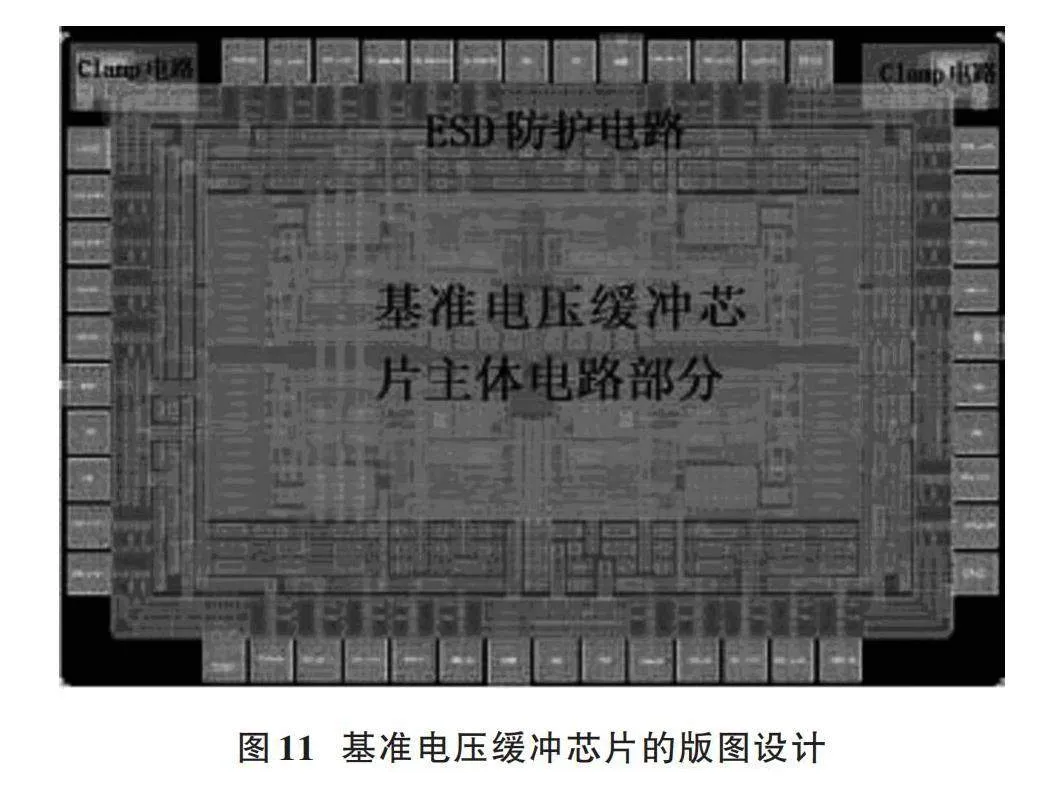

本文基于SMIC 0.18 μm CMOS工藝對基準電壓緩沖芯片進行了版圖設計,在同一個芯片上集成了4個CMOS電壓緩沖運算放大器。基準電壓緩沖芯片的版圖設計如圖11所示。

芯片尺寸為2 390 μm×1 660 μm,包含了主體電路模塊、ESD防護電路以及Clamp電路模塊等。

3.2" 芯片后仿真結果

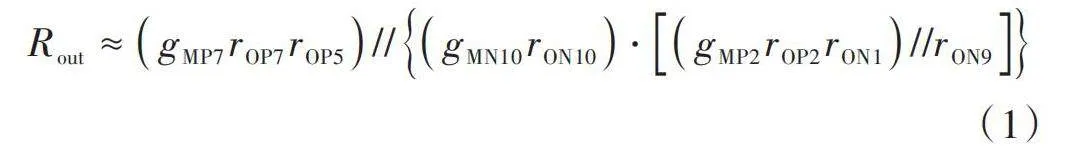

在與前仿真相同的仿真條件下,使用Calibre仿真工具進行后仿真。表2為在全PVT仿真下對芯片進行的前后仿真數據總結,并羅列出最大、最小值及典型值。

除此以外,輸出擺幅前后仿真均為-2.5~4 V,噪聲為448 nV/[Hz]@100 Hz、1 nV/[Hz]@100 kHz。總體結果表明,該電路具有高增益、高電源抑制比及低噪聲等特點,同時擁有很高的輸出驅動能力。因此,所提出的基準電壓緩沖芯片可以用于驅動如像素陣列等具有大電容負載的電路,并且性能優異。

與其他文獻中提出的電壓緩沖器所具有的性能參數進行對比,結果如表3所示。

由表3可以看出,本文所提出的電路的開環增益和電源抑制比(PSRR)遠高于文獻[13?15],輸出電壓范圍比較大,噪聲較小,特別是負載電容比其他電路大很多。這表明本文所設計的基準電壓緩沖芯片的關鍵性能表現優異,且擁有驅動大負載電容電路的突出能力。

4" 結" 語

本研究的目標是解決當前CMOS基準電壓緩沖器在驅動大電容負載電路時所面臨的可靠性問題和性能瓶頸,因此,提出了一種高性能的基準電壓緩沖芯片設計方案。該方案能驅動像素陣列并為其提供穩定可靠的參考電壓。本文介紹了該緩沖放大器的結構框架,設計了大小偏置電流產生電路和四級運放主體電路,增設了鉗位和防護電路。經過前后仿真驗證,本文設計的基準電壓緩沖芯片各項性能表現出色,具有較高的增益、PSRR和驅動能力,同時噪聲較低,能夠有效提高像素陣列的工作性能和圖像質量。因此,本研究具有重要的理論意義和實際應用價值。未來的研究方向將聚焦于進一步提高基準電壓緩沖芯片的性能,并探索該芯片在其他電子器件中的應用潛力。

注:本文通訊作者為劉成。

參考文獻

[1] 馬志寅,李富華,陳天昊.基于差分翻轉電壓跟隨器的AB類緩沖器設計[J].電子與封裝,2022,22(4):37?40.

[2] VENEZIA C, RIZZO A, PENNISI S. 15 nA CMOS analog voltage buffer insensitive to PVT variations [C]// 2023 18th Conference on Ph.D Research in Microelectronics and Electronics (PRIME). Valencia, Spain: IEEE, 2023: 73?76.

[3] ARSLAN E, MINALI S. Low?power and high?speed CMOS voltage buffer for flat panel displays [C]// 2022 19th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI?CON). Prachuap Khiri Khan, Thailand: IEEE, 2022: 1?4.

[4] 張春茗,王夢海,嚴展科.一種亞閾值有源共源共柵補償運算放大器[J].現代電子技術,2020,43(6):13?17.

[5] 王昌皓,熊祥正.微帶結構的高增益低噪聲放大器的設計[J].現代電子技術,2023,46(3):167?172.

[6] 吳曉文,陳曉東,劉軼.2~8 GHz超寬帶低噪聲放大器設計[J].現代電子技術,2019,42(7):108?111.

[7] 崔明輝,王星,李娜,等.一種基于CLASS?AB類運放的無片外電容LDO設計[J].電子技術應用,2023,46(9):53?57.

[8] CAGDAS E, ANIKTAR H, SAVCI H S, et al. An X?Band class?B push?pull power amplifier on a 0.25 μm SiGe?C process [C]// 2023 30th IEEE International Conference on Electronics, Circuits and Systems (ICECS). Istanbul, Turkiye: IEEE, 2023: 1?4.

[9] 陳逸舟.集成電路的ESD防護技術研究[D].蘇州:蘇州大學,2013.

[10] 許嘉航.集成電路ESD的防護關鍵技術研究[J].黑龍江科學,2023,14(16):156?158.

[11] 鄧志豪,成建兵,李瑛楠,等.一種快關斷的新型ESD電源箝位電路[J].微電子學,2021,51(6):889?893.

[12] 唐曉柯,李振國,郭海兵,等.一種用于繼電保護的電源鉗位靜電放電電路[J].半導體技術,2021,46(9):675?679.

[13] 梁清華,陳洪雷,丁瑞軍.用于IRFPA ROIC的高性能緩沖器模塊的設計[J].半導體光電,2017,38(4):566?570.

[14] CHOI J, PARK J, JEONG W, et al. Design of LDO linear regulator with ultra low?output impedance buffer [C]// International SoC Design Conference. Busan, South Korea: IEEE, 2010: 420?423.

[15] CARRILLO J M, DOMíNGUEZ M A, DUQUE?CARRILLO J F, et al. Low?voltage wide?swing fully differential CMOS voltage buffer [C]// 2011 20th European Conference on Circuit Theory and Design (ECCTD). Link?ping, Sweden: IEEE, 2011: 122?125.