硬件安全測試基準集及其管理體系的研究與評估

摘要:硬件安全作為網絡安全的關鍵部分,其安全性對整個系統至關重要。然而,由于硬件設備種類繁多、生命周期長,一旦出現問題修復成本極高,且目前硬件安全領域缺乏標準化測試方法,導致測試結果難以比較和驗證。設計了一種基于Web技術的硬件安全測試基準集管理系統,利用Flask框架和關系型數據庫實現數據完整性和安全性,并通過Yosys工具對測試基準集進行綜合評估,以識別安全風險并優化硬件設計,為硬件安全領域的標準化和進步提供支持。

關鍵詞:硬件安全;基準集;Web應用;數據庫;測試向量

中圖分類號:U467.5 收稿日期:2024-07-25

DOI:10.19999/j.cnki.1004-0226.2024.11.019

1 前言

隨著互聯網的普及和科技的快速發展,網絡安全問題日益嚴峻,尤其是硬件安全問題,它直接關系到整個系統的安全性。硬件安全不僅涉及確保計算設備的物理部件不存在漏洞,還涉及防護未經授權的訪問和物理篡改。鑒于硬件設備的多樣性和長生命周期,一旦出現安全問題,修復成本極高。目前,硬件安全領域缺乏標準化的測試方法,導致測試結果難以比較和驗證。本文通過設計一種測試集管理系統,實現硬件安全測試基準集的數據庫管理。在此基礎上,通過對Trust-Hub和Cryptographic Hardware Project中的測試基準集進行綜合結果分析,提供了硬件安全性能評估和優化的有效方法,還為硬件安全研究提供了數據支持和分析視角。

本文首先深入分析探討硬件安全測試基準集的設計內容;其次詳細介紹測試集管理系統的體系架構設計,從數據庫管理需求分析出發,設計測試基準集數據庫,并討論后端框架與模塊化設計;再次則通過利用數據庫中的測試基準集,使用開源工具Yosys進行綜合,進行了實驗評估;最后對本文工作進行了總結回顧,對未來工作內容進行了展望。通過這些章節的深入研究,旨在為硬件安全領域提供標準化的測試工具和方法,推動該領域的技術進步和創新。

2 硬件安全測試基準集研究

2.1 木馬測試基準集

硬件木馬(Hardware Trojan,HT)檢測技術是確保集成電路(Integrated Circuits,ICs)安全性的重要手段。隨著半導體技術的發展和全球化的制造流程,硬件木馬的威脅日益嚴重。硬件木馬是惡意植入電路中的隱蔽組件,可能在特定條件下激活,導致數據泄露、系統失效或永久性損壞。下面從測信道分析、門及特性評估、形式化驗證三個方面對硬件木馬檢測技術進行詳細介紹。

側信道分析(Side-Channel Analysis,SCA)是一種通過分析電路的物理側效應來檢測硬件木馬的方法。這種方法考慮了木馬電路對功耗、時序、熱量、面積、輻射等的影響。例如,在文獻[1]中,提出了一種基于路徑延遲測量的高效硬件木馬檢測方法,該方法能夠在最壞工藝變化下實現99%的木馬檢測準確率,精度達到0.001 ns。該方法不需要激活木馬,也不需要增加電路開銷,能夠有效分析所有易受木馬攻擊的路徑。

門級特性評估(Gate-Level Netlist Analysis)是通過分析門級網表的特性來檢測硬件木馬的方法。這種方法側重于分析木馬對電路結構特性的影響。例如在文獻[2]中,提出了一種數據增強方法,通過用邏輯等價的門替換硬件木馬電路中的門來增強機器學習基礎的硬件木馬檢測。實驗結果表明,該方法成功地提高了所有分類器的真正例率。

形式化驗證(Formal Verification)是一種通過數學方法來證明硬件設計滿足預定安全屬性的技術。這種方法可以在設計階段就檢測出潛在的硬件木馬,而不需要等到硅后階段。文獻[3]提出了一種基于屬性的形式化安全驗證方法,用于硬件木馬檢測。該方法在Coq定理證明環境中形式化了細粒度的門級信息流模型,以證明硬件設計的安全性屬性。與現有的寄存器傳輸級(RTL)信息流安全模型相比,該模型只需要將少量邏輯原語轉換為其形式化表示,無需支持豐富的RTL HDL語義或處理復雜的條件分支或循環結構。實驗結果表明,該方法能夠有效地檢測并定位木馬。

2.2 密碼核測試基準集

DES(Data Encryption Standard)是一種對稱密鑰加密算法,由美國國家標準與技術研究院(NIST)于1977年發布。它基于56位密鑰長度,并通過16輪的Feistel網絡來加密和解密數據。DES的密鑰生成過程包括密鑰生成和密鑰調度,其中密鑰生成過程將64位的密鑰轉換為16個48位的子密鑰,每個子密鑰用于Feistel網絡的一輪。DES的加密過程包括初始置換、16輪的Feistel網絡、最終置換。在每一輪中,數據塊被分為左右兩部分,左半部分與子密鑰進行異或操作,然后通過S盒和置換操作進行變換,最后與右半部分進行異或。解密過程與加密過程類似,但子密鑰的使用順序是反向的。DES在加密和解密過程中使用初始置換(IP)和最終置換(FP),這些置換表用于重新排列數據塊,增加算法的復雜性。同時,DES使用8個S盒,每個S盒是一個4×16的查找表,用于非線性變換,增強密碼系統的安全性。由于其密鑰長度較短,DES容易受到暴力破解攻擊。DES存在一些已知的弱點,如S盒的線性和非線性特性,以及差分攻擊和線性攻擊。因此,由于安全性的考慮,DES已經被更安全的算法如AES(Advanced Encryption Standard)所替代。

AES密碼核的功能要求是支持數據的加密和解密,同時需要滿足特定的性能指標,包括處理速度、功耗和資源占用。AES支持128位、192位和256位的密鑰長度,這為不同安全級別的需求提供了靈活性。加密過程包括密鑰擴展、輪密鑰加、字節代換、行移位和列混淆等步驟,而解密過程則是這些步驟的逆向執行。AES算法的密鑰擴展是加密過程的起點,它將原始密鑰轉換成一系列輪密鑰,這些輪密鑰在后續的加密輪中使用。引入一個初始化向量(IV)與原始數據的第一個塊結合,以防止相同的明文數據塊產生相同的密文塊。加密過程開始,它由多個輪組成,輪數取決于密鑰的長度。在每一輪中,首先執行的是加輪密鑰操作,即將當前數據塊與當前輪密鑰進行異或操作。緊接著,進行字節代換,對每個字節應用一個非線性變換,通常是S盒。之后,行移位操作對數據塊的行進行移位,不同的行移動的字節數不同。最后,列混淆操作對數據塊的每個列進行線性變換,增加了混淆性。在經過所有預定輪次的處理之后,最后一輪省略了列混淆步驟,只執行加輪密鑰、字節代換和行移位。這樣經過所有輪的處理,得到的最終數據塊即為加密后的密文。解密過程與加密過程相似,但輪密鑰的應用順序相反,并且使用逆向的字節代換和逆向的列混淆。在解密的每一輪中,首先執行逆向加輪密鑰操作,然后是逆向字節代換,接著是逆向行移位,最后是逆向列混淆。解密的最后一輪只包括逆向加輪密鑰、逆向字節代換和逆向行移位。

2.3 硬件安全測試基準電路

硬件測試基準電路是評估硬件設計和測試方法的重要工具,它們分為組合邏輯和時序邏輯兩大類。組合邏輯基準電路,如加法器和比較器,其特點是輸出僅依賴于當前的輸入值,而時序邏輯基準電路,例如觸發器和計數器,則包含存儲元素,其輸出不僅取決于當前輸入,還與歷史狀態有關。在設計和實現方面,組合邏輯的設計重點在于優化邏輯表達式和減少邏輯層次,以提升速度和減少占用面積。而時序邏輯設計則需重點考慮時鐘管理和同步問題,確保數據在時鐘邊沿能被正確捕獲。測試方法上,組合邏輯測試側重于確保所有可能的輸入組合都被測試到,以覆蓋所有邏輯路徑;相對地,時序邏輯測試則側重于驗證時鐘管理和狀態轉換的正確性。

故障模型方面,組合邏輯的故障類型包括短路、開路和邏輯錯誤等,通過使用基于故障的測試向量可以檢測這些故障。時序邏輯的故障類型則涵蓋時鐘偏差和建立時間/保持時間違規等問題,需要通過時序測試向量和狀態遷移分析來檢測。在性能指標上,組合邏輯的性能主要通過延遲和速度來衡量,而時序邏輯的性能則側重于時鐘頻率以及建立時間和保持時間。在仿真和驗證環節,組合邏輯仿真主要檢查邏輯功能的正確性,而時序邏輯仿真則關注時序行為和時鐘管理[4]。

硬件實現時,組合邏輯通常使用標準單元工藝實現,重點在于優化布局和布線以減少延遲;時序邏輯實現則需要考慮時鐘分配和時鐘樹設計,確保時序要求得到滿足。在應用領域,組合邏輯廣泛應用于處理器的算術邏輯單元和數據路徑,而時序邏輯則用于存儲器接口、微處理器的控制單元和數字信號處理等[5]。

2.4 小結

本章深入分析了硬件安全測試基準集的關鍵技術,涵蓋了從硬件木馬的檢測技術,如側信道分析、門級特性評估和形式化驗證,到密碼核測試基準集的DES和AES算法的安全40c5832104da1f4fc697bebf2844218d性分析。這些技術不僅提高了集成電路的安全性,還確保了設計階段的安全性驗證。此外,硬件測試基準電路的設計和測試方法,包括組合邏輯和時序邏輯的優化、故障模型分析以及性能指標考量,都是確保硬件設計可靠性和安全性的關鍵環節。

3 測試基準集管理系統體系架構

3.1 數據庫管理需求分析

制定Web數據庫管理框架是本課題的一個關鍵研究目標,旨在通過Web技術提高硬件安全測試基準集的可訪問性、交互性和管理效率。以下是該目標的詳細內容:a.用戶登錄系統;b.在用戶登錄或進行敏感操作時,提供安全提示;c.數據庫連接;d.數據展示;e.用戶交互進行操作;f.文件瀏覽、上傳與下載。

3.2 數據表結構及字段說明

userinfo表:用于存儲用戶數據,即用戶名和用戶密碼,在用戶登錄該管理系統時進行調用驗證。

database_table表:這個表可以被視為一種“數據表關聯表”。它的作用是將數據庫名和表名進行映射,從而建立它們之間的關系。該表用于多數據庫環境中,用來追蹤和關聯各個數據庫中的表。這些記錄表明了不同數據庫與其內部表的對應關系。例如,記錄('epfldata','arithmetic benchmarks')表示'epfldata'數據庫中有一個名為'arithmetic benchmarks'的表。這樣的映射對于數據庫管理系統來說非常有用,因為它提供了一種集中的方式來查看和管理數據庫和表之間的關系,尤其是在大型系統中,可能有多個數據庫和大量表存在時。此外,這種映射表也有助于在進行數據庫遷移、同步或管理任務時,能夠快速識別和訪問特定的數據庫和表。

由于測試基準集來自6個不同的源網址,因此具體數據表會根據源數據的不同而構造不同的數據表結構,以下為以來自Trust Hub的106個測試基準集構造的trusthubdata表,字段如下:

a.ID:唯一標識符,整型,主鍵。

b.Name:基準測試的名稱,如'AES-T100',字符串類型。

c.Insertion phase:插入階段,指的是設計或制造階段,字符串類型。

d.Abstraction level:抽象級別,如'Register Transfer level'或'Gate-level',字符串類型。

e.Activation mechanism:激活機制,如'Always on'或'Triggered Internally',字符串類型。

f.Effects:效果,如'Leak Information'或'Denial of Service',字符串類型。

g.Location:位置,指的是受影響的硬件組件,字符串類型。

h.Physical characteristics:物理特性,描述了基準測試的物理特性,字符串類型。

arithmetic benchmarks表:

a.ID:唯一標識符,整型,主鍵。

b.Name:基準測試的名稱,如'Adder',字符串類型。

c.Inputs:輸入端的數量,字符串類型。

d.Outputs:輸出端的數量,字符串類型。

e.LUT-6 count:輸入查找表的數量,字符串類型。

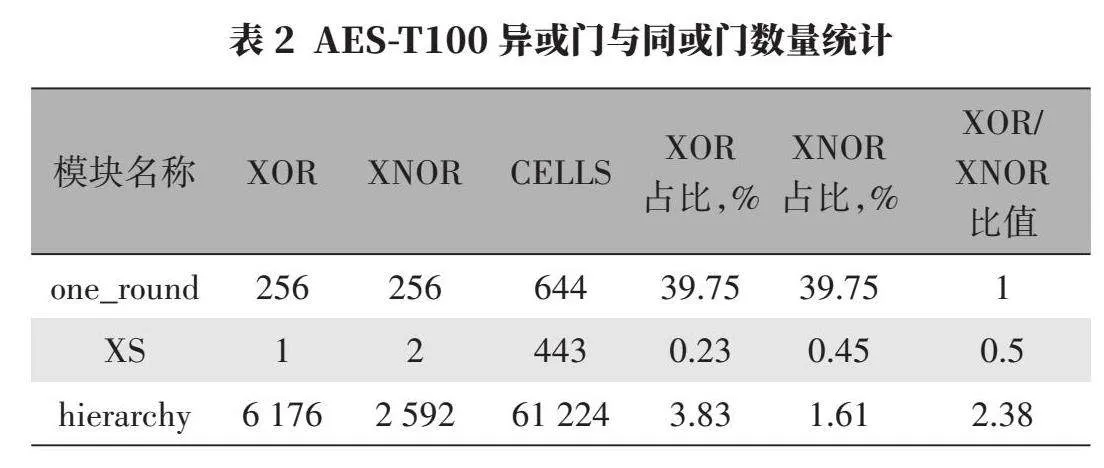

f.Levels:邏輯電路的級數,字符串類型。該數據表結構及部分數據如表1所示。

3.3 模塊化接口設計

下面將后端Flask框架劃分為四大關鍵模塊,即用戶認證模塊,數據庫連接模塊,數據庫操作模塊和文件系統管理模塊進行分析。

用戶認證模塊,該模塊處理用戶的登錄和會話管理。

該模塊接口設計分析如下:

a.登錄(/login):通過POST方法接收用戶名和密碼,驗證用戶并設置會話。

b.獲取會話(/getSession):通過GET方法獲取當前會話的信息。

數據庫連接模塊,該模塊負責從conn_info.json文件中讀取數據庫連接參數,并根據需要返回適當的數據庫連接配置。

該模塊接口設計分析如下:

a.數據庫連接參數(get_db_connection_params(db_name)):此函數根據提供的數據庫名稱返回數據庫連接參數。它處理了字典配置,并將游標類設置為DictCursor。

b.獲取數據庫表列表(/get-tables):通過POST方法返回指定數據庫中的所有表的列表。

c.獲取表索引(/get-indexes):通過POST方法返回指定表的所有索引。

數據庫操作模塊,如圖1所示,該模塊負責與數據庫的所有交互,包括數據的增刪查改。

該模塊接口設計分析如下:

a.添加數據(/add/bm):接收JSON數據并通過POST方法插入到數據庫表中。允許用戶通過POST請求添加新的基準集。

b.刪除數據(/delete/bm):根據提供的名稱,通過POST方法從數據庫表中刪除記錄。允許用戶通過POST請求刪除特定的基準集。

c.搜索數據(/search/bm):根據提供的名稱,通過POST方法搜索數據庫表中的記錄并返回結果。允許用戶通過POST請求搜索基準集。

d.顯示數據(/show-data):通過POST方法查詢并返回數據庫表中的所有記錄。用于展示指定表中的所有數據。

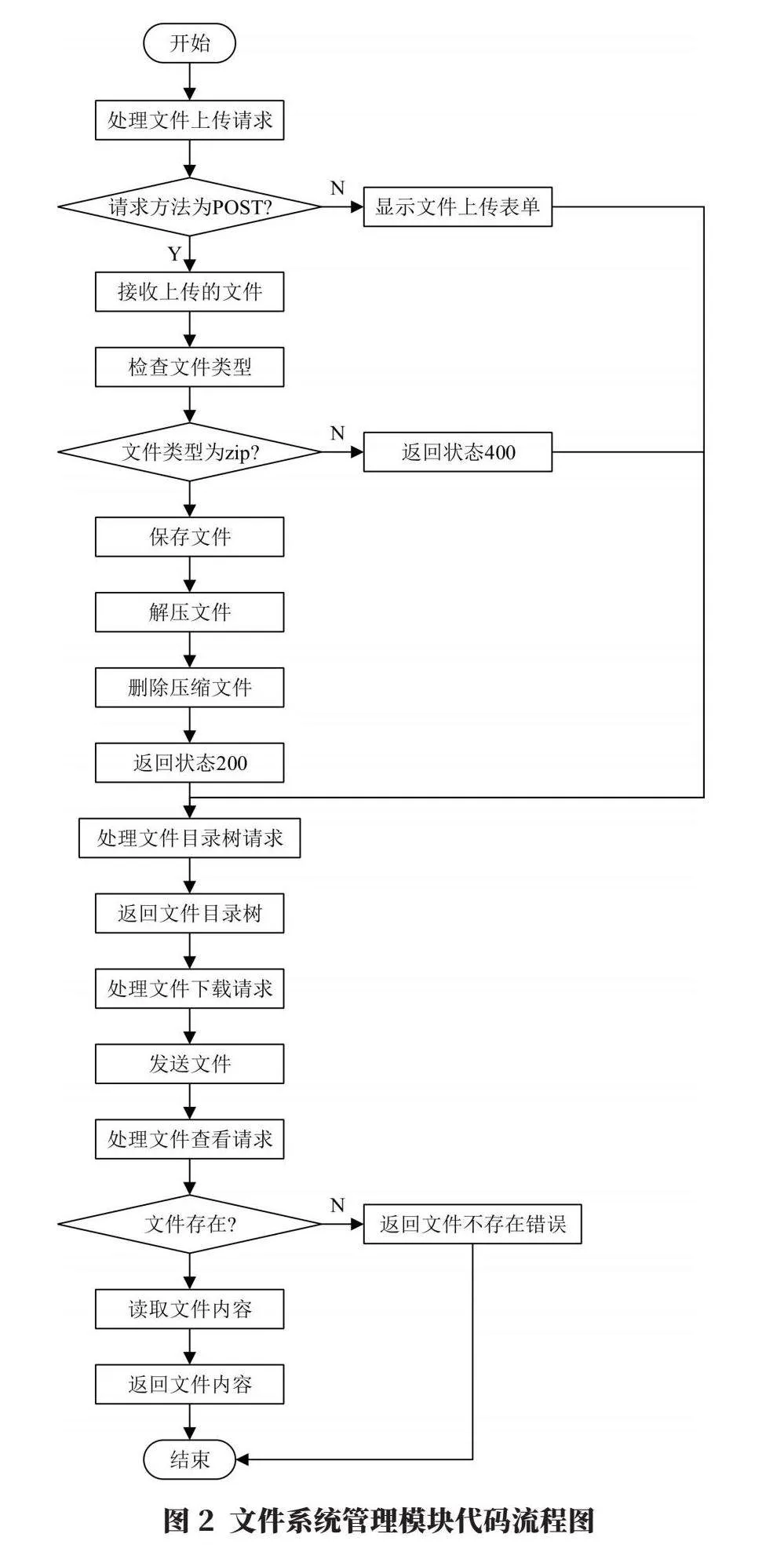

文件系統管理模塊,如圖2所示,此模塊包含處理文件目錄和文件操作的函數。

對于該模塊進行接口設計分析如下:

a.構建文件樹(build_file_tree):構建指定目錄的文件樹結構。

b.文件頁面(/files):渲染文件管理頁面。

c.獲取目錄(/get_directory):通過GET方法返回指定目錄的文件樹結構。

d.下載文件(/download/<filepath>):通過GET方法允許用戶下載文件。

e.查看文件(/view/<filepath>):通過GET方法允許用戶查看文件內容。

f.文件上傳(/upload):通過POST方法處理文件上傳,并提供解壓功能。

3.4 小結

本章集中討論了如何通過Web技術優化硬件安全測試基準集的數據庫管理。首先,明確了系統的核心需求,包括用戶登錄、安全提示、數據庫連接、數據展示以及文件操作等。詳細描述了數據表的結構,如`userinfo`和`trusthubdata`,以及它們如何支持系統的數據存儲需求。在后端開發方面,Flask框架因其輕量級和靈活性被選用,根據功能將后端劃分為用戶認證、數據庫連接、操作和文件系統管理等模塊,每個模塊都有清晰的接口設計。

4 硬件安全測試集實驗評估

本章旨在探討使用開源工具Yosys對現有的硬件測試基準集進行綜合,對得到的門級網表進行分析評估。Yosys作為一個開源的硬件描述語言(HDL)綜合工具,它在集成電路設計和驗證過程中扮演著至關重要的角色。通過Yosys的綜合過程,設計者能夠將高級的HDL代碼轉化為門級網表,通過使用Yosys,對數據庫中的測試向量進行代碼綜合,選擇了部分測試樣例進行實驗評估,對生成的門級網表進行分析。

實驗環境為Ubuntu 22.04,Tabby CAD Suite 2024-05-20版本的工具集成了Yosys的所需環境,從GitHub下載該版本進行安裝。配置完成后在安裝路徑下輸入Yosys命令即可開始使用Yosys進行綜合。

4.1 測試工具Yosys功能概述

Yosys是一個開源用于電路的邏輯綜合的框架,支持多種硬件描述語言包括Verilog和VHDL,能夠將這些高級語言代碼轉換成較低抽象層次的電路表示如門級網表[6]。Yosys的主要功能包括以下幾點:

a.語法解析:Yosys能夠解析Verilog和VHDL代碼,能夠執行從行為級到寄存器傳輸級、邏輯門級和物理門級的綜合,允許用戶讀取和處理大部分現代Verilog代碼,構建電路的內部表示。

b.邏輯優化:Yosys使用ABC(A System for Sequential Synthesis and Verification)工具提供了一系列的邏輯優化算法,用于簡化電路結構,消除冗余邏輯,從而提高電路的性能。

c.邏輯映射:Yosys可以將電路映射到特定的庫單元,如邏輯門和觸發器,生成門級網表。Yosys可以在網表級別(RTL、邏輯、門)執行各種操作,并支持將Verilog轉換為其他格式(如BLIF、BTOR等)[7-8]。

4.2 綜合流程詳解

綜合分為5個關鍵的步驟:

a.讀入Verilog代碼,這里需要將所有Verilog文件進行讀取,否則會出現找不到module的情況。

b.檢查層次結構并設置頂層。

c.執行synth綜合命令。在Yosys中,synth命令用于執行合成過程,使用不同的后綴則指定了不同的目標設備或平臺。在本研究中統一使用synth生成適用于多種FPGA或CPLD平臺的網表。

d.使用opt_clean命令可以對網表進行優化,主要作用是移除未使用的單元和連線。

e.執行write_verilog指令將設計寫入Yosys內部文件格式。

如果需要,還可以繼續執行show命令顯示xdot格式的網絡圖,由于測試基準集的復雜性高,綜合之后的圖像極大且生成效率較低,同時本文重點在于對測試集進行綜合并做簡單優化后的輸出結果進行分析,重點關注門級電路的結構與特點,所以不進行之后的步驟。

4.3 測試樣例實驗評估

4.3.1 AES-T100測試向量

對AES-T100木馬的綜合測試。AES-T100木馬利用了擴頻通信(Spread Spectrum Communications,SSC)的概念來創建一個隱蔽信道,這通常用于無線通信中以提高信號的抗干擾能力。通過這種方法,單個比特的泄露被分布到多個時鐘周期,從而降低了被檢測的可能性。

為了實現這一過程,木馬采用了偽隨機數生成器(PRNG),它初始化為一個預定義的值來創建一個CDMA(Code-Division Multiple Access,碼分多址)碼序列。這個碼序列隨后用于XOR調制秘密信息比特,將秘密信息與碼序列相結合,生成一個調制后的序列。

接下來,調制后的序列被轉發到一個泄露電路(Leakage Circuit,LC)。LC由8個相同的觸發器(flip-flop)元素組成,它們連接到XOR門的單一輸出,模仿一個大電容。這種配置允許在電源側信道中建立一個隱蔽的CDMA信道,通過這個信道,木馬能夠將密鑰信息泄露出去。整個機制的設計確保了木馬的隱蔽性和持續性,因為PRNG的預定義初始化和CDMA碼序列的XOR調制使得泄露的信息難以被追蹤和分析。同時,LC的配置進一步增強了信道的隱蔽性,使其能夠在不被注意的情況下持續泄露密鑰信息。

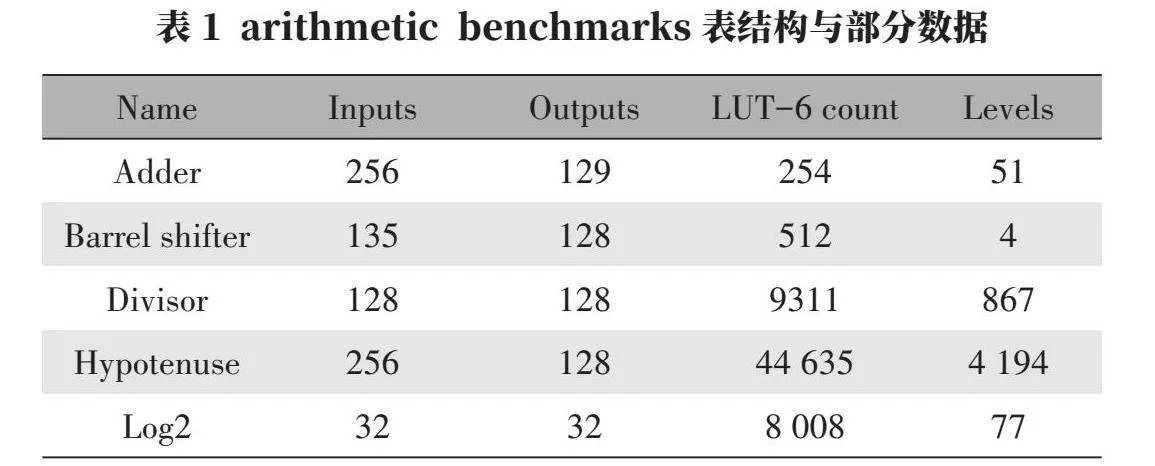

資源使用和總線位的統計顯示aes_128模塊擁有35個總線和4 353位,在邏輯單元方面,詳細列出了各種邏輯門的數量,包括AND、OR、NOT、DFF(觸發器)、XOR等。aes_128模塊中,如表2所示,有256個D觸發器和128個XOR門,而one_round模塊則使用了包括D觸發器、XNOR和XOR在內的多種類型的邏輯門,這顯示了設計的復雜性。

層次結構上,aes_128模塊包含了expand_key_128、final_round和one_round等子模塊,這顯示了一個層次化的設計方案。同時,S4模塊在多個地方被重復使用,這表明設計中存在模塊化和代碼復用。對于XOR/XNOR門比例的統計與分析,aes_128模塊中有128個XOR門,在one_round中有256個XOR門和256個XNOR門。one_round中總門數量為644個單元,其中XOR門256個,占39.75%,XNOR門占39.75%。XOR/XNOR門比值為1,在one_round模塊中,這表明該模塊在執行AES算法的混合操作時高度依賴這些門。性能方面,XOR/XNOR門的比例意味著設計在執行位操作時效率較高,這對于加密算法來說是可以接受的。

4.3.2 DES密碼核

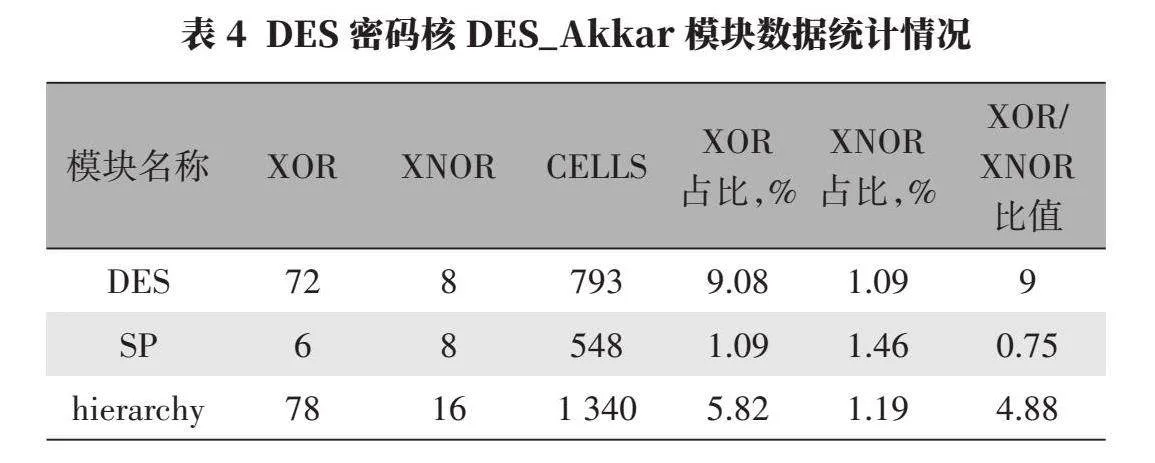

對DES密碼核的綜合測試。對于DES_ECB模塊,如表3所示,從資源使用的角度來看,DES模塊擁有578根總線和1 096位,而SP模塊則有532根總線和634位。在整個設計層次結構中,總線數量達到了1 110根,位數量為1 730位。此外,公共總線和位的數量分別為33根和653位,這表明設計中有一部分信號是共享的。邏輯單元的使用情況顯示,DES模塊擁有745個邏輯單元,而SP模塊有554個。整體來看,設計中共有1 298個邏輯單元,其中MUX(多路選擇器)的使用數量最多,這表明設計中存在大量的數據選擇邏輯。

設計中的并發操作可能通過大量的MUX和DFFE實現。層次結構方面,DES模塊包含一個SP模塊,形成了一個簡單的層次結構,有助于簡化設計和調試。特別地關注XOR/XNOR門的比例。在整個設計中,XOR門的數量為69個,而XNOR門的數量為26個,相對于總的1 298個邏輯單元來說,XOR門占比約為5.32%,XNOR門占比約為2.00%。XOR/XNOR門比值為2.65,雖然比例不高,但在電路性能和安全性方面扮演著重要角色。XOR操作在加密算法中是基礎,可以提供必要的數據變換功能,而XNOR門的使用則可以增加電路的安全性。

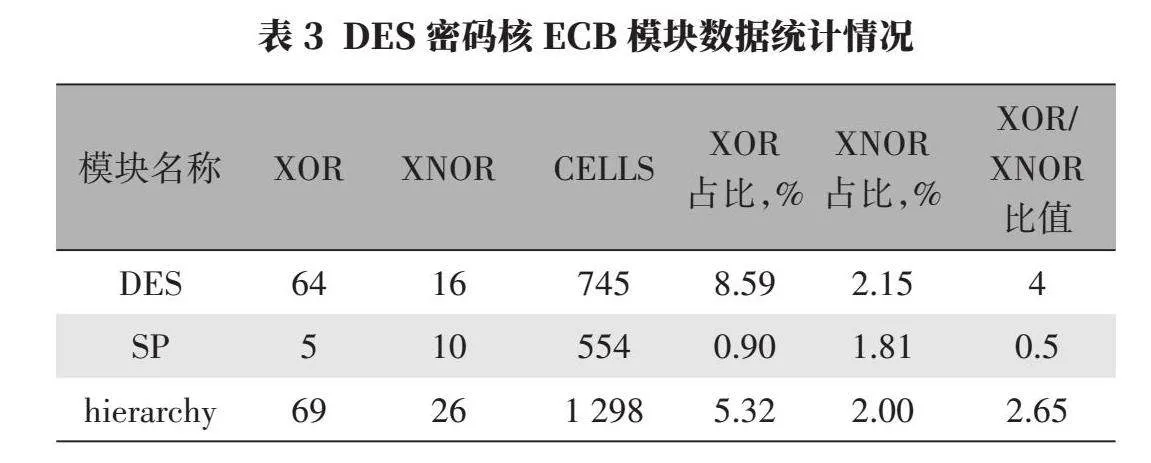

對于DES_ECB_Akkar模塊,如表4所示,從資源使用的角度來看,DES模塊擁有598根總線和1 336位,而SP模塊則有526根總線和628位,這表明兩個模塊在資源分配上有所不同。設計層次結構中,總線數量達到了1 124根,位數量為1 964位,公共總線和位的數量分別為34根和874位,這表明設計中有一部分信號是共享的,有助于減少資源的冗余。從邏輯單元角度分析,DES模塊擁有793個邏輯單元,而SP模塊有548個,整體設計中共有1 340個邏輯單元。其中,MUX(多路選擇器)的使用數量最多,這表明設計中存在大量的數據選擇邏輯,這是為了實現并發操作。

層次結構方面,DES模塊包含一個SP模塊,形成了一個簡單的層次結構,這有助于簡化設計和調試。對于XOR/XNOR門的使用比例情況,在整個設計中,XOR門的數量為78個,而XNOR門的數量為16個,相對于總的1 340個邏輯單元來說,XOR門占比約為5.82%,XNOR門占比約為1.19%。XOR/XNOR門比值為4.88,這一比例的增加可能意味著對數據變換功能的需求有所提升。此外,與DES_ECB_sta.txt相比,DES_ECB_Akkar_sta.txt中的邏輯單元數量略有增加,尤其是MUX的數量在SP模塊中從415增加到416,這可能反映了設計者對數據選擇邏輯的進一步優化。XOR門的數量在DES模塊中從64增加到72,在SP模塊中從5增加到6,整體從69增加到78,這進一步證實了對數據變換功能需求的增加。

4.4 小結

本章詳細闡述了在Ubuntu 22.04環境下使用Yosys的綜合流程,包括讀取Verilog代碼、檢查層次結構、執行綜合命令、優化網表以及輸出設計等關鍵步驟,為深入的分析提供了基礎。先對門級網表的結構和特點進行討論,包括輸入輸出端口、邏輯門、連線、時鐘控制等,以及層次化設計方法在管理復雜性中的重要性。門級網表不僅是電路設計的一個詳細藍圖,也是確保電路功能正確實現的關鍵。進一步地對作為實驗樣例的測試基準集進行了性能評估,涵蓋了資源使用情況、邏輯單元的類型和數量以及XOR/XNOR門的比例等。這些分析結果不僅幫助理解電路的性能表現,還揭示了設計優化的潛在機會。在安全性分析方面,Yosys的應用價值得到了凸顯,它幫助識別可能的安全風險,特別是在硬件木馬的檢測上。通過對綜合結果分析,設計者可以更好地理解電路的行為,并采取相應措施以提高安全性。

5 結語

本文主要完成了以下兩個核心部分的工作,它們分別對應于硬件安全研究測試基準集的構建和管理,以及使用Yosys工具進行的綜合分析。

a.設計并實現了一個基于Web技術的數據庫管理體系架構,旨在提升硬件安全測試基準集的存儲、下載和管理效率。系統核心需求涵蓋了用戶登錄、安全提示、數據庫連接、數據展示和文件操作等關鍵功能。在后端將系統劃分為用戶認證、數據庫連接、操作和文件系統管理等模塊,每個模塊都具備清晰的接口。同時,深入研究了關系型數據庫設計,特別強調了數據完整性和安全性,確保了關鍵數據表如trusthubdata的結構合理性。

b.詳細探討了使用開源工具Yosys對硬件測試基準集進行綜合分析的過程。Yosys作為一個在集成電路設計和驗證中扮演關鍵角色的HDL綜合工具,能夠幫助設計者將高級HDL代碼轉化為門級網表,為后續的布局布線、時序分析和性能評估打下基礎。在硬件安全領域,Yosys的應用價值得到了凸顯,它幫助識別可能的安全風險,尤其是在硬件木馬的檢測上。通過對測試基準集的綜合結果分析,能夠更好地理解電路的行為。

展望未來,本項目在硬件安全領域將更新測試基準集以適應發展,開發多維度評估工具,集成Yosys至Web應用提升效率,引入AI實現智能化管理。同時,將加強安全性和隱私保護,擴展測試范圍,開發高級Web數據庫管理,并強化安全措施。

參考文獻:

[1]He C,Hou B,Wang L,et al.A novel hardware Trojan detection method based on side-channel analysis and PCA algorithm[C]//2014 10th International Conference on Reliability,Maintainability and Safety (ICRMS).IEEE,2014:1043-1046.

[2]Zhan P,Shen H,Li S,et al.BGNN-HT:Bidirectional Graph Neural Network for Hardware Trojan Cells Detection at Gate Level[C]//2023 IEEE International Symposium on Circuits and Systems(ISCAS).IEEE,2023:1-5.

[3]Ponugoti K K,Srinivasan S K,Mathure N.Formal Verification Approach to Detect Always-On Denial of Service Trojans in Pipelined Circuits[C]//2021 28th IEEE International Conference on Electronics,Circuits,and Systems(ICECS).IEEE,2021:1-6.

[4]Neto W L,Possani V N,Marranghello F S,et al.Exact multi-level benchmark circuit generation for logic synthesis evaluation[C]//2018 31st Symposium on Integrated Circuits and Systems Design (SBCCI).IEEE,2018:1-6.

[5]Amarú L,Soeken M,Haaswijk W,et al.Multi-level logic benchmarks: An exactness study[C]//2017 22nd Asia and South Pacific Design Automation Conference(ASP-DAC).IEEE,2017:157-162.

[6]張茜歌,朱嘉誠,馬俊,等.基于故障傳播模型的硬件安全性與可靠性驗證方法[J].西北工業大學學報,2024,42(1):29-31.

[7]Wolf C, Glaser J,Kepler J.Yosys-a free Verilog synthesis suite[C]//Proceedings of the 21st Austrian Workshop on Microelectronics(Austrochip),2013:97.

[8]Shah D,Hung E,Wolf C,et al.Yosys+nextpnr:an open source framework from verilog to bitstream for commercial fpgas[C]//2019 IEEE 27th Annual International Symposium on Field-Programmable Custom Computing Machines(FCCM).IEEE,2019:1-4.

作者簡介:

關磊,男,1984年生,助理工程師,研究方向為整車測試。