基于CPLD的智能交通信號燈控制器

杜玉遠

CPLD是一種復雜可編程邏輯器件,具有高集成度、高密度、高速度的特點。將原有采用中小規模集成電路(LSI)設計的電路改造為由CPLD實現,既可以提高系統的集成度,又可以提高系統的可靠性。另外,由于CPLD具有在系統編程的功能,可在不改變印刷電路板的情況下改變電路功能,這樣可以為系統提供更多的冗余功能。本文介紹一種采用CPLD設計實現智能交通信號燈控制器方法,改變了原有控制器的體積較大、故障率高的缺點,并且增加了智能控制功能,使交通信號燈控制器具有更廣泛的適應性。

工作原理

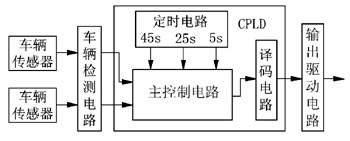

目前,在十字路口等待通行信號時,經常遇到在沒有車輛需要通行的路口方向是通行的信號,而在有車等待的路口方向卻是亮著紅燈的情況。這樣既浪費了司乘人員的時間,也浪費了馬路的效率。另外,由于汽車在等待信號時還會排出尾氣,也不利于環保。為此,在采用CPLD設計新型交通信號燈控制器時,在控制器中增加了車輛檢測電路。新的智能交通信號燈控制器的原理框圖如圖1所示。從圖1中可以看出,控制器由車輛檢測電路、定時電路、輸出驅動電路和主控制電路組成。車輛檢測電路由傳感器和波形整形器構成,整個車輛檢測電路有四路相同的支路構成,四個傳感器被安放在十字路口停車線的位置,當有車輛到達路口時,就由相應路口的傳感器產生請求通過信號,交通燈控制器根據此信號確定信號燈的變換。同時,還假設十字路口是由一條主干道和一條次干道匯合而成,并且主干道的車流量比次干道的車流量大。考慮到主、次干道車流量不同,主干道每次放行時間較長,次干道每次放行時間較短。當綠燈轉換成紅燈時,中間有一段黃燈亮的時間作為信號過渡期,以便車輛有時間停靠在停車線之外。這里設主、次干道放行時間分別為45s、25s,過渡時間為5s。定時電路用來完成這三種時間定時工作。主控電路將根據傳感器信號和定時時間的狀態控制信號燈的切換。輸出驅動電路由光電耦合器和繼電器驅動電路組成,用來控制信號燈開關。

智能交通信號燈控制器的實現

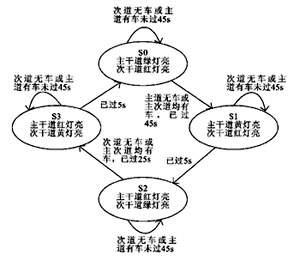

根據上述智能交通信號燈控制器的工作原理,可以得到如圖2所示的智能交通信號燈控制器的控制狀態轉換圖。為了設計實現智能交通信號燈控制器,引入邏輯變量和邏輯狀態表示圖2中的狀態轉換,主干道和次干道的傳感器檢測電路的輸出用邏輯變量A、B表示,A代表主干道的傳感器輸出有效,即主干道有車要求通過,B代表次干道的傳感器輸出有效,表示次干道有車要求通過。定時電路的輸出用邏輯變量L、S、P表示,它們分別代表45s、25s、5s定時器輸出狀態,當這些定時器定時時間到時,對應的邏輯變量L、S、P有效。主、次干道的通行狀態用S0、S1、S2、S3 四個狀態表示,其中用S0=00表示主干道通行狀態,用S1=01表示主干道停車狀態、用S2=11表示次干道通行狀態,用S3=10表示次干道停車狀態。用上述邏輯變量和邏輯狀態替換圖2中的邏輯狀態轉換圖,就可以得到用邏輯變量來表示的狀態轉換圖。這里由于篇幅有限省略此圖,根據狀態轉換圖,可以得到如表1所示的狀態轉換表。狀態轉換表中的Q1n 、Q2 n表示觸發器現態,Q1 n+1、Q 2n+1表示次態觸發器,表1中x代表任意態。

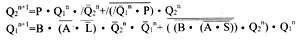

為實現表1所示的狀態轉換,根據表1 可以得到關于Q1n+1、Q2n+1的狀態方程,狀態方程經過化簡表示如下:

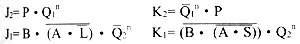

為實現這兩個的狀態方程,選用兩個JK觸發器作為狀態控制觸發器,將上述Q1n+1、Q2n+1的狀態方程與JK觸發器的特征方程對照處理,可以得到兩個JK觸發器的驅動方程如下:

根據上述表達式,在MAXPLUS Ⅱ系統中,采用原理圖輸入方式設計的主控電路圖如圖3所示。

在主控電路中,輸入信號L、S、P為定時電路的輸出,它們分別為45s、25s、5s定時時間到的輸出信號,在定時電路中,采用1Hz的信號作為時基信號,分別設計45進制,25進制和5進制三個計數器,就可以實現45s、25s、5s的定時信號、以25進制計數器為例,采用VHDL語言為輸入方式的源程序見本刊網站。其它進制計數器的實現只需修改計數器的終值就可以實現,這里不再重述。

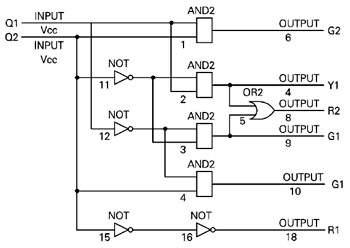

主控電路的狀態輸出經過譯碼電路,產生交通信號燈的開關控制信號。根據狀態控制電路所產生的不同狀態,來完成主干道和次干道的紅燈、綠燈、黃燈之間的切換操作,根據圖2給出的狀態轉換圖,可以得出如表2所示交通信號燈開關狀態的邏輯真值表。其中“1”表示信號燈亮,“0”表示信號燈滅。由此設計的譯碼電路如圖4所示。

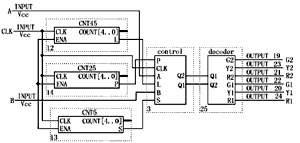

將上述各單元連接起來,就可以得到智能交通燈控制器設計的頂層圖,如圖5所示。所設計的頂層圖包括5個單元,其中CNT45、CNT25、CNT5是3個計數器,實現定時功能,Control 是主控電路所對應的模塊,decoder 是信號燈譯碼電路對應的模塊。圖5中的計數器模塊的計數輸出端這里沒有使用,當需要有定時顯示時,可以將其輸出控制時間顯示。

結 語

本文所給出的智能交通燈控制器的設計過程是采用自底而上(bottom-up)的設計方法,在初學EDA設計時,這是一種較為實用的設計方法,設計者可以很容易地從中小規模集成電路設計轉為超大規模集成電路設計。與自底而上設計方法相對的還有自頂而下(top-down)的設計方法,這種設計方法一般被用在開發FPGA芯片,設計較為復雜時序電路時使用。

在本文所給出設計過程中,采用了兩種設計輸入方法:即原理圖輸入和VHDL語言輸入。在對CPLD開發的過程中經常采用這種混合輸入方式,設計者可以根據需要對不同電路,采用比較適宜的設計輸入方式,來提高設計效率。