《低頻數字式相位測量儀》評析

王一舉

2003年全國大學生電子設計競賽試題中的C題,要求設計并制作一個低頻數字式相位測量儀。按照題目的要求和說明,低頻數字式相位測量儀實際需要設計和制作的是三個各自獨立的部分:(1)數字式相位測量儀;(2)數字式移相信號發生器;(3)移相網絡。其中移相網絡基本采用了題目推薦的電路,只是根據要求設計了與相移相關的關鍵的電阻電容的參數這里不做詳細的分析。

就湖北賽區而言,參賽學生設計了許多不同的實現方案,根據設計方案制作出很多成功的作品,選擇本題進行設計制作的有53隊,占湖北賽區23%,其中參與測試的作品有49件,而能通電測試的作品有43件,占參與測試的88%。而基本功能和擴展部分完成比較好的作品有20件,占本題參賽作品的28%,相對其它題目而言,從整體完成情況看是比較好的。本文主要對數字式相位測量儀和數字式移相信號發生器的設計思路和電路情況進行介紹,對采用的幾種方案進行簡潔的評析,由于只是參評過程中印象較深的部分內容,沒有相關作品原稿,難免出錯和疏漏,僅供參考。

1.數字式相位測量儀部分

數字式相位測量儀設計思路最基本的有兩個。

第一種思路是通過過零比較得到被測信號和參考信號之間的過零點的時間差τ之后,利用相位差φ與信號周期之間的關系:φ=(τ/T)×360o,就可以得到信號之間的相位差了。這種思路非常直接明了,過零比較一般采用集成運放如LM311構成同相放大器完成,也有把進入單片機前的電路功能統一用CPLD實現的作品。而測量τ的方式一般直接利用單片機的時鐘作為基準。也有部分作品為了提高測量的精度,外加高頻震蕩信號作為測量的時鐘基準。采用這種思路,能充分利用單片機的計算功能,但是,必須對信號的周期或頻率進行準確測量。典型的電路框圖如圖1所示。

第二種思路是將被測信號按題目的精度要求(<0.01o),用被測信號的N(3600以上)倍頻進行“刻度”(即把一個周期分為N等份),整形后使每一個計數值對應1/N o,這樣把測量相差轉換為τ期間的計數數值。“刻度”計數的方式主要有二:其一是利用鎖相環倍頻進行刻度,用8254等專用計數器計數后送單片機處理顯示;其二是把刻度計數等功能用CPLD實現,計數送單片機進行處理顯示。這種思路的最大問題是在被測信號頻率較高時,用于“刻度”的頻率太高,對器件的要求高,性價比會大大下降。典型的電路框圖如圖2所示。

2.數字式移相信號發生器

數字式移相信號發生器設計的方案有三類。

其一是采用函數發生器產生信號,湖北賽區有4例。采用這種思路,可以很快得到高精度頻率可調和幅度可調的信號,但是,要產生可以隨意調節相位差的兩路信號,就比較難以實現了,故此這種方案不可取。

其二是采用DSP技術,湖北賽區有1例。采用此種思路,其實也是直接數字波形合成(DDFS)技術的一種實現方式,應該可以實現題目的要求,此方案是可取的。

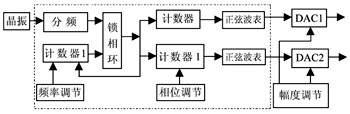

其三是采用DDFS技術實現數字移相信號發生器的方案,湖北賽區有31例,占測試作品的63%,真正實現的有16件作品,成功方案的實現方式一般都是采用單片機加FPGA或CPLD或E2PROM,從性能價格比上講,采用E2PROM更可取,但是,采用FPGA或CPLD更能體現技術先進性。采用DDFS技術實現數字移相信號發生器的典型的電路框圖如圖3所示。圖中虛線框內的部分可以采用FPGA或CPLD實現。

3.筆者對題目的理解

本題的低頻測相部分關鍵是對低頻的充分理解,若采用第一種思路來測相,電路設計方面比第二種思路復雜,要保證精度必須保證τ和T的測量都要正確;第二種思路把相位差轉化成了單一的脈沖個數的計數,不需要測量信號頻率或周期,電路的設計也簡潔,測量準確度也非常高,但是,若被測信號的頻率過高時要求用于“刻度”信號的頻率非常高,對器件的要求也很高。所以,在充分理解“低頻”的前提下,應該采用第二種方案,因為可以大大地提高準確度。

而移相信號發生器的難點關鍵在移相,要做到隨意移相,采用函數發生器或任何已有的信號產生器件都是難以實現的,采用DDFS幾乎是一種必然。測試的結果也充分證明了這一點。

最后,主要針對創新問題對參賽者談一點建議。一般參賽者把語音讀數或提示,遙控輸入或設置等作為自己的創新設計,當然,盡量采用新的技術或模塊,不能說不新,但是,不是創新,因為這些功能許多都不是設計者自己設計的,而是“拿來”的功能,創新應該是在作品的主要技術參數方面的突破。以本題為例,應該是在相位測量精度的提高、頻率范圍的擴大、不同波形信號相位差的測量、小信號的處理等方面進行電路設計思路的創新。