DTMB標(biāo)準(zhǔn)實(shí)時LDPC編碼器設(shè)計(jì)*

彭海云 ,徐建敏 ,王 鵬 ,劉 瑋

(1.周口師范學(xué)院 計(jì)算機(jī)科學(xué)系,河南 周口 466001;2.東莞理工學(xué)院 計(jì)算機(jī)學(xué)院,廣東 東莞 523808;3.同濟(jì)大學(xué) 通信軟件及專用集成電路設(shè)計(jì)中心,上海 200092)

1 引言

LDPC碼的概念最早由R.G.Gallager于1962年提出[1]。然而其研究成果長期為人們所忽視,直到1996年,Mackay等人重新“發(fā)現(xiàn)”了LDPC碼的強(qiáng)大性能[2],此后,LDPC碼開始成為信道糾錯編碼的一個主要研究熱點(diǎn)。LDPC碼具有極強(qiáng)的糾錯性能,如S.Y.Chung等人設(shè)計(jì)的1/2碼率,碼長107的非規(guī)則LDPC碼,在二進(jìn)制輸入AWGN信道下,當(dāng)錯誤概率為10-6時距Shannon限僅為0.004 55 dB[3],這是迄今為止性能最接近Shannon限的信道編碼。

2006年8月,我國的數(shù)字電視廣播地面?zhèn)鬏敇?biāo)準(zhǔn)DTMB正式公布[4]。該標(biāo)準(zhǔn)目前已經(jīng)正式實(shí)施,與歐美等國的ATSC,DVB-T等同類標(biāo)準(zhǔn)相比,其最大的亮點(diǎn)就是在前向糾錯編碼中引入了LDPC碼,使整個系統(tǒng)在相同頻譜利用率條件下的接收門限比ATSC,DVB-T等標(biāo)準(zhǔn)的接收門限更低,也更有利于固定和移動接收。

DTMB標(biāo)準(zhǔn)中的前向糾錯碼由BCH碼和LDPC碼級連而成,依不同應(yīng)用有0.4,0.6,0.8等3種碼率。其LDPC碼為準(zhǔn)循環(huán)(QC-LDPC)非規(guī)則碼,對應(yīng)校驗(yàn)矩陣和生成矩陣均具有分塊循環(huán)特性,每個子塊為全零陣或循環(huán)陣,以降低編譯碼復(fù)雜度,同時仍保持了LDPC碼的優(yōu)良糾錯性能[5]。

本文針對DTMB標(biāo)準(zhǔn)中LDPC碼的準(zhǔn)循環(huán)特點(diǎn),基于循環(huán)移位寄存器結(jié)構(gòu),實(shí)現(xiàn)了DTMB標(biāo)準(zhǔn)3種不同碼率的LDPC編碼,整個設(shè)計(jì)在FPGA芯片上經(jīng)過綜合和布局布線,最高時鐘達(dá)到了182.82 MHz,遠(yuǎn)超過DTMB實(shí)時編碼要求,而且該設(shè)計(jì)具有很強(qiáng)的通用性,只需更改編碼器內(nèi)部的生成矩陣子塊生成多項(xiàng)式記錄模塊,即可適用于任意QC-LDPC編碼。

2 DTMB標(biāo)準(zhǔn)LDPC碼

在DTMB標(biāo)準(zhǔn)中,輸入的比特碼流數(shù)據(jù)進(jìn)行擾碼處理后即送入前向糾錯模塊,其前向糾錯編碼(FEC)由外碼(BCH碼)和內(nèi)碼(LDPC)級聯(lián)實(shí)現(xiàn)。

LDPC碼生成矩陣Gqc的結(jié)構(gòu)如下

式中:I是 b×b 階單位矩陣;O 是 b×b 階零陣;Gi,j是 b×b循環(huán)矩陣,取 1≤i≤k,1≤j≤c。LDPC 編碼碼字輸出信息位在后,校驗(yàn)位在前。

DTMB標(biāo)準(zhǔn)中規(guī)定了3種FEC碼率,對應(yīng)LDPC碼率也有 3 種,分別是 LDPC(7 493,3 048)碼; LDPC(7 493,4 572)碼;以及 LDPC(7 493,6 096)碼;在將 LDPC 編碼碼字作為FEC輸出時,刪除前面5個校驗(yàn)位,因此事實(shí)上只輸出7 488 bit。

3 DTMB標(biāo)準(zhǔn)LDPC編碼器

如前所述,DTMB中采用的QC-LDPC碼為系統(tǒng)碼,校驗(yàn)比特在前,信息比特在后,3種碼率下的子塊大小均為127×127。如果在編碼時能充分利用生成矩陣的子塊循環(huán)特性,即使該生成矩陣并不具有稀疏性,也可以在較低的復(fù)雜度下完成LDPC編碼[6]。

3.1 QC-LDPC編碼算法

對QC-LDPC碼生成矩陣(如式(1)所示),由于子矩陣 Gi,j具有循環(huán)移位特性,只需記錄其第一行數(shù)據(jù) gi,j即可得到整個子矩陣 Gi,j, 故稱 gi,j為該子矩陣的生成多項(xiàng)式,因此整個生成矩陣 Gqc可以由(c×(t-c))個生成多項(xiàng)式 gi,j來 完 整描 述 。

記 a=(a1,a2,...,a(t-c)b)為待編碼信息比特,可將其依子塊大小分成(t-c)個子向量(a1,a2,...,at-c),其中 ai=(a(i-1)b+1,a(i-1)b+2,...,aib),1≤i≤(t-c),根據(jù)線性分組碼理論,信息比特a對應(yīng)的編碼碼字為

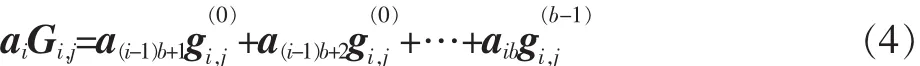

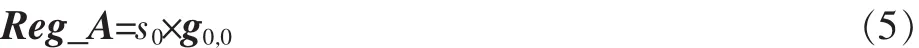

上式中,pj=(pj,1, pj,2,…,pj,b)為校驗(yàn)比特的第 j個子向量,1≤j≤c,由矩陣乘法知識可以得到

至此可以看出,隨著輸入信息比特(a1,a2,…,at-c)串行進(jìn)入編碼器,第j個校驗(yàn)比特子向量pj可以通過式(3)~(4)完成,當(dāng) ai進(jìn)入編碼器時,首先根據(jù)式(4)完成 aiGi,j運(yùn)算,該式可方便地采用線性反饋移位寄存器結(jié)構(gòu)實(shí)現(xiàn),然后再計(jì)算 Sj=a1G1,1+ a2G2,j+…+aiGi,j,而當(dāng) at-c全部進(jìn)入編碼器后,此時 Sj=a1G1,1+ a2G2,j+…+at-cGt-c,j,恰為第 j個校驗(yàn)比特子向量pj,因此如果編碼器中包含有c個pj并行計(jì)算模塊,即可在讀入所有信息比特后完成所有校驗(yàn)比特計(jì)算,而編碼器內(nèi)部只需存儲(c×(t-c))個生成多項(xiàng)式 gi,j信息。

3.2 設(shè)計(jì)要求

編碼器設(shè)計(jì)需要能夠完成DTMB標(biāo)準(zhǔn)中所有3種LDPC碼的實(shí)時編碼。3種LDPC碼的信息比特長度分別為3 048 bit、4 572 bit和 6 096 bit, 碼字長度均為 7 493 bit,但前面5個校驗(yàn)位不必輸出,只需輸出后面的7 488 bit即可。

采用前述QC-LDPC編碼算法,在所有信息比特輸入完畢的同時計(jì)算出所有校驗(yàn)比特,然后再將刪除前面5位的校驗(yàn)比特和信息比特組成完整碼字以串行形式輸出,這需要耗費(fèi)7 488個時鐘周期,而輸入信息比特最大長度為6 096 bit。為提高系統(tǒng)工作穩(wěn)定性,采用單時鐘設(shè)計(jì),輸入、輸出均為1位串行模式,且各自有單獨(dú)的Data_Valid信號配合。首先確定編碼器時鐘頻率,按照DTMB標(biāo)準(zhǔn)規(guī)定,系統(tǒng)最高凈載荷率為32.486Mbit/s(對應(yīng)0.8碼率FEC模式),此時LDPC碼信息比特和碼字比特速率分別為32.486×762/752 Mbit/s=32.918 Mbit/s和 32.486×7488/6 016 Mbit/s=40.435 Mbit/s,為留有部分余量,選擇45 MHz為編碼器工作時鐘。

3.3 LDPC編碼器設(shè)計(jì)

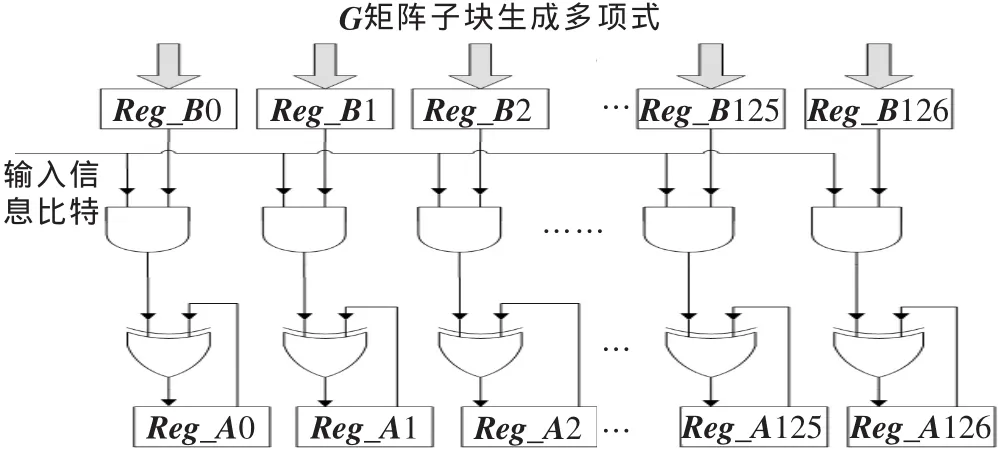

編碼器的核心是移位寄存器-加法器-累加器結(jié)構(gòu)(SRAA),它可以完成式(3)~(4)所示的校驗(yàn)比特計(jì)算,其具體結(jié)構(gòu)如圖1所示。

圖1 SRAA結(jié)構(gòu)圖

可以看出,該SRAA由2組寄存器陣列組成,上方為寄存器B陣列Reg_B,下方為寄存器A陣列Reg_A,其寬度均為子塊大小127。初始狀態(tài)時,寄存器陣列A,B內(nèi)容全部清零,開始編碼時,首先將生成矩陣G子塊G0,0的生成多項(xiàng)式g0,0加載到寄存器B陣列中,此時第1個信息比特s0出現(xiàn)在輸入端,s0與Reg_B經(jīng)與門陣列相與后出現(xiàn)在異或門陣列輸入端,在GF(2)域中,加法與異或運(yùn)算是等效的,因Reg_A初始內(nèi)容為零,可知更新后的Reg_A值為

在下一個時鐘周期,第2個信息比特s1出現(xiàn)在輸入端,Reg_B內(nèi)容循環(huán)右移1位,變?yōu)椋瑯咏?jīng)與門和異或門陣列后,此時Reg_A變?yōu)?/p>

以此類推,在第127個時鐘周期時,Reg_A為

式中:s0為信息比特按子塊長度127分割而成的第1組子陣列(s1,s2含義同上,記 s=(s0,s1,s2,…,st-c))。 此后,Reg_B開始加載子塊 G1,0的生成多項(xiàng)式 g1,0,再重復(fù)上述操作,經(jīng)127個時鐘周期后,Reg_A為

這樣,當(dāng)所有信息比特均輸入完畢后,寄存器陣列A中的值為

因此,一個SRAA結(jié)構(gòu)可以在信息比特長度 (t-c)×127個時鐘周期內(nèi)完成1個校驗(yàn)比特子塊計(jì)算(含127個校驗(yàn)比特),采用c組SRAA結(jié)構(gòu)并行工作,可以在所有信息比特輸入完畢后同時得到所有校驗(yàn)比特(計(jì)算結(jié)果存儲于Reg_A陣列中),去除前面5個校驗(yàn)比特,并將余下的校驗(yàn)比特和原始信息比特組成完整的7 488 bit以串行模式輸出,即完成了整個LDPC編碼過程。

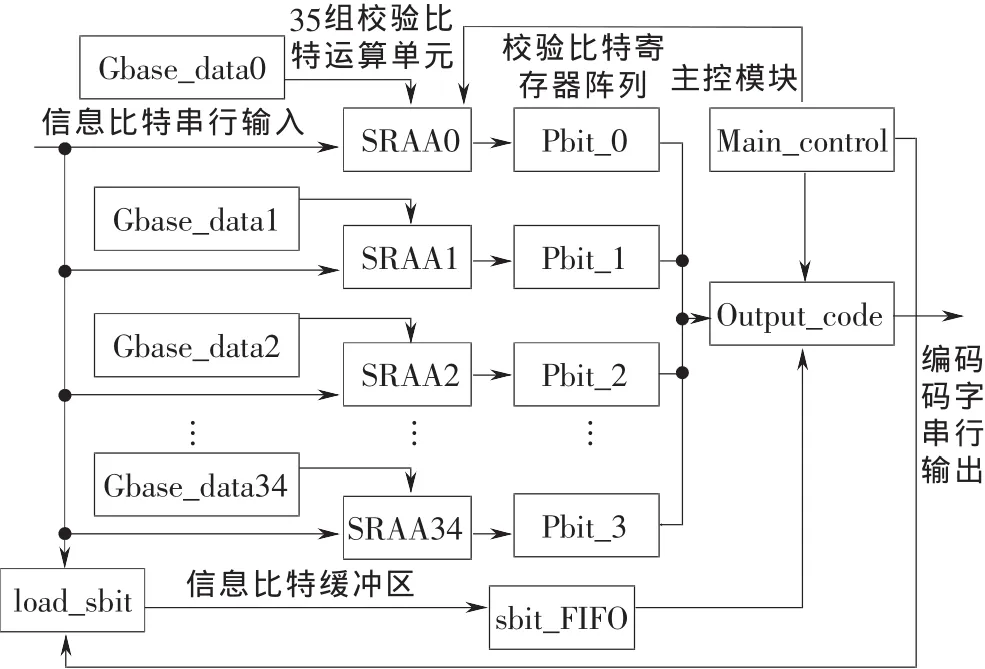

圖2給出了DTMB標(biāo)準(zhǔn)LDPC編碼器頂層模塊結(jié)構(gòu)圖。編碼器采用3級流水線設(shè)計(jì):第1級流水線完成輸入信息比特乒乓緩存(由LDPC信息比特最大傳輸速率和編碼器工作時鐘可知完成一幀信息比特傳輸最多耗費(fèi)8 333個時鐘周期),第2級完成校驗(yàn)比特計(jì)算(最多耗時6 096個時鐘周期),第3級完成編碼碼字輸出(耗時7 488個時鐘周期)。

編碼器硬件實(shí)現(xiàn)采用Altera公司的Stratix II系列EP2S15芯片,以下詳細(xì)介紹各子模塊設(shè)計(jì):

1)load_sbit模塊

load_sbit模塊主要完成信息比特讀入,將讀入的信息比特存入內(nèi)部乒乓緩沖區(qū),同時還要記錄相應(yīng)的碼率信息code_rate,該乒乓緩沖區(qū)可由一塊位寬為1 bit,深度為16 384 bit的RAM構(gòu)成,其地址最高位作為乒乓緩沖區(qū)切換位。當(dāng)一幀LDPC碼字傳輸完畢后,置相應(yīng)buf_available信號為高,代表當(dāng)前乒乓緩沖區(qū)可用,此后SRAA模塊可以接收load_sbit模塊內(nèi)部乒乓緩沖區(qū)輸出的信息比特,同時下一幀信息比特?cái)?shù)據(jù)也在繼續(xù)寫入乒乓緩沖區(qū),這樣可以使load_sbit模塊始終處于工作狀態(tài),減少了系統(tǒng)延時。

圖2 DTMB標(biāo)準(zhǔn)LDPC編碼器結(jié)構(gòu)框圖

2)sbit_FIFO模塊

sbit_FIFO主要用作緩存發(fā)送至SRAA模塊的信息比特,當(dāng)校驗(yàn)比特計(jì)算完畢時,由碼字輸出模塊output_code讀取FIFO中的信息比特?cái)?shù)據(jù),并與校驗(yàn)比特組成完整的LDPC碼字,該模塊可由Altera公司的IP核專用生成工具M(jìn)egaWizard實(shí)現(xiàn),F(xiàn)IFO數(shù)據(jù)寬度為1 bit,最大深度為16 384 bit。

3)SRAA模塊陣列

SRAA陣列是編碼器的核心,也是占用資源最多的模塊,其中單個SRAA模塊內(nèi)部結(jié)構(gòu)如前所述。在DTMB標(biāo)準(zhǔn)3種LDPC碼率中,對應(yīng)的校驗(yàn)比特子塊長度分別為35(0.4碼率 FEC 模式)、23(0.6碼率 FEC 模式)和 11(0.8碼率FEC模式)。相應(yīng)地,3種碼率下所需的SRAA個數(shù)也恰為35,23,11。在實(shí)際工作中,這些SRAA陣列的工作時序完全相同,因此設(shè)計(jì)中采用了一個主SRAA模塊SRAA0_prior,該模塊不僅完成3種碼率下的校驗(yàn)比特子塊計(jì)算功能,同時還產(chǎn)生SRAA模塊時序共用信號,供其余從SRAA模塊使用。從SRAA依工作模塊不同也可分成3類,一類可支持所有3種碼率(SRAA0)、一類可支持0.4和0.6碼率模式(SRAA1),還有一類僅支持0.4碼率模式(SRAA2)。SRAA具體排列如圖3所示。

當(dāng)所有SRAA模塊均被使能,且SRAA0_prior,SRAA0,SRAA1設(shè)置為0.4碼率工作模式,編碼器可完成LDPC(3 048,7 492)編碼;當(dāng) SRAA0_prior,SRAA0,SRAA1使能,SRAA2 禁用, 且 SRAA0_prior,SRAA0,SRAA1 設(shè)置為0.6碼率工作模式,編碼器可完成LDPC(4 572,7 492)編碼;當(dāng) SRAA0_prior,SRAA0 使能,SRAA1,SRAA2 禁用,且SRAA0_prior,SRAA0設(shè)置為0.8碼率工作模式,編碼器可完成 LDPC(6 096,7 492)編碼。

圖3 SRAA并行計(jì)算陣列

在35組SRAA模塊中,SRAA0_prior處于核心地位,信息比特輸入、生成矩陣子塊生成多項(xiàng)式讀取、校驗(yàn)子塊計(jì)算、SRAA狀態(tài)更新及輸出等功能均由該模塊完成。其余從SRAA模塊只需配合SRAA0_prior輸出時序信號進(jìn)行校驗(yàn)比特計(jì)算即可。

4)gbase_data模塊

gbase_data模塊用于存儲LDPC碼生成矩陣子塊生成多項(xiàng)式,每個生成多項(xiàng)式位寬為127 bit。3種碼率下的數(shù)據(jù)均需存儲,0.4 FEC碼率下對應(yīng)24×35=840個G矩陣生成多項(xiàng)式;0.6 FEC碼率下對應(yīng)36×23=828個G矩陣生成多項(xiàng)式;0.8 FEC碼率下對應(yīng)48×11=528個G矩陣生成多項(xiàng)式。

gbase_data模塊與SRAA模塊一一對應(yīng),因此共需要35組gbase_data模塊,其中前面11組需要存儲所有3種碼率下的G矩陣子塊列生成多項(xiàng)式,深度為24+36+48=108;中間12組深度為24+36=60;最后12組深度為24。均由ROM構(gòu)建,依外部碼率信號不同,Gbase_data模塊可自動輸出對應(yīng)碼率下的生成多項(xiàng)式數(shù)據(jù)。

5)output_code模塊

校驗(yàn)比特計(jì)算完畢后,由output_code模塊完成碼字輸出,首先輸出校驗(yàn)比特?cái)?shù)據(jù)(去除前面5個校驗(yàn)位),待校驗(yàn)比特串行輸出完畢后,再讀取sbit_FIFO中的信息比特?cái)?shù)據(jù),也以串行模式輸出,二者配合構(gòu)成完整的7 488 bit FEC碼字,為減少輸出數(shù)據(jù)毛刺現(xiàn)象,在輸出編碼數(shù)據(jù)時增加了一級寄存器。

6)main_control模塊

main_control模塊主要控制各模塊的使能、禁用、FIFO數(shù)據(jù)清零,以及根據(jù)碼率不同確定SRAA工作模式。

4 譯碼器FPGA實(shí)現(xiàn)及驗(yàn)證

采用RTL級Verilog HDL代碼編寫整個設(shè)計(jì),實(shí)現(xiàn)平臺為EP2S15,在Quartus II 7.2下成功完成了綜合及布局布線,布線后最高工作頻率可達(dá)182.82 MHz,已遠(yuǎn)超過DTMB標(biāo)準(zhǔn)的時鐘要求。該編碼器布線后具體資源占用情況如表1所示,與現(xiàn)有同類設(shè)計(jì)相比,節(jié)省了近20%的硬件資源[7]。

表1 譯碼器占用資源統(tǒng)計(jì)

5 結(jié)論

DTMB標(biāo)準(zhǔn)中采用的是QC-LDPC碼,對應(yīng)生成矩陣具有準(zhǔn)循環(huán)移位特性,因此可直接采用生成矩陣完成LDPC編碼,編碼器中只需存儲3種碼率下的LDPC碼生成矩陣子塊生成多項(xiàng)式即可,整個編碼器基于SRAA陣列結(jié)構(gòu),通過線性反饋移位寄存器來完成LDPC編碼,共占用4 699個ALUT,存儲資源占用為350 Kbit。該編碼器可以在45 MHz的工作時鐘下完成DTMB標(biāo)準(zhǔn)下的實(shí)時LDPC編碼,且支持所有3種LDPC碼率。

[1]GALLAGER R G.Low-density Parity-check Codes[J].IRE Trans.Inf.Theory, 1962,8(1):21-28.

[2]MACKAY D J C,NEAL R M.Near Shannon limit performance of low-density parity check codes[J].Electron.Lett., 1996,32(15):1645-1647.

[3]CHUNG S Y, FORNEY G D,RICHARDSON T J,URBANKE R.On the design of low-density parity check codes within 0.0045dB of the Shannon limit[J].IEEE Comm.Letters , 2001,15(2):58-60.

[4]楊知行.地面數(shù)字電視國家標(biāo)準(zhǔn)DTMB技術(shù)解讀[EB/OL].[2009-06-20].http://www.availink.com.cn/UserFiles/u12850461886 29250001668832814.pdf.

[5]ANDREWSK,DOLINARS,THORPEJ.Encoders for block-circulant LDPC codes[C]//International Symposium Proceedings on Information Theory.Adelaide , Australia:[s.n.].2005, 4(9):2300-2304.

[6]LI Zongwang, CHEN Lei, ZENG Lingqi, et al.Efficient encoding of quasi-cyclic Low-Density Parity-Check Codes[J].IEEE Trans.Comm., 2006,54(1):71-75.

[7]楊抒文,彭克武,潘長勇.DTMB發(fā)射機(jī)LDPC編碼器的設(shè)計(jì)與優(yōu)化[J].電視技術(shù),2008,32(7):4-5.