數字信道中誤碼發生器的設計與實現

何源潔,李宏利

(中國電子科技集團公司第五十四研究所,河北石家莊050081)

0 引言

隨著通信事業的發展,通信系統的測試正在變得越來越重要。為了如實測試通信系統的數字信道性能,常常需要加入一定的具有特定統計特性的隨機誤碼。而信號隨機誤碼插入一般是具有高斯分布特性誤碼的插入,是數字信道測試設計中的難點。

將線性同余法和Box-Muller變換應用在數字信道測試中使用的高斯誤碼發生器設計中,采用現場可編程門陣列(FPGA)全數字硬件架構,具有精度高、硬件實現容易、節約硬件邏輯資源和誤碼率可控的優點,可廣泛應用于高速無線和有線通信測試中。

1 算法與方案

1.1 誤碼發生器的實現結構

隨機誤碼發生器所要求的技術指標為:插入具有高斯白噪聲條件下的誤比特特性,誤比特率為0或1×10-2~1×10-7可調,每量級上步進均為1.0。對于數字信道中誤碼的插入,實質上是要解決誤碼分布的產生及誤碼數量的控制問題。隨機誤碼發生器的過程如圖1所示。

圖1 隨機誤碼發生器原理

誤碼發生器的工作原理如下:首先,根據誤碼分布特性,隨機數發生器產生與隨機誤碼分布特性相一致的隨機數序列,同時借鑒真實數字信道中誤碼數量與判決電平選取相關,誤碼數量的控制是通過設置與誤比特率和誤碼分布相關的閾值TH來實現。接著,比較器將閾值TH和隨機數發生器產生的隨機數R相比較,若R≥TH則輸出誤碼標記1,否則輸出0,這樣就產生了0和1誤碼圖譜數據流。顯然誤碼圖譜數據流中的誤碼標記1的分布與誤碼分布一致,且其個數與誤碼數量一致。將具有誤碼分布特性和數量特性誤碼圖譜數據流與輸入的無誤碼的數據作模二加運算,即完成隨機誤碼的插入。

技術指標要求所設計的隨機誤碼發生器能夠模擬高斯白噪聲信道下的誤碼特性,因此,隨機數發生器產生的隨機數必須服從高斯分布。得到高斯分布隨機數的關鍵是:首先得到均勻分布的隨機數,然后通過變換得到高斯分布的隨機數。

1.2 均勻分布隨機數的產生

均勻分布隨機數是產生其它分布隨機數的基礎,如高斯分布和指數分布等,因此產生均勻分布隨機數的好壞直接影響到所產生的高斯隨機數的性能。所以均勻隨機數的產生至關重要。

常用的均勻隨機數的產生方法主要有線性同余法、反饋位移寄存法和組合同余法。其中線性同余法實現簡單、占用存儲單元少,是目前應用最廣泛的方法之一。

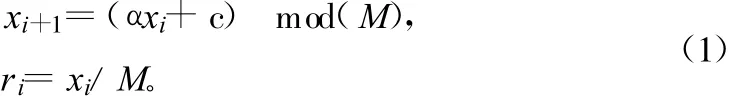

線性同余法是由萊默(Lehmer)于1951年提出來的,此方法是利用數論中的同余運算來產生隨機數,故稱為同余發生器。其遞推公式為:

式中,α為乘子(常數);c為增量(常數);x0為種子;M為模;α,x0和 M都是正整數;i為迭代次數;ri為(0,1)區間均勻分布的隨機數。

1.3 高斯分布隨機數的產生

由隨機信號理論可知,在(0,1)區間上服從均勻分布的隨機數經過一定的變換,可產生服從N(0,1)的高斯隨機數。該變換就是Box-Muller變換法。Box-Muller變換法產生高斯隨機數的計算式為:

式中,r1和r2為互相獨立的(0,1)區間均勻分布隨機數。

用式(2)產生高斯分布隨機數的精度高,可以同時產生一對互為正交的獨立高斯隨機數,應用較為廣泛。實現時可分別建立正余弦表和自然對數平方根表,將前面生成的均勻分布的隨機數作為地址就可以通過查表來實現Box-Muller變換。

2 硬件實現

2.1 硬件組成

數字信道中高斯隨機誤碼產生器的實現框圖如圖2所示,其中監控計算機作為主控制器和誤碼門限值的計算。監控計算機與FPGA之間通過串口進行門限的設置。FPGA作為信號實時處理器,實現信號的輸入/輸出以及隨機誤碼的實時插入。

圖2 高斯隨機誤碼發生器實現

該設計中采用Altera公司Cyclone系列FPGAEP1C12芯片來完成誤碼發生器的工程實現。Cyclone系列是Altera公司于2003年推出的具有高性價比的FPGA系列產品,EP1C12芯片可用的資源包括:12 060個邏輯單元、234 kbit的RAM和2個鎖相環。該系列芯片使用靈活、功能豐富、成本低、便于開發。這種方案的優點是:采用計算機作為主控制器可以實現多種人機交互接口;采用FPGA作為實時信號處理器可以利用其強大的實時信號處理能力完成高速的數據流的誤碼實時插入,且FPGA具有多次可編程的優點使得系統的擴展和升級變得非常容易。此外利用串口配置閾值或將閥值存儲到FPGA的存儲器中,使得閾值的處理非常方便;同時利用FPGA產生隨機數,不需要額外的存儲空間節約了成本,降低了設計難度。

2.2 處理流程和難點

高斯隨機誤碼插入的流程是外部輸入沒有誤碼的數據和時鐘,用輸入時鐘推動均勻隨機數發生器按式(1)描述的算法用VHDL語言實現,輸出2組不同的(0,1)區間均勻分布的16 bit位寬的無符號隨機數。然后使用查表法實現Box-Muller變換,得到高斯分布的隨機數。由于誤比特率為0或1×10-2~1×10-7可調,所以對高斯分布的隨機數進行了32 bit位寬的量化。

2.3 閥值的計算

根據設置的誤比特率Pe和誤碼分布的概率密度函數(即高斯分布),可以通過式(3)求出閾值TH。

根據要求利用MATLAB可以比較容易得到誤碼率和門限閥值之間的關系,如表1所示。

表1 誤碼率與閥值關系表

2.4 硬件仿真

用VHDL語言實現的高斯隨機數發生器之后,再用ModelSim軟件對其進行硬件仿真,其仿真結果如圖3所示。

圖3 高斯隨機數發生器的ModelSim仿真結果

通過對該仿真輸出的數據進行高斯分布隨機數的直方圖和概率校驗圖的分析,并與MATLAB軟件仿真的結果進行了比較,結果表明該VHDL語言實現的高斯隨機數發生器完全滿足要求。

3 測試結果

根據圖2的實現框圖,將誤碼儀的輸出數據接到無誤碼數據流端,再將經過隨機誤碼發生器插入誤比特后有誤碼數據流輸出到誤碼儀,用監控計算機的軟件控制插入誤碼率的門限,隨機誤碼發生器輸出端就得到相應的插入誤碼后的數據流。

所研制的隨機誤碼產生器利用FIREBERD 6000A誤碼儀進行了測試,測試結果如表2所示。測試結果表明設計的隨機誤碼產生器具有較高的準確性,能夠滿足數字信道中誤碼測試的要求。

表2 測試結果對比表

4 結束語

通過對一種高斯隨機誤碼發生器實現方法的介紹,并對其實現的技術難點進行了詳細描述。技術難點有3點:①均勻分布隨機數的產生;②自然對數平方根表的生成;③誤碼率閥值門限的計算。

與已有的誤碼產生方法相比,該方法具有以下優點:誤碼分布具有足夠的隨機性,即所產生的誤碼分布符合高斯隨機分布的統計特性;該方法實現電路簡單,并采用較小容量的FPGA和相應的接口芯片就實現了高斯誤碼圖案插入。

[1]DANGER J L,GHAZEL A,BOUTILLON E,et al.Efficient FPGA Implementation ofGaussian NoiseGeneratorfor Communication ChannelEmulation[J].The7th IEEE International Conference on Electronics,Circuits and Systems,2000(1):366-369.

[2]張胡平,姚遠程,馮 立.高斯分布誤碼插入的設計和實現[J].無線通信,2008(1):4-6.

[3]劉 江,汪 濤,劉洛琨.基于FPGA實時可配置的高斯白噪聲發生器[J].現代電子技術,2005(6):13-15.