高速脈沖信號源的設計與實現

史赟 任勇峰 焦新泉 王 強

(中北大學電子測試技術國家重點實驗室,山西 太原 030051)

0 引言

脈沖信號包含了豐富的高頻和低頻成分。在數據采集系統中,通常需要脈沖信號源提供的信號來檢測數據采集設備的工作狀況。此外,脈沖信號源產生的信號還可以作為控制信號,用于實現對采集設備的控制。因此,要實現靈活控制脈沖信號的脈寬、占空比、幅度和偏移量等,脈沖信號源要具備及時、穩定和可靠的特性[1]。本文針對某遙測系統所要求的脈沖信號,根據脈沖信號的脈寬和幅度設計出了兩種方案:一種是將FPGA產生的脈沖信號經過高速運放調理產生;另一種是通過FPGA控制電子開關的導通和關斷來形成相應的脈沖信號。

1 信號源的方案設計

1.1 功能介紹

本高速脈沖信號源的主要功能是為數據采集設備提供被測信號源。高速脈沖信號源能夠模擬產生兩路脈寬為100 ns、幅度為-1.0~+1.0 V的視頻信號。

1.2 基本原理

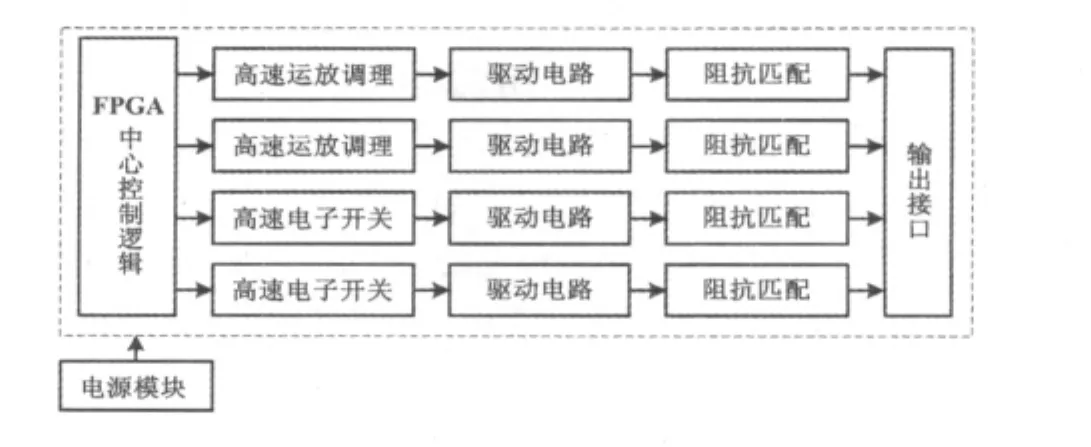

高速脈沖信號源分別采用基于高速運放調理和基于高速電子開關兩種方案實現。信號源由中心控制邏輯、高速運放調理電路、高速電子開關電路、驅動電路、阻抗匹配、電源模塊和輸出接口等部分組成。其原理框圖如圖1所示。

圖1 原理框圖Fig.1 Block diagram of the principle

中心控制邏輯FPGA負責控制高速信號的產生。此高速脈沖信號源采用VHDL硬件描述語言進行設計,靈活可靠。高速運放調理電路將FPGA產生的高速信號處理成符合要求的形式輸送到接口,高速脈沖信號也可以通過FPGA控制高速電子開關的導通和關斷。驅動電路是為了增強整個信號源的驅動能力。阻抗匹配的作用是消除信號源在長線傳輸中的反射現象。電源模塊為脈沖信號源的各部分供電,各部分所需供電電平不兼容,因此,電源模塊中要進行電平轉換。進行電平轉換時要注意供電芯片和被供電電路的功耗匹配,保證輸出正確的供電電壓,使各部分能夠正常通信。

2 硬件電路實現

2.1 高速運放調理電路

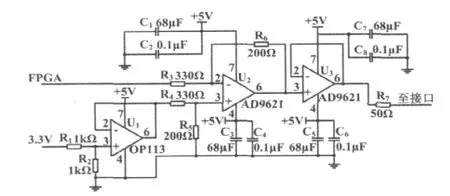

由可編程邏輯器件FPGA產生的脈沖信號,脈寬滿足要求,但幅值不滿足要求。因此,基于高速運放調理方案,采用差動放大電路,通過外部提供偏置電壓,對信號進行幅值調理,產生所要求的高速脈沖信號。高速運放調理電路原理圖如圖2所示。

圖2 高速運放調理電路原理圖Fig.2 Principle of the high-speed operational amplifier conditioning circuit

在高速運放調理電路設計中,主要考慮高速運放的選擇、信號幅值的調理和驅動電路的設計。

2.1.1 高速運放的選擇

從FPGA輸出的原始信號經過差動放大電路進行調理。由于信號是高速信號,所以應該選擇高速運放與之匹配。壓擺率是高速運放的重要指標,也稱作運放的轉換速率(slew rate,SR),它反映的是一個運算放大器在速度方面的指標,表示運放對信號變化速度的適應能力,對于高速運放來說是至關重要的。運放的壓擺率相對于信號過低時,信號不能及時地被調理;過高時,輸出的信號會產生振蕩(低頻信號通過高速運放時會產生振蕩)[2]。信號幅值越大、頻率越高,要求運放的SR也越大。

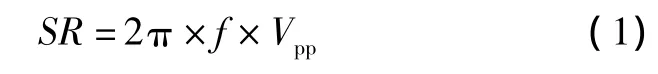

SR與頻率f、幅度VPP之間的關系為:

本例中高速脈沖信號的脈寬為100 ns,按照極限頻率為10 MHz考慮(占空比為1∶1時),高速脈沖信號的諧波分量豐富,調理時要考慮脈沖信號的5次諧波分量,有效頻率f高達50 MHz,幅度 Vpp=1.0 V,經計算得運放的轉換速率為SR=314 V/μs。選擇運放時要按至少兩倍的冗余考慮,一般取兩倍以上,即壓擺率要大于 628 V/μs。

放大器選用AD9621,它是一種基于電壓反饋的高速運放,失真低,噪聲低,小信號模型工作頻率為350 MHz,大信號工作頻率為130 MHz,壓擺率為1200 V/μs。高速運放AD9621壓擺率滿足要求,可以保證高速脈沖信號的不失真輸出。AD9621需要+5 V雙端供電,電路設計中需要在供電電源和地之間就近加退耦電容,以濾除噪聲,保證高速運放工作在穩定狀態。

2.1.2 信號幅值的調理

脈沖信號的幅值通過差動放大電路可以調理到合適的范圍內。設差動放大器反向端和同向端的輸入電壓分別為 Ui1和 Ui2,其中 Ui1為0~3.3 V,通過對 FPGA編程實現,使FPGA某個I/O口輸出脈寬為100 ns,幅度為0~3.3 V的脈沖信號。Ui2是由放大器OP113組成的放大電路為后級差動放大電路提供的偏置電壓。OP113是一種低噪聲、低溫漂的放大器。電路中,由于R1=R2,因此可以將3.3 V的輸入電壓調整到1.65 V,作為OP113的同相輸入端電壓,放大倍數為1,則輸出為1.65 V,輸入到差動放大電路的同相輸入端。

在差動放大電路中,差動電路要求輸入電路的兩端對稱,即從運放反相端到地之間向外看的等效電阻等于同相端到地之間向外看的等效電阻。因此,要注意電阻匹配。差動放大電路的高度對稱,共模抑制比高,能有效地抑制零點漂移,抗干擾性能好[3]。利用虛短和虛斷的概念分析電路,得到輸出端電壓為:

當R3=R4、R5=R6時,滿足電阻匹配的要求,同時可以消除由輸入的共模部分和運放偏置電流引起的誤差,使輸出電壓只與輸入的差模部分有關。由圖2可知,R3=R4=330 Ω,R5=R6=200 Ω,Ui1取 0 ~3.3 V,Ui2=1.65 V,將以上變量代入式(2)中,可得 Uo= -1.0 ~1.0 V。

2.1.3 驅動電路的設計

差動放大電路輸出的高速脈沖信號再經過電壓跟隨器組成的驅動電路輸出。采用電壓跟隨器可以使高速脈沖信號完全進入采集設備,避免對信號處理時由于輸入信號的輸出阻抗過高而導致的損耗[4]。根據輸入的高速脈沖信號的特點,本設計中選用AD9621作為電壓跟隨器。在+5 V雙電源供電的情況下,該運放的特性完全滿足信號的頻率和幅度等方面的要求。

2.2 高速電子開關電路

高速脈沖信號源也可以采用高速電子開關實現,即通過FPGA產生的控制信號控制高速電子開關相應引腳的導通和關斷來產生高速脈沖信號,其硬件原理圖如圖3所示。

圖3 高速電子開關電路原理圖Fig.3 Principle of the high-speed electronic switch circuit

高速電子開關電路設計主要考慮的是決定輸出高速脈沖信號上升沿和下降沿時間的高速電子開關的導通和關斷時間[5]。本方案中采用單刀雙擲三通道電子開關 ADG733,其導通電阻為2.5 Ω,導通時間為21 ns,關斷時間為10 ns,滿足要求,并選用高速運放AD818將幅值為+5 V和-5 V的直流信號調理到+1 V和-1 V,作為高速電子開關的輸入端。高速運算放大器AD818具備很強的驅動能力且噪聲和功耗低。

高速電子開關ADG733可以支持單端和雙端兩種供電方式,這里使用雙端供電方式,導通電阻為2.5 Ω。ADG733有3個地址輸入端,不同的地址控制著不同通道的開關切換。本文中由于要模擬輸出兩路視頻信號,因此使用ADG733的1通道和2通道作為切換通道,將地址輸入端的高位接地,另兩位接到FPGA的I/O口。通過邏輯控制地址輸入端的值,就可以實現兩個通道的開關切換。由于輸出的高速脈沖信號的脈寬為100 ns,因此,可以通過時序控制開關的切換速度來實現,即通過控制FPGA與高速電子開關地址端相連的I/O口輸出“0”和“1”的持續時間和間隔時間來控制高速電子開關切換到±1 V來實現。高速電子開關由-1 V導通到+1 V導通時,產生信號上升沿;由+1 V導通到-1 V導通時,產生信號下降沿。使用電子開關時,應注意導通電阻和漏電電流要小,其開關速度越快越好,且需符合能夠產生脈寬為100 ns脈沖信號的要求。為了提高信號源的驅動能力,高速電子開關后面使用高速運算放大器做輸出跟隨,其原理與第一種方案相同。

2.3 消除反射

高速脈沖信號接口選用無線電天線接口(subminiature-A,SMA)連接器與同軸電纜相連,傳輸到采集設備。在實際測量中,接口處未接同軸電纜時,接口處測得的信號波形完整,沒有出現較大的衰減和畸變,引起的誤差在合理的范圍之內。當接口處接同軸電纜時,測量同軸電纜的源端和負載端,信號均存在振鈴和過沖現象,信號發生了反射。具體來說,電壓跟隨器起到了較好的信號隔離作用,由于其輸出阻抗低,提高了帶負載能力[6-8]。但同時它又會導致高速信號輸出端的阻抗與同軸電纜的特性阻抗不匹配,引起高速脈沖信號在傳輸過程中的反射現象。

信號在源端反射的大小取決于源端阻抗ZS和傳輸線特性阻抗的Z0的差值,同理,信號在負載端反射的大小取決于負載端端阻抗ZL和傳輸線特性阻抗的Z0的差值。源端反射系數,負載端反射系數。反射系數在+1和-1之間。當R1、R2為正時,反射信號與原信號方向相同;為負時,反射信號與原信號反向;R1、R2為+1時,信號被100%反射回來;R1、R2為0時,傳輸線的特性阻抗被精確匹配。

本脈沖信號源采用在驅動電路輸出端串聯一個電阻的方法來消除反射,電阻要盡量靠近驅動電路的輸出端,使其與驅動電路的輸出阻抗之和等于傳輸線的特性阻抗。本例中跟隨放大器的輸出阻抗較小,相對于同軸電纜50 Ω的特性阻抗來說,可以忽略,因此,在驅動電路和傳輸線之間串聯一個50 Ω的電阻與同軸電纜的特性阻抗相匹配。采用串聯端接阻抗區配方法的優點是簡單,只需要一個元件,而且不需要較大的驅動電流[10]。高速脈沖信號輸出端與同軸電纜阻抗匹配后,再次測量到的高速信號波形得到了較大的改善,信號的反射基本消除。

3 結束語

高速脈沖信號源已廣泛應用于數據采集系統中,數據采集設備對其可靠性和穩定性的要求也越來越高。本文提出的兩種高速脈沖信號源的設計方案,均能夠輸出穩定可靠的脈沖信號,同時利用可編程邏輯器件FPGA實現對信號輸出的控制,靈活穩定。通過采用串聯端接阻抗匹配的方法,消除了高速脈沖信號在傳輸過程中的反射現象。本高速脈沖信號源已成功應用于某采集設備的調試。

[1]徐文強,任勇峰,文豐.基于FPGA的高速脈沖信號源的設計與實現[J].微計算機信息,2007,23(2):251 -252,229.

[2]薛瑤.某飛行器數據記錄器的優化設計[D].太原:中北大學,2009.

[3]王遠.模擬電子技術[M].北京:機械工業出版社,2000.

[4]吳蓬勃.視頻傳輸中的阻抗匹配研究[J].航空電子技術,2009,40(2):43-47.

[5]趙呈愷.通用測試臺模擬信號源的設計[D].太原:中北大學,2009.

[6]任勇峰,莊新敏.VHDL與硬件實現速成[M].北京:國防工業出版社,2005.

[7]朱明杰,卓君華.傳輸線的反射干擾[J].電子測試,2009(6):70-73.

[8]黃乘順,李星亮.傳輸線阻抗匹配的分析與設計[J].科學技術與工程,2007,7(4):609 -611.

[9]Johnson H M.高速數字設計[M].沈立,朱來文,陳宏偉,等,譯.北京:電子工業出版社,2004.

[10]焦新泉,秦麗.信號傳輸過程中的反射及其抑制方法[J].測試技術學報,2004,18(z2):93 -96.