FPGA中浮點運算功能的實現技術

茅 飛 劉樹青 朱興華 朱昊

1.南京康尼電子科技有限公司,江蘇 南京 210013

2.南京工程學院先進數控技術江蘇省高校重點建設實驗室,江蘇 南京 211167

3.常州大學機械工程學院,江蘇 常州 213016

FPGA中浮點運算功能的實現技術

茅 飛1劉樹青2朱興華3朱昊2

1.南京康尼電子科技有限公司,江蘇 南京 210013

2.南京工程學院先進數控技術江蘇省高校重點建設實驗室,江蘇 南京 211167

3.常州大學機械工程學院,江蘇 常州 213016

浮點運算在眾多領域廣泛應用,通過采用純硬件電路方法實現并形成模塊化,可以增強可移植性、提高浮點運算速度和精度、縮短研發周期和降低開發成本。詳細介紹了FPGA中浮點運算功能的實現算法和實現技術,實現了32位浮點數的加減乘除功能運算單元設計,通過QuartusII自帶的仿真軟件獲得仿真波形,驗證了正確性。

浮點運算;現場可編程門陣列;模塊化

隨著半導體技術的快速發展和生產工藝水平的不斷提高,FPGA芯片在性能和密度方面得到了提高,已具有性能高、密度高、電壓低、功耗低、可靠性高等特點,可滿足純硬件實現浮點運算的需要。本文介紹了FPGA中浮點運算功能的實現算法和實現技術。

1.浮點數的描述

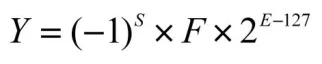

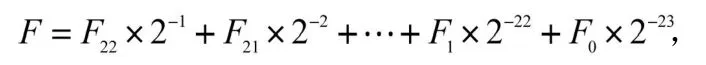

E為階碼位,共8位,E∈[1,254],當E=0或E=255時Y為非數(NAN,Not A Number)或非規格化數。32位浮點數(單精度)組成結構如表1。

表1 32位浮點數組成結構

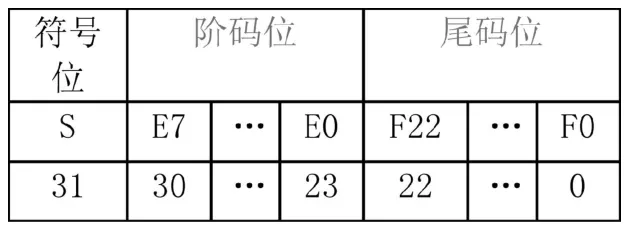

為表述方便,設有浮點數Y1和Y2,分別為:

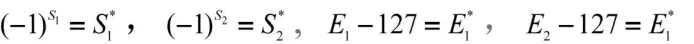

其中S1,S2為符號位;F1,F2為尾碼位;E1,E2為階碼位。令

2.浮點數加減法設計

2.1 浮點數加減法算法

如(1-3)、(1-4)兩個浮點數,其加減法運算可如下表示:

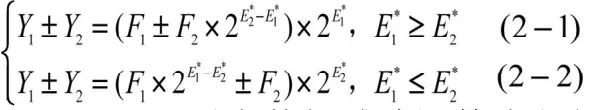

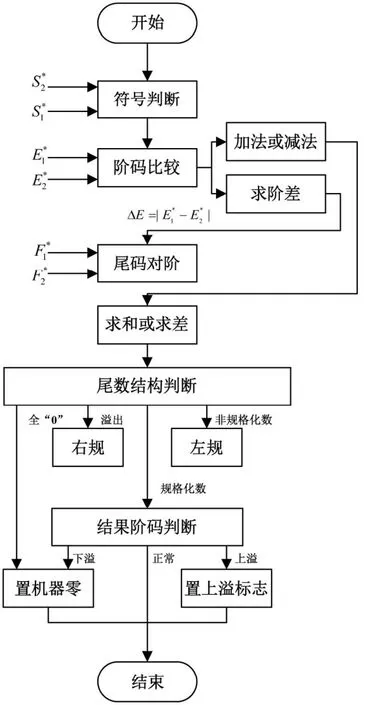

Y1和Y2兩浮點數加減法運算流程如圖1所示。其運算步驟如下:

⑷ 求和或求差:對階完畢浮點數的尾碼需要進行求和或求差;

圖1 浮點數加減法流程

2.2 加減法模塊實現

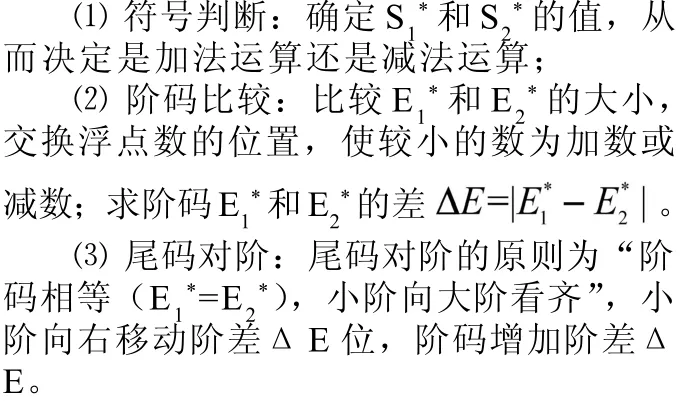

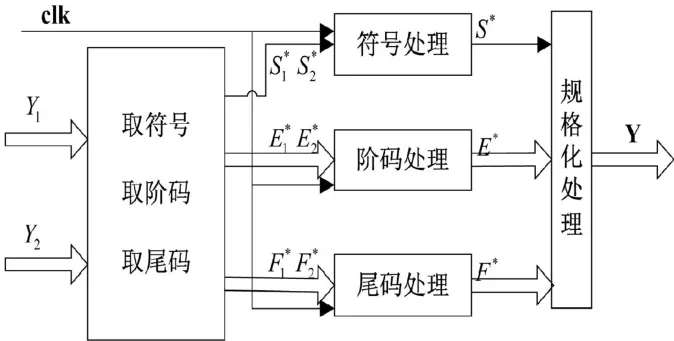

根據2.1算法,可利用Verilog HDL硬件描述語言實現浮點數加減法運算器。浮點數運算器邏輯框圖如圖2所示。

圖2 浮點運算器邏輯框

浮點數進入輸入單元后,提取出符號位、階碼位、尾碼位送到相應的運算單元進行處理,再經過規格化處理單元,得到結果。浮點運算器端口定義見表2。

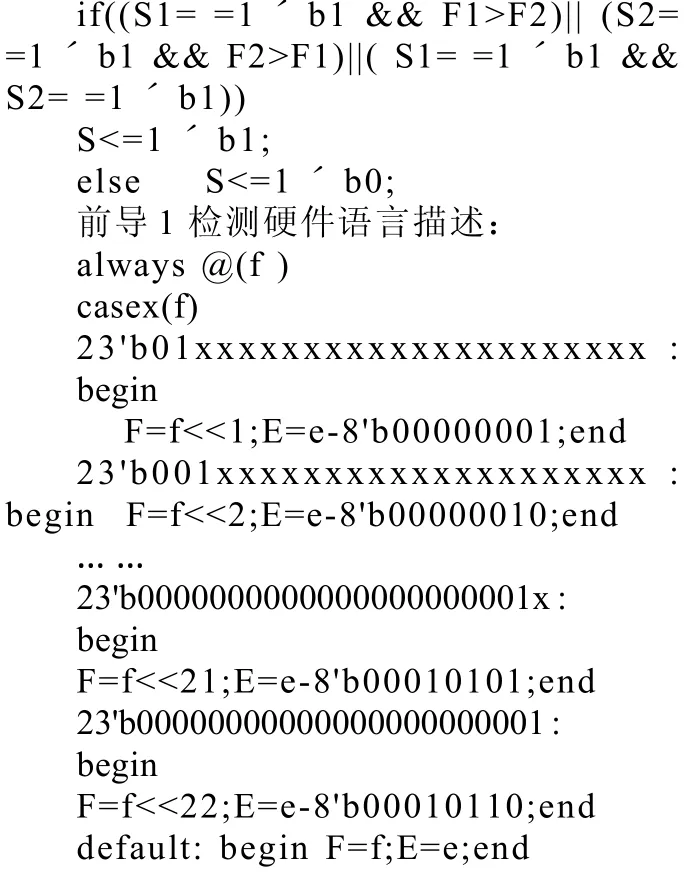

在加減法運算單元中,符號判斷和前導1檢測比較重要,前者決定運算方式和最終結果符號,后者為規格化服務。

表2 浮點運算器端口

符號判斷硬件語言描述:

其中y為兩浮點數尾碼相加或相減后的結果,e為兩浮點數階碼比較后的階碼,前導1檢測就是檢測尾碼運算結果的第一位是否為1,如不是,則左移,左移1位,階碼減1;casex語句中x表示0、1均可,如23'b001xxxxxxxxxxxxxxxxxxxx表示只判斷前三位是否001,條件成立則f左移2 位賦值給F 輸出,F 值為23'b1xxxxxxxxxxxxxxxxxxxx00,同時階碼減2(8'b00000010)。

3.浮點數乘除法設計

3.1 浮點數乘除法算法

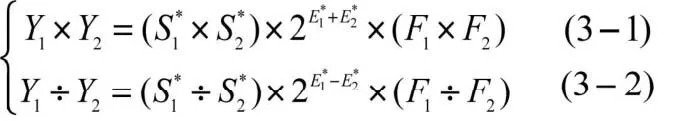

如(1-3)、(1-4)兩個浮點數,其乘除法運算可如下表示:

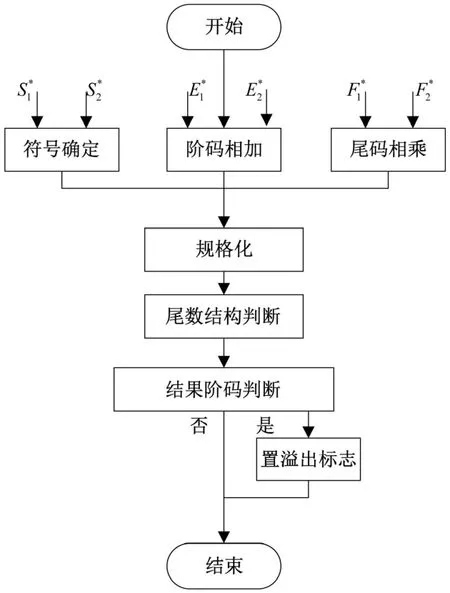

Y1和Y2兩浮點數乘除法運算流程如圖3所示。其運算步驟如下:

得出結果符號。

⑷ 規格化處理:對結果進行前導零檢測、初次規格化、尾數舍入和最終規格化得到最后結果。

圖3 浮點數乘除法流程

3.2 乘除法模塊實現

根據3.1算法,利用Verilog HDL硬件描述語言、FPGA內嵌的硬件乘法器和除法器實現浮點數乘除法運算單元。浮點數乘除法運算邏輯框圖如圖2所示。

浮點數進入輸入單元后,提取出符號位、階碼位、尾碼位送到相應的運算單元進行處理,再經過規格化處理單元,得到結果。浮點運算器端口定義見表2。

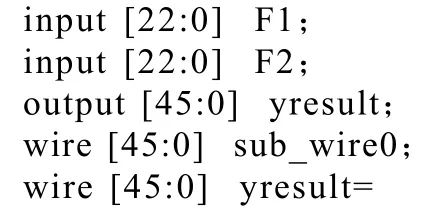

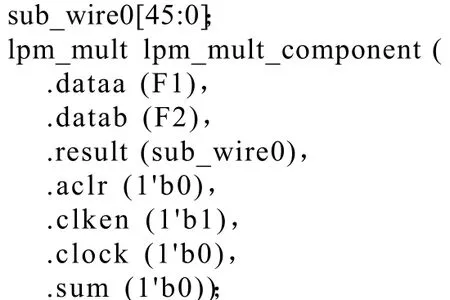

內嵌硬件乘法器和除法器可完成高速乘除法操作,精度較高。比使用邏輯單元完成乘除法運算更節省邏資源,延時更小。內嵌硬件乘法器例化描述如下:

其輸入為23位,輸出結果為45位,結果經舍入處理為23位后,規格化得到尾碼23位。

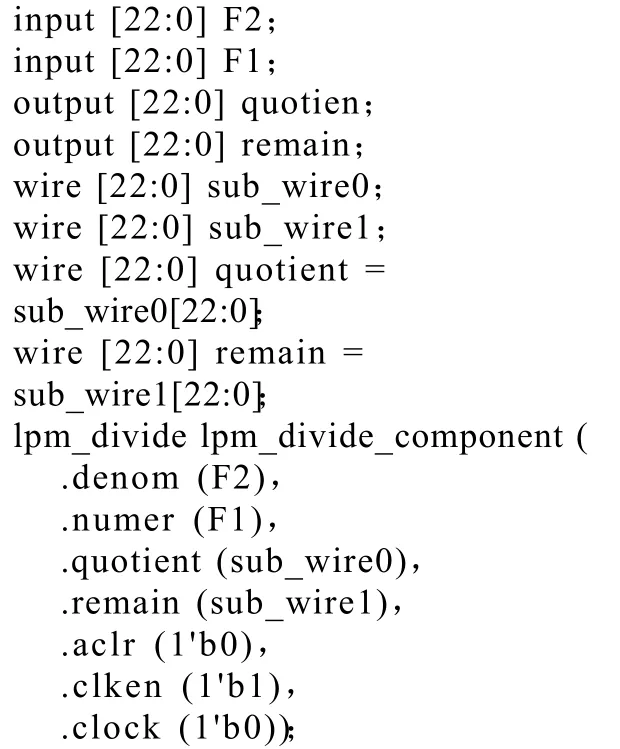

硬件除法器例化與乘法器有所不同,其結果分

為商和余數,內嵌硬件除法器例化描述如下:

其輸入為23位,輸出商為23位,余數為23位,余數經過移位與除數輾轉相除,得到最后結果。

4.浮點數運算模塊化

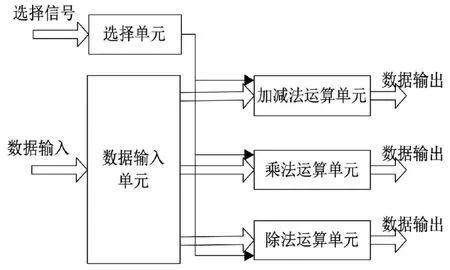

在浮點數加減、乘除運算單元的基礎上,實現三個子單元的模塊化設計,可以縮短研發周期和降低開發成本,為以后的I P核固化打下基礎。模塊由數據輸入單元、運算選擇單元和運算處理單元組成,運算處理單元包含加減法運算單元、乘法運算單元和除法運算單元。模塊通過數據輸入單元提取符號位、階碼位和尾碼位;通過運算選擇單元決定是何種運算;通過運算處理單元處理相應的運算。模塊邏輯框如圖4所示。

圖4 模塊邏輯框

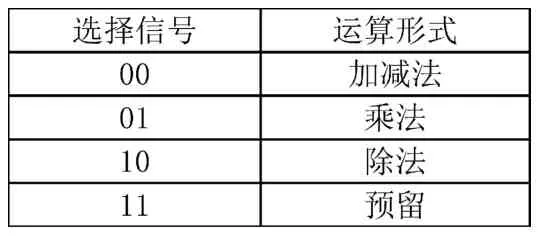

由于只有3個運算單元,選擇信號只需2位,具體選擇信號與運算單元之間關系見表3。

表3 選擇信號與運算單元關系

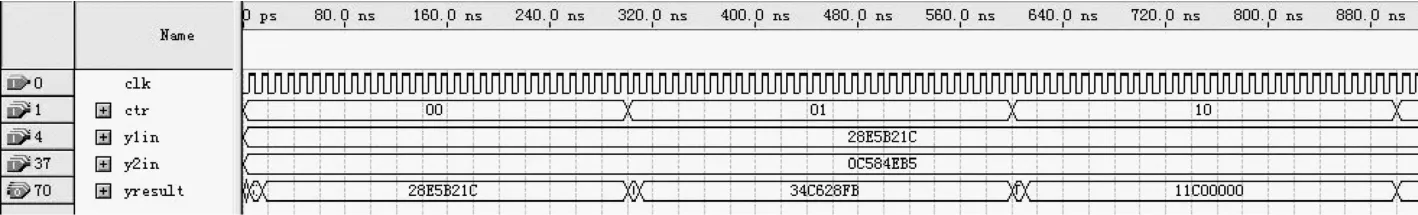

使用硬件描述言語輸入和原理圖輸入,在Altera公司的可編程邏輯器件開發軟件Quartus II中經過分析和綜合后得到的模塊封裝圖如圖5所示,模塊綜合仿真圖如圖6所示。

圖5 模塊封裝圖

圖6 模塊綜合仿真圖

仿真圖中clk(1位)是時鐘信號,ctr(2位)是運算模式控制信號;y1in(32位),y2in(32位) 為輸入信號;yresult(32位)為輸出信號。圖中控制信號是二進制格式,輸入輸出信號是十六進制格式。

5.結束語

本文詳細介紹浮點運算的加減運算和乘除運算的實現算法和技術,并在此基礎上實現三個運算單元的模塊化設計。通過Altera公司的可編程邏輯

器件開發軟件Quartus II軟件仿真,驗證了設計的正確性。

[1]劉增明,張文山.嵌入式軟件浮點運算精度分析[J].洛陽:航空兵器,2010

10.3969/j.issn.1001-8972.2011.23.034

江蘇省自然科學研究基金項目(BK2008367);南京工程學院科研創新基金項目(CKJ2009004)