基于FPGA的全幀紫外CCD驅動時序設計

胡社教, 余 升, 張 錚

(合肥工業大學 計 算機與信息學院,安徽 合 肥 230009)

隨著微電子技術和材料科學的快速發展,光電轉換技術有了長足的進步。光電檢測已不再局限于可見光,非可見光尤其以紅外和紫外應用發展迅速。紫外探測成為繼紅外和激光探測之后又一新的領域[1]。紫外全幀背照式面陣(Charge Coupled Device,簡稱CCD)以其高靈敏度和高動態范圍成為紫外探測的首選器件,廣泛應用于生命科學、物理實驗、光譜分析、工業成像及粒子圖像測試等領域。

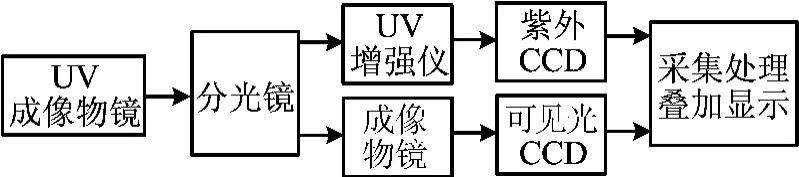

紫外探測的另一重要應用是對電暈的強度檢測和定位,它可以發現高壓電力設施的早期故障隱患,確保高壓線輸電線路正常運行。本研究是紫外-可見光雙光譜成像系統的重要組成部分,該系統利用紫外成像來完成對高壓電力設施電暈強度檢測,根據紫外圖像在可見光圖像中的位置來確定電暈的位置。紫外CCD和可見光CCD的成像和融合是系統的關鍵,紫外-可見光雙光譜成像系統結構如圖1所示。

圖1 紫外-可見光雙光譜系統結構圖

1 紫外背照明面陣

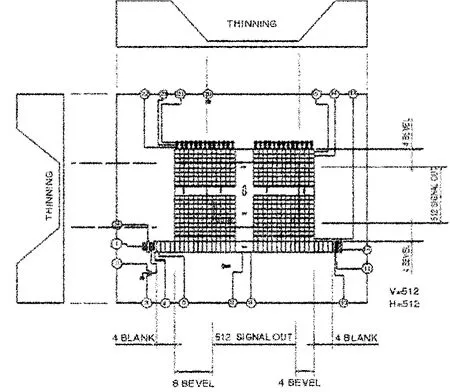

通過背照明以及勢阱耗盡的概念,CCD在寬頻帶范圍內實現高量子效率響應以及低噪聲讀出[2]。S7171-0909是濱松公司研制的多相位內嵌的背照式全幀轉移CCD,具有較寬的光譜響應范圍,特別適合紫外成像檢測。其背照式設計使得CCD具有足夠薄的襯底厚度,能使微弱光從CCD背面直接進入到芯片的有源區,該結構不需經過透明電極,保證了對紫外光的高靈敏度和量子效率,且對0.1~1 000nm的光子以及高能量帶電粒子具有高靈敏度[3]。像素合并模式設計可以降低噪聲、提高信噪比和視頻信號的幀速率。像素合并由CCD片上的時序電路控制,在視頻信號模擬放大之前設定了并行和串行寄存器的工作狀態,S7171-0909系統結構如圖2所示。

圖2 S7171-0909系統結構圖

S7171-0909芯片由感光區、存儲區、水平移位寄存器3個部分組成。為使該芯片正常工作,需要8路信號。分別為“Start”信號、2路垂直轉移脈沖P1V和P2V、水平轉移脈沖P1H和P2H、加在垂直轉移柵上的轉移脈沖(TG)、加在融合柵上的像素合并時鐘脈沖(SG)和復位脈沖(RG)。由于面陣CCD的驅動信號數量多,相位要求嚴格,且需要多種電壓的驅動,因此進行時序分析并設計出高精度的驅動時序電路是問題的關鍵。

基于單片機線陣CCD驅動電路,對于目前工藝更復雜、成像性能更好的面陣CCD,多采用可編程邏輯器件來實現[4]。文獻[5]提出了一種幀轉移CCD驅動設計方法來驗證傳感器在X射線激勵下的表現性能,雖說該設計也是基于FPGA的系統,但其硬件驅動電路都是通過水平時鐘驅動、垂直時鐘驅動以及存儲區時鐘驅動3個分立的元器件來實現的,這增加了軟件設計的復雜度和硬件調試上的難度。文獻[1]則是利用CPLD以及門電路完成CCD驅動時序的設計,其中三相時鐘是由3個D觸發器配合產生的,文獻[1,5]均能完成設計,但是在設計上均為完成硬件與軟件的合理搭配,在資源利用和效率上有待進一步改進,而且CPLD一般是在CCD工作頻率較低時比較適合,與現場可編程邏輯陣列(FPGA)相比缺乏通用性。

文獻[6]提出了一種基于FPGA分離紫外CCD數模信號的驅動設計方法,較好地達到設計目的,其缺點是在軟件設計時利用VHDL語言開發,該語言與Verilog語言相比較難掌握,還需要有Ada編程基礎,增加了開發難度。

而本設計則是以FPGA為開發平臺,在軟件上利用Verilog描述狀態有限狀態機和鎖相環形成軟核來實現主時鐘以及各路脈沖的產生,而且Verilog開發環境幾乎能實現目前能用硬件實現的所有功能,并進行功能仿真和綜合優化,從而避免了到硬件調試才會發現問題,大大縮短了開發周期,加快了復雜電路的設計,而且該設計方法更容易實現其他功能模塊接口的連接,增加系統的可靠性。

2 CCD驅動時序及參數設計

S7171-0909完成一幀圖像的采集要經歷感光、垂直轉移和水平讀出3個階段,并且有線性合并模式和陣列掃描模式,本文研究了線性合并模式,驅動時序如圖3所示。在感光階段,“start”信號處于高電平,傳感器開始接受曝光,在P1V和P2V為低電平時進行曝光積分,電荷在P1V、P2V電極形成勢阱積累。

垂直轉移電荷主要由P1V、P2V、TG配合時鐘脈沖CLK完成的,P1V的下降沿光積分結束,在P2V到達高電平后開始整幀轉移。垂直移位寄存器中的電荷在雙相垂直驅動時鐘P1V和P2V交替作用下逐行地向水平寄存器轉移,此時水平驅動時鐘P1H、P2H、SG、RG、CLAMP均保持不變,而傳輸時鐘TG與垂直驅動脈沖P2V保持同步。垂直和水平轉移循環交替進行,電荷由光敏區轉移到存取區是由與P2V同頻同相的行計數TG脈沖控制,電荷完成520行的垂直轉移后,傳感器就開始下一次的積分。

水平讀出階段主要由P1H、P2H、SG、RG、CLAMP配合時鐘脈沖CLK完成,在P1H、P2H時鐘脈沖的控制下,開始水平轉移,P1H、P2H為同頻反相的脈沖,在每一個P1H的上升也即是P2H的下降沿,并且在復位脈沖RG達到高電平時,開始逐一讀出電荷,融合脈沖SG同時亦為列計數脈沖,為避免RG抖動引入噪聲,CLAMP為RG鉗位脈沖,存儲區電荷向水平寄存器轉移并完成像素合并后輸出530個像元,有效像素為512個,其中包括8個空白像素和12個暗像素,作為輸出信號的參考電平。

圖3 垂直轉移和水平讀出時序圖

3 CCD驅動時序的FPGA實現

CCD驅動時序可以采用直接數字電路、單片機、EPROM、微處理器或數字信號處理器(DSP)和可編程器件產生。FPGA是第4代可編程器件,它將定制ASIC的高集成度、高性能的優點與可編程器件靈活性優點結合在一起,從而避免了定制ASIC的高成本、高風險、長設計周期和可編程器件密度低的缺點[7]。

本文采用FPGA進行邏輯電路的設計,用Verilog HDL描述時序邏輯。設計采用Altera公司的Cyclone II系列芯片EP2C8作為硬件平臺,該芯片含有8 256個邏輯單元,容量為162k的RAM、內嵌18個乘法器、2個PLL以及最多可以使用的182個I/O引腳。FPGA工作需要提供I/O供電電壓、內核(內嵌CPU或DSP)工作電壓以及輔助工作電壓。典型的I/O電壓有3.3、2.5、1.8V,目前90nm工藝的 FPGA 內核電壓為1.2V,輔助電壓根據內嵌功能塊不同,在1.2~ 2.5V。在本芯片中輔助供電2.5V 為PLL供電電壓。

EP2C8提供3.3V有源主時鐘50MHz的晶振,設計輸入信號為3路,輸出為8路信號。S7171-0909工作頻率為1MHz,工作時512×512像素參加曝光,考慮幀轉移和像素合并以及像素讀出所占用的時間,幀頻為96幀/s,由于CCD各個驅動信號間的嚴格時序要求,本設計采用多計數器和雙循環套嵌方式實現。曝光結束后,垂直電荷轉移和水平像素輸出構成內循環,通過主時鐘、垂直計數器和水平計數器控制實現。由“Start”信號、復位脈沖和主時鐘控制外循環,以雙重循環狀態機實現對整個工作過程的控制。

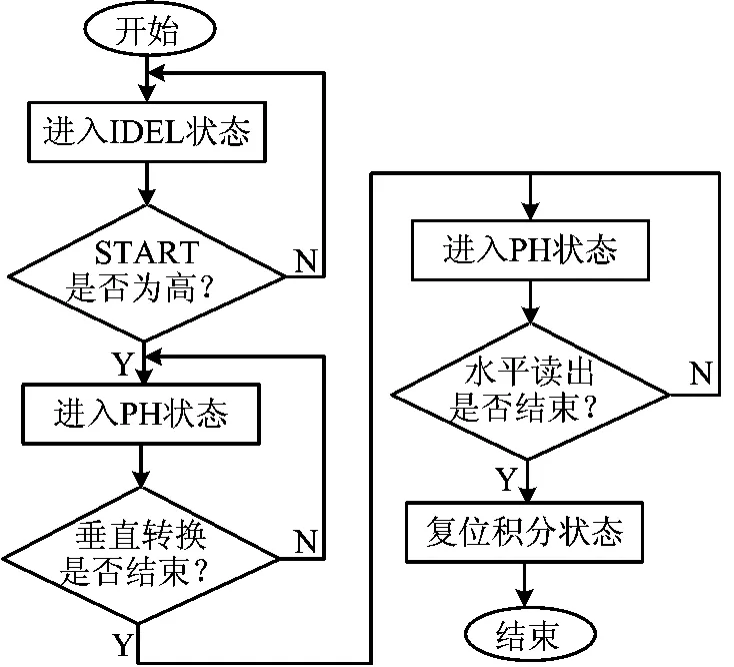

狀態機流程圖如圖4所示,狀態機的4個狀態分別為IDLE、積分狀態、PV、PH。其中IDLE:復位時鐘(nRST)為低電平時為空閑狀態,主時鐘、垂直、水平計數器都清零,P1V=0,P1H=1。積分狀態:復位時鐘(nRST)為高電平時開始積分,“Start”為高電平,轉到狀態PV。狀態PV:P1V=0,P1H=1,開始垂直電荷轉移,垂直寄存器開始計數;電荷向水平寄存器內轉移520行后,轉向狀態PH,否則,自循環。狀態PH:水平讀出狀態;水平計數器計數,完成水平讀出532個像元后,轉向IDLE狀態,否則自循環。其中“Start”為場有效標志,當“Start”=1時,進入積分狀態,開始下一幀的工作。

圖4 狀態機流程圖

4 功能仿真

針對FPGA/CPLD開發應用,Altera公司提供了完整的多平臺設計環境Quartus II,它含有FPGA和CPLD設計所有階段的解決方案,支持設計輸入、邏輯綜合、布局布線、仿真、時序分析、功耗管理以及最后的下載配置。設計時主要有原理圖輸入、Verilog語言輸入和波形圖輸入3種輸入方式,目前的設計大都采用Verilog語言進行代碼設計,并且軟件支持第三方軟件對工程設計進行仿真測試,以便及時查錯,對設計做出調整。

Verilog HDL是用于邏輯設計的硬件描述語言,并且都已成為IEEE標準[8],因此可以容易地把設計移植到不同廠家的不同芯片中去,從而增加了設計的靈活性,縮短工程周期。在設計時,不需要底層電路原理圖,而是在頂層根據設計目標進行邏輯功能的設計和模塊的劃分,然后進行代碼設計、綜合優化、實現。該硬件語言在設計具體功能模塊時,與具體器件的制作工藝沒有關系,容易完成工藝映射[9]。本文利用Verilog HDL設計自頂向下與自底向上相結合的方法設計CCD的時序脈沖。在對Verilog語言描述的時序狀態機發生器進行編譯后,并編寫Testbench測試文件,再調用第三方仿真軟件Modesim對驅動時序發生器進行功能仿真,仿真結果如圖5所示。

由圖5可看出,CLK、START、P1V、P2V及TG各路時鐘脈沖與圖3a垂直轉移時序保持一致,CLK、START、P1H、P2H、SG、RG 及CLAMP各路時鐘脈沖與圖3b水平轉移時序保持一致,由此說明該芯片的驅動時序脈沖能夠完全滿足芯片對時序以及相位關系的要求,為后續硬件實現奠定了基礎。

5 硬件實現

CCD時序驅動電路由直流偏置電壓、FPGA組成的CCD時鐘信號產生電路和驅動電路3部分組成[10]。系統供電電源模塊要求提供(+5、+15、-15、+24V)4個等級的電壓為系統提供直流偏置。FPGA的I/O輸出信號的電壓等級為0~3.3V,無法滿足各路時序脈沖的電壓等級,CCD驅動電路的作用是把FPGA時序單元產生的時序脈沖進行功率放大,以滿足CCD對波形電壓電流以及時序的要求。

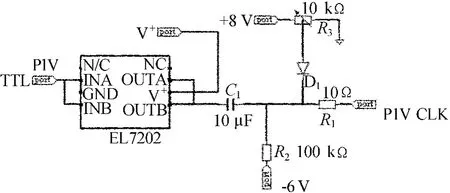

本文將FPGA產生的TTL邏輯電平轉換到-6、8V2個電壓等級。對于為容性負載的CCD,在供給較大擺幅的電壓情況下,需要在電壓快速變化延時為其提供足夠大的瞬態電流,因此要選擇工作電流足夠大的器件以滿足要求[11]。本文采用EL7202對各路脈沖進行放大以完成對CCD的驅動。

EL7202可以驅動較大的電容負載,最大脈沖電流可達2A,最高輸出電壓大于15V。負載電容為1 000pF時,上升和下降沿分別為10ns和13ns(典型值)。垂直移位寄存器在電容CP1VCP2V為6 400pF以及轉移柵電容70pF時上升和下降時間Tprv、Tpfv均為200ns,水平移位寄存器在電容CP1HCP2H為120pF以及融合柵電容為30pF時上升和下降時間Tprh、Tpfh均為10ns,復位柵電容為30pF時上升和下降時間Tprr、Tpfr為5ns,該芯片能夠滿足信號上升和下降速度的匹配,并完成對TTL信號功率放大的要求。該Elantec驅動EL7202接受TTL輸入以及垂直、水平轉移所需的CCD時鐘電壓的峰值,該峰值是可以調整的,驅動輸出為交流電壓,提供可調整的從負極到正極的時鐘偏移。垂直、水平時鐘脈沖驅動電路圖如圖6所示。圖6中,R1為水平脈沖電壓匹配電阻,R2為下拉匹配電阻,通過調整R3可以調整垂直脈沖偏壓。設置電容C1的大小,可以調整上升和下降時間。

圖6 EL7202應用電路

仿真后給開發板上電,程序下載方式設置為JATG下載配置,把程序下載到EP2C8芯片中,最后通過板級調試對CCD器件進行成像實驗,如圖7所示,表明S7171-0909芯片工作正常穩定,達到了預期效果。

圖7 不同電荷容量時CCD輸出波形

6 結束語

本文以EP2C8為硬件平臺,在Quartus II 9.1環境下,完成了S7171-0909驅動時序電路,該軟件設計基于狀態機設計,使CCD工作模式更加清晰,有利于后續對數據的傳輸和處理的控制。對于其他類型的CCD器件驅動設計,只需修改一些參數即可,因此該狀態機設計有一定的通用性,可以縮短開發周期。本課題選用高性能的電壓轉換芯片和驅動器保證CCD的正常穩定工作。

[1] 姚鳴暉,李自田,劉 軍.紫外面陣CCD驅動時序設計[J].微計算機信息,2008,24(11):281-289.

[2] Meidinger N,Andritschke R,Assmann W,et al.CCD detector development for the eROSITA space telescope[C]//2010IEEE Nuclear Science Symposium Conference Record(NSS/MIC),2010:24-31.

[3] Tower J R,Swain P K,Hsueh F L,et al.Large Format Backside Illuminated CCD Imager for Space Surveillance[J].IEEE Transactions on Electron Devices,2003,50(1):218-224.

[4] 韋曉茹,居戩之.基于單片機ATmegal6的CCD驅動電路的設計[J].微型機與應用,2010,29(16):33-36.

[5] 姚 遠.高速線陣CCD的驅動分析與設計[J].合肥工業大學學報:自然科學版,2009,32(4):560-563.

[6] 馬慶軍,宋克非,曲 藝,等.紫外臨邊成像光譜儀CCD電路系 統 的 設 計 [J].光 學 精 密 工 程,2011,19(7):1538-1544.

[7] 程鵬飛,顧明劍,王模昌.基于FPGA的幀轉移面陣CCD驅動電路設計[J].紅外技術,2006,28(9):519-522.

[8] 夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2008:13-14.

[9] 雷伏容.VHDL電路設計[M].北京:清華大學出版社,2006:6-8.

[10] Lee H L,Madden T,Fernandez P,et al.Kodak CCD-based detector for small angle X-ray scattering[C]//2009 IEEE Nuclear Science Symposium Conference Record(NSS/MIC),2009:1807-1810.

[11] 薛旭成,曲洪豐,李洪法,等.CCD相機功率驅動電路設計[J].微計算機信息,2007,23(25):272-273.