基于FPGA的DVB-C系統編碼器的設計

陳慶旭,孫 曼,植 涌

(四川大學電氣信息學院,四川 成都 610065)

由于種種原因造成數字信號傳輸的數據流出現誤碼,從而導致接收端產生圖像不連續、跳躍等現象,因此信道編碼就顯得尤為重要。信道編碼可增加通信的可靠性,極大地避免傳送碼流中誤碼的發生,并在信道中加入糾錯、交織等處理誤碼的技術。該文介紹了DVB-C系統中編碼器的實現,將其分為擾碼、RS編碼、卷積交織、QAM調制4個部分,并對其中的RS編碼和卷積交織做了重點介紹,提出一種基于FPGA的實現方案。

1 DVB-C系統的硬件實現

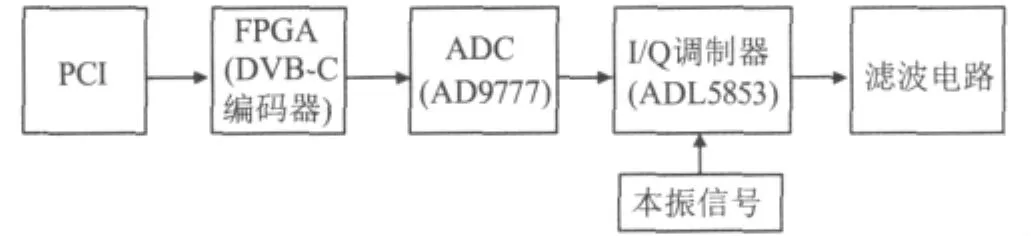

圖1為DVB-C編碼系統的硬件實現圖。

圖1 DVB-C編碼系統的硬件實現圖

DVB-C編碼系統的硬件實現包括5個部分:

1)PCI接口。該系統采用Altera公司CPLD MAXII系列中的EPM1270256C5實現PCI接口。因為MAXII的功耗和成本大幅降低,資源密度和性能卻顯著提升,非常適用于接口協議,又因為只在EPM1270和EPM2210的I/O Bank 3中有PCI鉗位二極管,故此設計選用EPM1270256C5[1]。

2)DVB-C編碼器。該系統采用Altera公司的CycloneIII系列中的EP3C55F484C6完成了編碼器的設計。

3)ADC。ADC模塊采用ADI公司的AD9777數模轉化器,它非常適合那些要求高調制精度(即64 QAM以上)的應用,可以抑制模擬混頻操作固有的鏡像,從而減少濾波級的數量,降低實現3G和寬帶頻譜發射所需硬件的成本[2]。

4)I/Q調制器、本振信號。I/Q調制器采用ADL5385,它是一款硅單芯片正交調制器,設計用于50~2200 MHz頻率范圍。其出色的相位精度和幅度平衡可以為通信系統提供高性能中頻或直接射頻調制。ADL5385 從兩路差分基帶輸入獲得信號,并將其調制到兩個彼此正交的載波上。兩個內部載波均源自一路單端、外部本振輸入信號,其頻率為目標載波輸出頻率的兩倍。經過調制的兩路信號通過差分轉單端放大器相加,驅動50 Ω負載。該振信號的產生采用的是 ADF4351,其輸出頻率范圍為35 ~4400 MHz。

5)濾波電路。濾波網絡采用低通濾波器,將濾波器的截止頻率分成 80 MHz,120 MHz,180 MHz,225 MHz,400 MHz,630 MHz,1200 MHz共7 個等級。

2 DVB-C系統編碼器的FPGA設計與實現

圖2為DVB-C系統編碼器的FPGA過程圖。

圖2 DVB-C系統編碼器過程

DVB-C系統編碼器的過程分為4個部分:

1)同步反轉數據擾碼。在DVB-C標準中,每188個字節組成1個MPEG-2數據幀,每個MPEG-2的第1個字節(47 H)為同步字節。每8個MPEG-2數據幀組成1個傳輸包,并且每1個傳輸包的第1個字節要取反輸出[3]。然后進行擾碼處理,避免出現長串的0或1。

2)RS編碼。在每1幀的數據輸入之后,要進行RS編碼,編碼的目的是為了糾正突發錯誤。編碼過后會產生16個校驗位,每1幀的字節長度變成204。

3)卷積交織。卷積交織加入之后可以進一步增強抵御突發差錯的能力,卷積交織改變數據的傳輸順序從而提高抗突發誤碼的能力。

4)QAM調制。QAM調制分為從字節到字符的轉換、差分編碼、星座映射3個部分組成。字節到字符的轉換把字節轉化成調制需要的符號流,在轉換完成后,應對符號的最高2位進行差分編碼,經過星座映射完成I/Q正交。

2.1 同步反轉數據擾碼

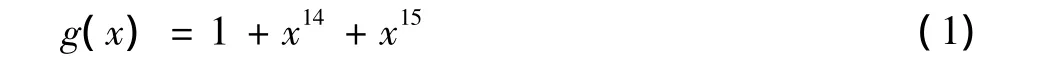

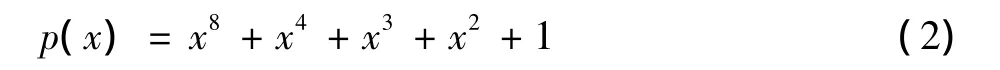

在信號初始化的過程中,數據要進行同步翻轉,即每1個傳輸包的第1幀同步字節應該取反輸出,然后對數據進行擾碼(即能量擴散)。在DVB-C系統中傳輸的數據流為了保證出現“0”與“1”的概率相等,即各為50%,必須對輸入的數據流進行擾碼。擾碼是通過偽隨機二進制序列發生器來完成的。DVB-C系統中實現擾碼的偽隨機序列的生成的多項式為

經過擾碼處理后,輸出的數據流出現“0”與“1”的概率近似相等了,而且減小了對其他通信設備的干擾,有利于載波的恢復。

2.2 RS編碼

2.2.1 RS編碼原理

RS碼既可以糾正隨機誤碼,也可以糾正突發誤碼,它廣泛應用在數字電視傳輸系統中。RS碼是目前效率最高、應用最廣的糾錯編碼之一。

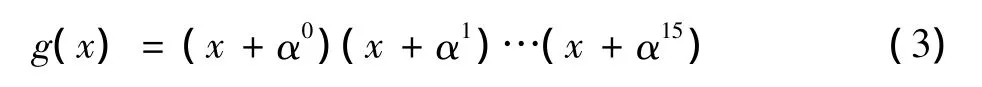

經過擾碼之后的數據流要進行RS編碼,在DVB-C系統中,它采用 RS(204,188,8)碼[2],每 1 個數據幀要用16個校驗符號,即188個符號產生16個校驗符號,編碼后總數為204 個符號。RS(204,188,8)是 RS(255,235,8)的截短碼,它是在GF(28)域上得到的[4]。GF(28)域上的生成多項式為

碼字生成多項式為

2.2.2 RS編碼的實現

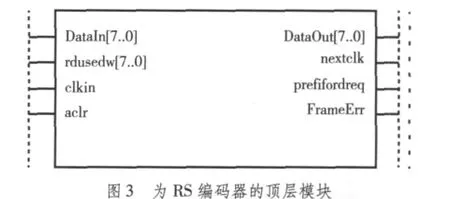

圖3為RS編碼器的頂層模塊實現框圖,DataIn[7..0]和DataOut[7..0]分別為RS編碼的輸入和輸出,cklin為時鐘信號,aclr為復位信號。FrameErr為監視信號的同步。根據RS編碼原理,在送入第188個數據后就必須停止輸入,直到校驗數據全部輸出為止。圖4為RS編碼的仿真,輸入為1~188的循環。輸出前188個字節為1 ~188,16 個校驗位195,231,90,194,142,112,85,171,63,242,251,154,1,82,33,222。

2.3 卷積交織

2.3.1 卷積交織的原理

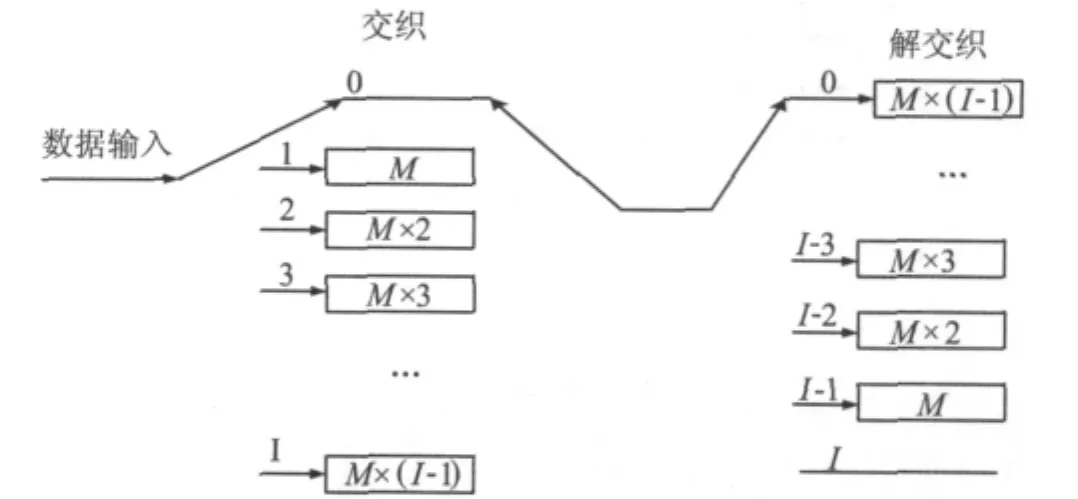

交織主要是把連續出現的突發誤碼散成便于糾正的隨機誤碼,為正確譯碼創造條件。交織過程中只需要打亂碼元的順序排列,因此不會降低傳輸效率,經過交織之后,系統的糾錯能力得到進一步提高。在DVB-C系統中采用卷積交織方法[5],卷積交織的基本原理如圖5所示。其中I表示交織深度。交織器由I=12個分支組成,每1個分支都有先進先出(FIFO)(其中M=17)移位寄存器。經過RS編碼的數據按照順序分別進入I條分支延遲器,每1路分支延遲各不相同。第1路無延遲,接下來的每1路分支以延遲M=17個周期遞增,直到第12路的分支延遲為17×11。

圖5 卷積交織與解交織

2.3.2 卷積交織的實現

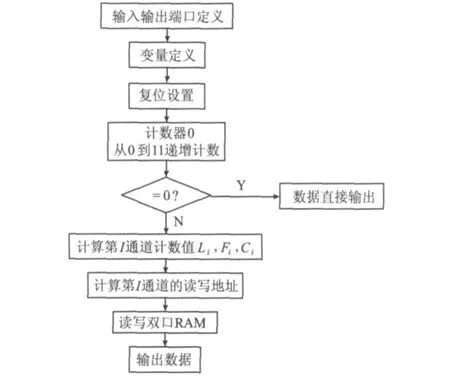

為了實現延遲,最簡單的方法就是給每條延遲通道分配一定長度的FIFO移位寄存器,但是這種方法需要的FIFO移位寄存器為1122 個。該設計采用雙端口RAM代替FIFO移位寄存器,采用RAM整塊循環移位法,從而節省大量的存儲單元,且代價小,是理想的方法[6]。圖6為卷積交織的設計流程圖,其中Ci為第I道的計數值,Fi為通道的首地址,Li為通道的尾地址。RAM的讀寫規律為:

圖6 卷積交織的設計流程圖

第I通道讀地址為Ci+Fi。

相對應的寫地址為Li,當Ci不為0時,Ci+Fi-1;當Ci為0 時,為 Li。

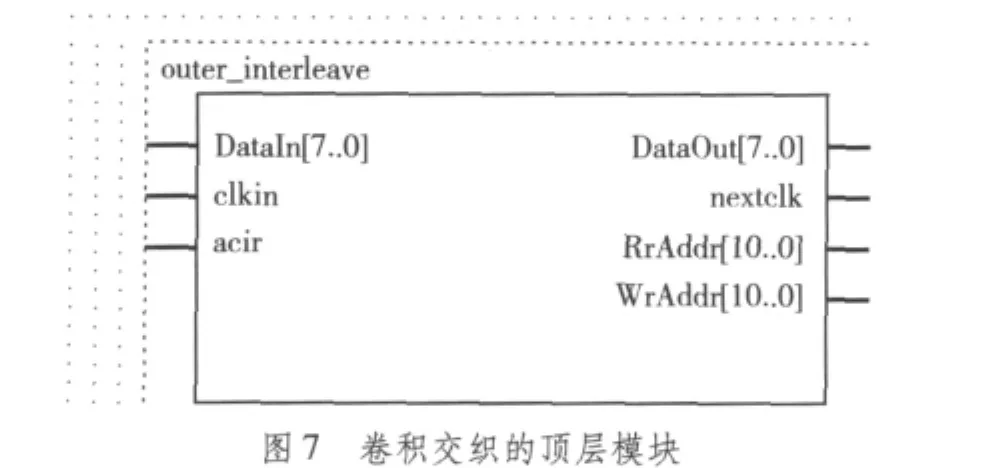

圖7為卷積交織器的頂層模塊圖,其中clkin為系統時鐘信號,aclr為復位信號,DataIn[7..0]是數據輸入端,DataOut[7..0]是數據輸出端,RrAddr[10..0]為雙口RAM的數據讀地址,WrAddr[10..0]為雙口RAM的數據寫地址。圖8為卷積交織的仿真,輸入為0~255的循環。這是第2幀的輸出,第2幀的第1個字節輸出為204,第2個字節為前1幀的第2個字節,即1。

2.4 QAM調制

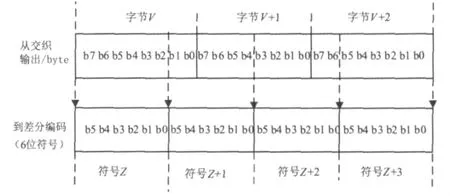

DVB-C系統采用了多電平正交幅度調制技術(MQAM),可以在2m-QAM(m=4,5,6,7,8)中選擇。為了調制的方便,在2m-QAM調制之前,要進行字節到符號的映射。映射的符號高位取字節的高位,這個字節剩下的位和下個字節的高位組成下個符號。圖9是64-QAM的映射過程。

圖9 64-QAM時字節到m比特字符的轉換

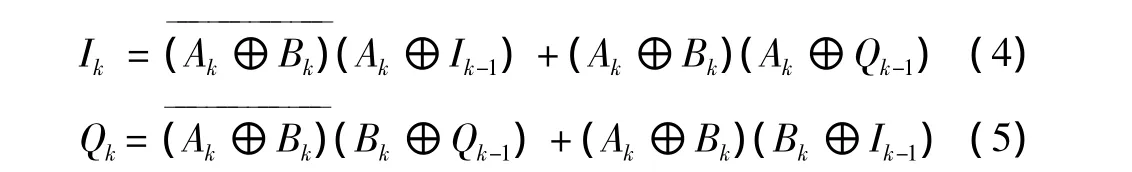

經過字節到符號的轉化后,需要對符號進行映射,同時為了獲得π/2旋轉不變QAM星座圖,需要對每個m比特符號的最高位Ak與次高位Bk進行差分編碼[7],公式為

圖10是QAM調制的過程,QAM調制采用雷格碼在星座圖上的差分編碼映射,這樣能夠消除相位模糊的問題。

圖10 QAM調制過程

3 結論

采用Altera公司的EP3C55F484C6芯片設計了DVB-C系統的編碼器,此芯片有55856 個邏輯單元,整個編碼器用了1391 個邏輯單元,占用率不到1%。通過實現了DVB-C系統編碼器的設計,所有模塊都在Quartus II 10.0中通過了驗證,且用modelsim進行了仿真,并給出了整個編碼器的仿真結果,仿真如圖11所示。

圖11 仿真結果(截圖)

[1]MAX II Device handbook chapter 8:using MAXII Devices in multi-voltage systems[EB/OL].[2011-09-10].http://www.altera.com/literature/hb/max2/max2_mii51009.pdf.

[2]AD9777:16-Bit,160 MSPS 2x/4x/8x Interpolating Dual TxDAC+D/A Converter[S].2006.

[3]GB20600—2006,Framing structure,channel coding and modulation for digital television terrestrial broadcasting system[S].2006.

[4]梁煒新,王群生.基于FPGA的通用RS編解碼器的VHDL設計方法[J]. 電視技術,2004,28(3):16-20.

[5]梁小萍,肖嵩.卷積交織器和解交織器的VHDL設計和FPGA實現[J]. 制造與設計,2004,27(20):102-103.

[6]HANNA S A.Convolutional interleaving for digital radio communications[C]//Proc.ICUPC 1993.[S.l.]:IEEE Press,1993:443-447.

[7]KOUKOURLIS C S,HOULIS P H,SAHALOS J N.A general purpose differential digital modulator implementation incorporating a direct digital synthesis method.member[J].IEEE Trans.Broadcasting,1993,39(4):383-389.