基于FPGA的實時直方圖統(tǒng)計設(shè)計

張 科,徐書文,葛 珊

(中國電子科技集團公司第三研究所,北京 100015)

1 直方圖統(tǒng)計方法簡介

直方圖可以提供圖像灰度分布的統(tǒng)計特征,是圖像處理的基本方法之一。直方圖統(tǒng)計方法常應(yīng)用于圖像增強、圖像壓縮和圖像分割等圖像處理基礎(chǔ)理論分析和應(yīng)用中,也廣泛應(yīng)用于遙感、遙測、成像跟蹤與制導(dǎo)等軍事領(lǐng)域中。

隨著DSP[1]應(yīng)用技術(shù)的發(fā)展,利用DSP完成實時直方圖統(tǒng)計的方法主要有3種:1)專用DSP芯片;2)DSP+片內(nèi)DRAM結(jié)構(gòu);3)DSP+片外DRAM結(jié)構(gòu)。

第一種專用DSP芯片是指通過簡單外圍控制設(shè)置完成固定直方圖統(tǒng)計功能的電路;第二種DSP+片內(nèi)DRAM結(jié)構(gòu)是指DSP芯片自身具有大容量片內(nèi)DRAM,并有專用的視頻接口,通過DSP編程實現(xiàn)直方圖統(tǒng)計功能,如圖1所示;第三種DSP+片外DRAM結(jié)構(gòu)是用片外DRAM做幀存,采用乒乓切換控制數(shù)據(jù)存儲。當(dāng)1個幀存寫數(shù)據(jù)時,DSP對另一幀存進行讀操作,通過DSP編程實現(xiàn)直方圖統(tǒng)計功能[2-4],如圖2 所示。

圖1 DSP+片內(nèi)DRAM結(jié)構(gòu)

圖2 DSP+片外DRAM結(jié)構(gòu)

使用專用DSP芯片實現(xiàn)直方圖統(tǒng)計時,速度快、實時性好,可以達(dá)到像素時鐘的速度。但是這種專用DSP芯片只能用于直方圖統(tǒng)計,不能改作其他用途,而且體積大,不利于小型化。對于DSP+片內(nèi)DRAM結(jié)構(gòu)和DSP+片外DRAM結(jié)構(gòu),是通過DSP編程實現(xiàn)直方圖統(tǒng)計的,實時性稍差,并且實現(xiàn)直方圖統(tǒng)計功能占用了DSP運行時間和資源。但是,這2種結(jié)構(gòu)靈活性很好,通過改變DSP程序就可以改作其他用途。

本文介紹了一種采用基于FPGA[5]實現(xiàn)實時直方圖統(tǒng)計功能的設(shè)計方案,該設(shè)計方案不占用DSP資源,實時性可以達(dá)到像素時鐘的速度;通過改變程序,可以改作其他用途。這就是說,采用FPGA實現(xiàn)實時直方圖統(tǒng)計設(shè)計方案既繼承了上述3種結(jié)構(gòu)的優(yōu)點,同時又克服了上述3種結(jié)構(gòu)的缺點。

2 邏輯結(jié)構(gòu)及原理

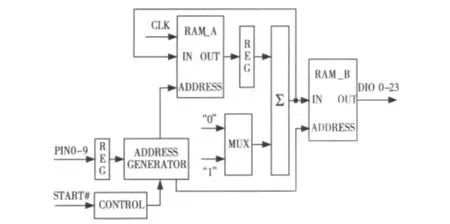

對于灰度級為[0,L-1]范圍的數(shù)字圖像,其直方圖是離散函數(shù)h(rk)=nk,這里rk是第k級灰度,rk∈[0,L-1],nk是圖像中灰度級為rk的像素個數(shù)。直方圖直觀地反映了1幅圖像灰度的分布情況,是圖像分割算法中常用的方法。灰度直方圖的特點是橫坐標(biāo)為灰度值rk,縱坐標(biāo)為像素數(shù)nk。在FPGA設(shè)計中實現(xiàn)直方圖統(tǒng)計,首先要考慮圖像灰度值和統(tǒng)計值的映射關(guān)系,在這里采用了雙RAM結(jié)構(gòu),用圖像灰度rk作為RAM的地址,RAM中的數(shù)據(jù)對應(yīng)像素數(shù)nk,從而實現(xiàn)在存儲器中灰度和像素數(shù)的對應(yīng)關(guān)系,基于FPGA的實時直方圖統(tǒng)計原理如圖3所示。在圖3中,CLK為像素時鐘;START#為直方圖統(tǒng)計起始信號;PIN 0-9為10位的像素灰度數(shù)據(jù)輸入;DIO[23..0]為灰度對應(yīng)像素數(shù)的統(tǒng)計結(jié)果。圖中RAM_A用于完成直方圖統(tǒng)計像素數(shù)的讀取、累加和回寫,RAM_B通過外部CPU配置讀使能和讀地址,用于讀取直方圖統(tǒng)計最終結(jié)果。

圖3 基于FPGA的實時直方圖統(tǒng)計原理框圖

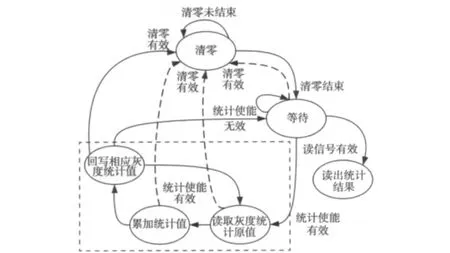

FPGA的軟件編程采用VHDL語言,在QuartusII9.0集成開發(fā)環(huán)境綜合,F(xiàn)PGA軟件設(shè)計采用mealy型有限狀態(tài)機。為了實現(xiàn)1個像素灰度值的直方圖統(tǒng)計在相應(yīng)的像素周期內(nèi)完成,需要在1個像素時鐘周期內(nèi)分別實現(xiàn)RAM數(shù)據(jù)的讀出、累加、寫入,因此,這里選用4倍頻像素時鐘作為直方圖統(tǒng)計的同步時鐘。從設(shè)計的邏輯完備性考慮,需要考慮各種狀態(tài)轉(zhuǎn)換的情況,防止出現(xiàn)由于外部信號時序沖突導(dǎo)致的未知狀態(tài)而不能跳轉(zhuǎn)。直方圖實現(xiàn)過程中可能出現(xiàn)的各種狀態(tài)及跳轉(zhuǎn)關(guān)系如圖4所示。

圖4 直方圖統(tǒng)計狀態(tài)轉(zhuǎn)換圖

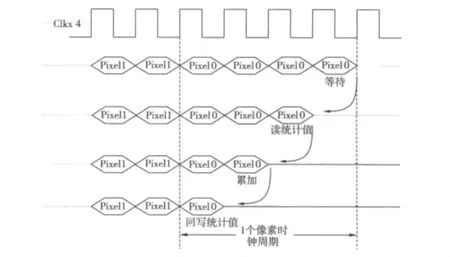

從圖4中可以看到,整個設(shè)計有4個狀態(tài),即清零、等待、直方圖統(tǒng)計、讀出統(tǒng)計結(jié)果,各狀態(tài)轉(zhuǎn)換由外部控制信號觸發(fā)。其中,清零信號的優(yōu)先級最高,其次是統(tǒng)計使能信號,讀信號在統(tǒng)計結(jié)束后有效,等待狀態(tài)為中間空閑態(tài)。直方圖統(tǒng)計狀態(tài)中還有4個子狀態(tài),即空閑(等待)、讀取灰度統(tǒng)計原值、累加統(tǒng)計值、回寫相應(yīng)灰度統(tǒng)計值,這4個子狀態(tài)以4倍頻像素時鐘為同步時鐘進行流水操作,如圖5所示。

圖5 灰度統(tǒng)計值累加時序

該設(shè)計中像素灰度位寬為10 bit,因此RAM地址需要1024個;直方圖統(tǒng)計模塊像素灰度統(tǒng)計數(shù)值位寬為24 bit,即1幅圖像的像素數(shù)最大可以達(dá)到16 Mbit,RAM需要的緩存空間為1024×24 bit=24576 bit,滿足一般實時圖像分辨力的要求。依據(jù)上述直方圖設(shè)計分析,F(xiàn)PGA芯片選用Altera公司CycloneⅡ系列器件EP2C5Q208I8N芯片,該芯片屬于Altera公司低成本的FPGA系列,容量中等。EP2C5Q208I8N的主要資源包含:1)內(nèi)部邏輯單元多達(dá)4608個,最大系統(tǒng)門數(shù)約合9萬門以上;2)RAM資源共計119808 bit,可以由用戶配置為FIFO,DPRAM等模塊;3)2個鎖相環(huán);4)13個18×18的嵌入式乘法器;5)IO管腳數(shù)為142。

針對該設(shè)計,該款FPGA芯片資源有較多冗余,具有可擴展性。如果需要處理更高分辨力的圖像,可依據(jù)該設(shè)計提供的方法選用資源更豐富的FPGA芯片。

3 設(shè)計仿真及驗證

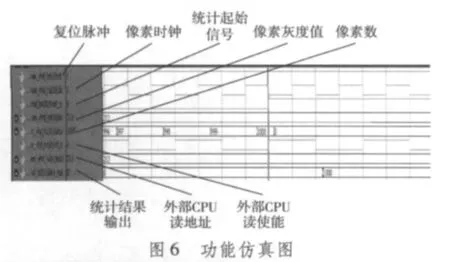

該設(shè)計采用Modelsim軟件進行功能仿真,為了便于驗證,仿真時選取連續(xù)相同灰度進行統(tǒng)計,仿真結(jié)果如圖6所示。圖6中rst為清零脈沖信號;clk為像素時鐘;start_n為直方圖統(tǒng)計起始信號;pin為像素灰度值;data為回寫雙RAM的灰度統(tǒng)計值;rd_n為微處理器讀取統(tǒng)計結(jié)果的讀信號;add為微處理器讀取統(tǒng)計值的相應(yīng)灰度值;data_out為微處理器讀出的統(tǒng)計數(shù)據(jù)。start_n選通了1000個像素時鐘周期,因此,像素統(tǒng)計結(jié)果為1000個。

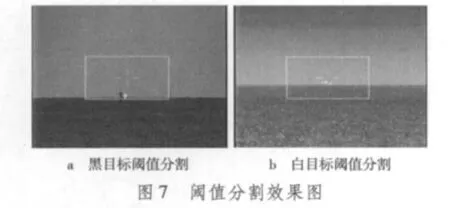

該設(shè)計還在某設(shè)備的閾值分割電路中得到應(yīng)用,閾值分割電路采用目標(biāo)灰度直方圖實時統(tǒng)計進行分割門限的實時計算,從而實現(xiàn)目標(biāo)的實時分割,如圖7所示。在圖7中,波門內(nèi)十字線下部的白色標(biāo)記為分割出的目標(biāo)部分。

4 結(jié)論

本文提出了一種基于FPGA的實時直方圖統(tǒng)計設(shè)計原理和方法,并經(jīng)過軟件仿真和實際應(yīng)用硬件電路的驗證,實驗結(jié)果證明該設(shè)計不僅實時性強,占用系統(tǒng)資源少,滿足設(shè)計需求,而且,采用VHDL語言編程,程序的可移植性強,可以方便地移植到更大規(guī)模的FPGA芯片中,為數(shù)字圖像的直方圖實時統(tǒng)計處理提供了1種實用的方法。

[1]韓文俊,張艷艷,任國強,等.基于雙DSP的實時高清H.264視頻編碼器實現(xiàn)[J]. 電視技術(shù),2010,34(5):33-35.

[2]李弼程,彭天強,彭波.智能圖象處理技術(shù)[M].北京:電子工業(yè)出版社,2004.

[3]阿森頓.VHDL設(shè)計指南[M].葛紅,黃河,吳繼明,譯.北京:機械工業(yè)出版社,2005.

[4]Harris Semiconductor.HSP 48410 datasheet[EB/OL].[2011-10-10].http://www.datasheets.org.uk/HSP48410/Datasheet-028/DSA00501738.html.

[5]王德勝,康令州.基于FPGA的實時圖像采集與預(yù)處理[J].電視技術(shù),2011,35(3):32-35.