基于DSP系統的FPGA精插補器設計

喬 橋,范良志

QIAO Qiao,FAN Liang-zhi

(武漢紡織大學 機電學院,武漢 430074)

0 引言

FPGA是新型的大規模可編程數字集成電路器件。它充分利用計算機輔助設計技術進行器件的開發與應用。用戶借助于計算機不僅能自行設計專用集成電路芯片,還可在計算機上進行功能仿真和實時仿真,及時發現問題,調整電路,改進設計方案。這樣,設計者不必動手搭接電路、調試驗證,只須在計算機上操作很短的時間,即可設計出與實際系統相差無幾的理想電路。而且,FPGA器件采用標準化結構,體積小、集成度高、功耗低、速度快,可無限次反復編程,因此,成為科研產品開發及其小型化的首選器件,其應用極為廣泛。

本文介紹了二次插補算法中的精插補器在FPGA中的實現方法,插補方法經過多年的發展已形成了眾多的門類,一般依據數控系統控制方式的不同將插補方法分為兩大類:基準脈沖插補和數據采樣插補。基準脈沖插補是用于開環控制系統的插補方法,它用理論直線上采用各種方法離散化得出的驅動信號直接驅動傳動裝置,沒有檢測實際加工軌跡誤差的反饋部件;數據采樣插補用于閉環數控系統中,在目前的檢測和運算技術還不能較快的實現插補與檢測同步修正的情況下,通常采用時間分割的思想,將整個插補過程分為粗插補和精插補兩個階段[1]。粗插補器在給精插補器發送下一段插補數據之前若干個周期從實時位置反饋單元得到實時位置數據,并依據此數據對下一段加工數據進行校正,從而使實際加工軌跡在控制器的監控下始終處于誤差允許范圍之內,這是一種二次插補方法。本文就是介紹了二次插補方法中精插補器的設計。最終將該精插補器運用于基于DSP控制平臺的伺服控制系統中。

1 伺服控制系統硬件設計

1.1 系統硬件組成

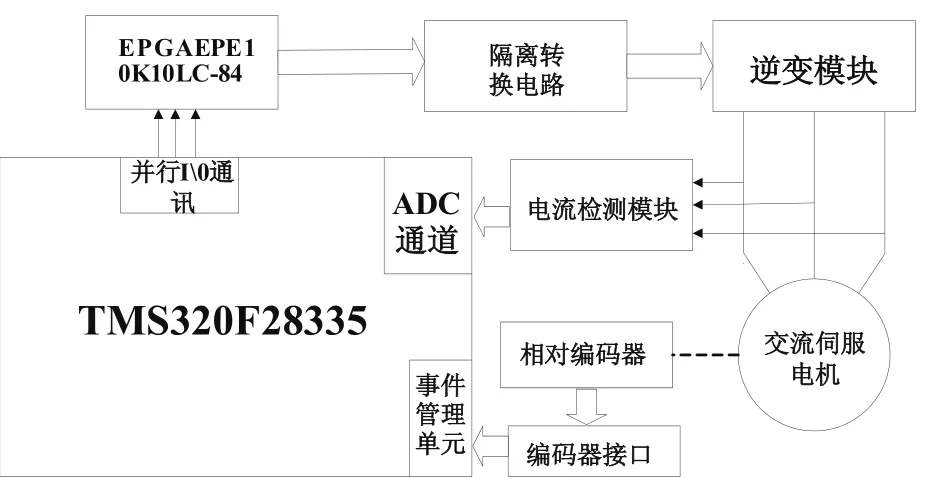

系統硬件框圖如圖1所示:

圖1 系統硬件框圖

該伺服系統中心控制電路采用TI公司的TMS32OF28335芯片。外設還包括6個捕獲單元,用以捕獲編碼信號和集成的3路正交編碼電路。另外本系統采用FPGA核心芯片EPE10K10LC-84來根據轉子位置信號通過邏輯關系輸出六路PWM 波[4]。

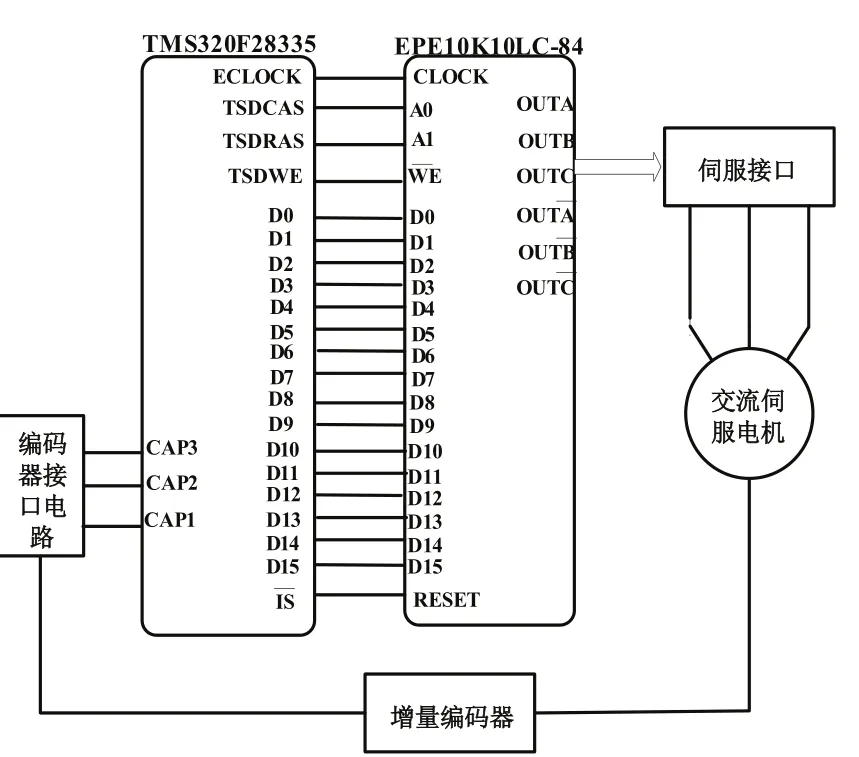

1.2 DSP與FPGA總線接口設計

本設計中TMS32OF28335與EPE10K10LC-84 的接口電路如圖2中所示。其中的工作頻率為32.47MHz,為保證DSP和FPGA在工作時序上的一致性,FPGA的時鐘源由DSP的ECLOCK腳提供,FPGA同步工作在32.47MHz 。DSP地址線TSDCAS(行選通) ~TSDRAS(列選通)、數據線D0~D15分別于FPGA的地址線A0~A1和數據線相連, IS為DSP與FPGA復位信號,WE為DSP的寫控制信號,當需要訪問 FPGA空間時,引腳輸出低電平選通 FPGA。CAP1~CAP3為DSP的事件管理模塊的輸入端口,用于接收編碼器的位置反饋信號[2]。

圖2 DSP與FPGA接口圖

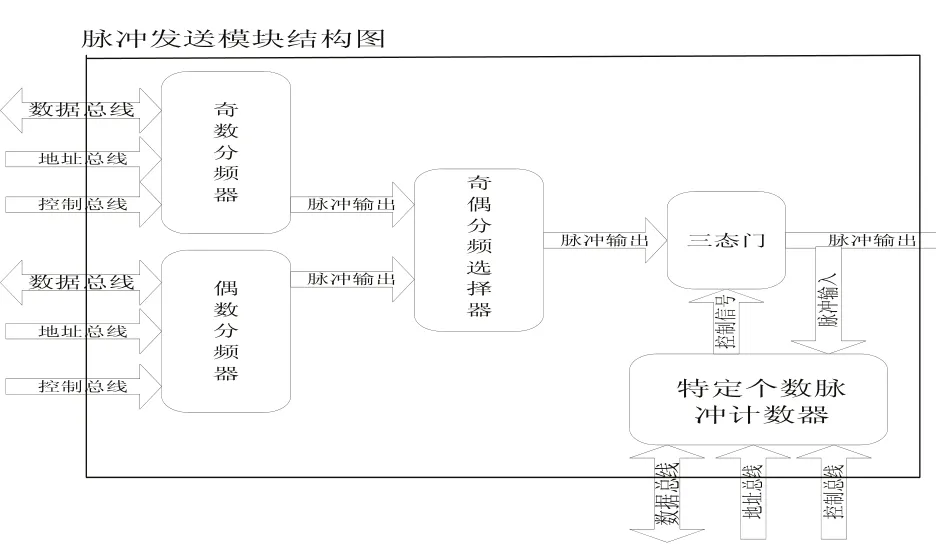

圖3 FPGA精插補器模塊框圖

2 FPGA精插補器內部組成及電路介紹

2.1 FPGA精插補器組成

對于FPGA精插補器模塊,其中的關鍵技術就是如何實現占空比為50%整數分頻和如何實現特定個數的脈沖發送。在本系統中整數分頻是由奇數和偶數兩種分頻器組成。而實現特定個數的脈沖發送時,系統設計了計數模塊,首先通過數據總線、地址總線和控制總線,把24位的二進制代表脈沖個數的數據分三次寫到計數模塊的三個8位的寄存器中,然后打開計數模塊的計數功能,讓其記錄從分頻器中發出的脈沖個數,當它記錄的脈沖個數和設定的脈沖個數相等時,就發出信號,停止分頻器繼續發送脈沖,從而達到實現特定個數脈沖的發送功能。FPGA精插補器整體模塊框圖如圖3所示。奇偶分頻選擇(J O X Z)和脈沖比較計數(MCBJJS),其內部電路及各模塊之間的接線電路如圖4所示。

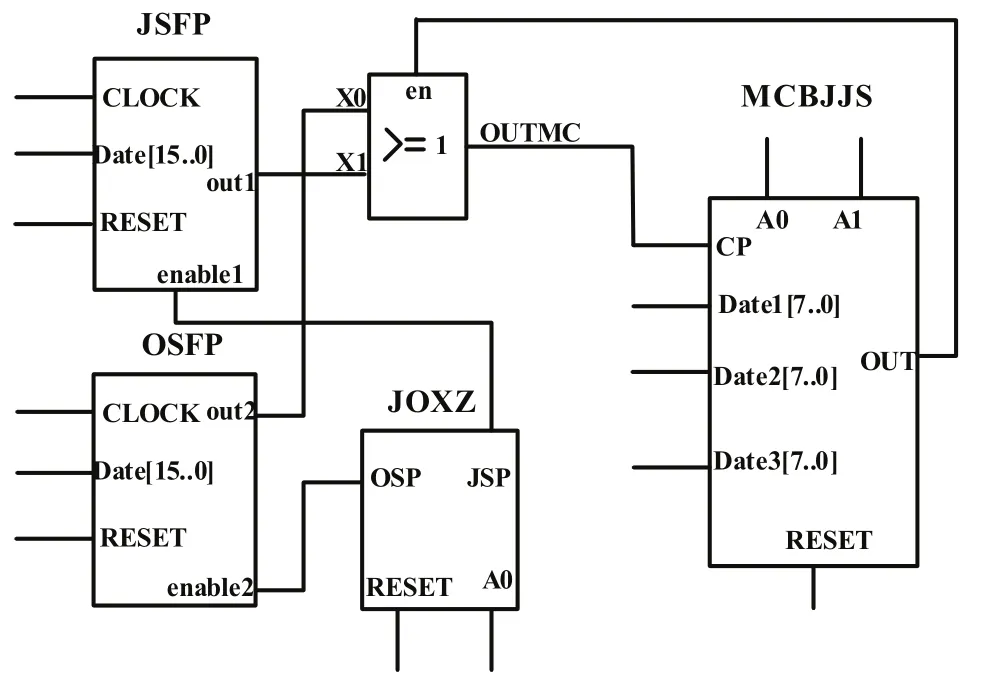

圖4 FPGA內部電路圖

圖中各模塊功能及引腳說明如下[3]:

奇數分頻器(JSFP)實現的是以1-65536中的奇數為參數的分頻功能,該功能模塊有一個時鐘輸入信號“Clock”管腳,用于接受外部基準時鐘信號,最大可以接受32.47MHz的時鐘信號,參數輸入通過“Date[15..0]”數據總線輸入,“Reset”管腳為復位管腳,每當一次參數更新時,都要使“Reset”管腳電平為“高”,才能使更新操作有效,但要注意的是:“Reset”管腳電平不能一直為“高”,復位以后要立刻變為“低”,否則輸出為“0”。“enable1”為選通使能腳,該信號由奇偶分頻選擇(JOXZ)寄存器提供。

偶數分頻器實現的是以2-65535中的偶數為參數的分頻功能其他引腳功能與奇數分頻器一致。

奇偶分頻選擇(JOXZ)的作用在于:當輸入的參數是奇數時,就打開奇數分頻器通道,讓系統輸出的脈沖來自于奇數分頻器,反之,如果

2.2 FPGA內部寄存器及電路設計

根據2.1所述,FPGA內部寄存器由四部分組成:奇數分頻(JSFP)、偶數分頻(OSFP)、系統輸入的分頻參數是偶數,就應該選擇偶數分頻器,使系統輸出的脈沖來自于偶數分頻器。該功能模塊如圖4總圖中的JOXZ模塊。圖中用兩個輸出信號分別控制奇數分頻器和偶數分頻通道。當“jfp” 管腳和“ofp”管腳的輸出電平組合為“10”時,選擇的是奇數分頻器;當為“01”時,選擇的是偶數分頻器;當無操作時,電平組合為“00”,即兩個分頻器都被關閉。值得注意的是:這兩個管腳的輸出電平組合沒有為“11”的狀態,即不可能同時打開兩個分頻器。而輸出狀態是由輸入的“A0”和“reset”兩個信號的狀態控制。當“A0”和“reset”的狀態為“10”時,即開奇數分頻器通道,當為“00”時,即開偶數分頻器,一旦“reset”的狀態變為“1”時,不管“A0”為什么狀態,則都要關閉兩個脈沖輸出通道。

脈沖比較計數(MCBJJS)的功能主要是完成對輸入脈沖的計數,當輸入脈沖個數于設定的個數相等時,輸出管腳“out”的電平由“1”變為“0”,從而控制三態門的使能端口“en”,是其處于截止狀態,這樣就使得輸出沒有脈沖信號了,即使系統停止向電機驅動器發脈沖。代表計數脈沖個數的參數輸入到內部三個八位的寄存器里,然后通過“reset”復位信號使該模塊重新以新的參數計數,“reset”復位信號有效時為“1”,復位后要使信號變為“0”,否則該模塊將不能進入計數狀態,被計數的脈沖從“cp”管腳輸入。

系統的脈沖輸出信號通過三態門的“OUTMC”提供給外部伺服接口。

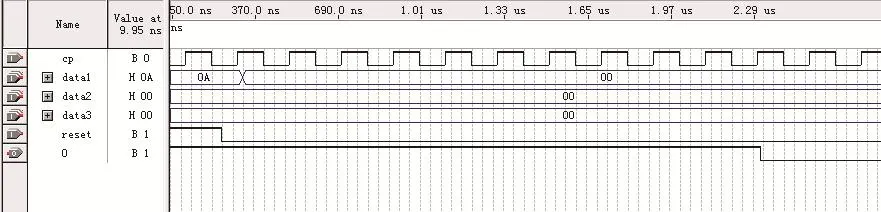

計數10個脈沖的仿真波形圖如圖5所示。

圖5 計數10個脈沖的仿真波形圖

3 反饋模塊實現

3.1 編碼器原理

在該伺服系統中增量式旋轉編碼器主要起到位置及速度反饋的作用。

增量式旋轉編碼器通過內部兩個光敏接受管轉化其角度碼盤的時序和相位關系,得到其角度碼盤角度位移量增加(正方向)或減少(負方向)。在接合數字電路特別是單片機后,增量式旋轉編碼器在角度測量和角速度測量較絕對式旋轉編碼器更具有廉價和簡易的優勢。

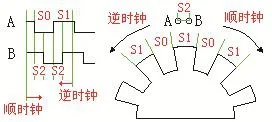

增量式旋轉編碼器工作原理如圖6所示:

圖6 旋轉編碼器工作原理圖

其中A、B兩點對應兩個光敏接受管,A、B兩點間距為S2 ,角度碼盤的光柵間距分別為S0和S1[4]。

當角度碼盤以某個速度勻速轉動時,那么可知輸出波形圖中的S0:S1:S2比值與實際圖的S0:S1:S2比值相同,同理角度碼盤以其他的速度勻速轉動時,輸出波形圖中的S0:S1:S2比值與實際圖的S0:S1:S2比值仍相同。如果角度碼盤做變速運動,把它看成為多個運動周期(在下面定義)的組合,那么每個運動周期中輸出波形圖中的S0:S1:S2比值與實際圖的S0:S1:S2比值仍相同。通過輸出波形圖可知每個運動周期的時序,如表1所示。

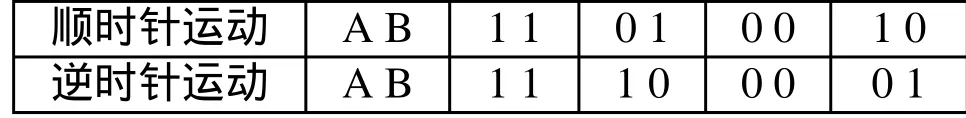

表1 運動周期時序表

我們把當前的A、B輸出值保存起來,與下一個A、B輸出值做比較,就可以輕易的得出角度碼盤的運動方向。如果光柵格S0等于S1時,也就是S0和S1弧度夾角相同,且S2等于S0的1/2,那么可得到此次角度碼盤運動位移角度為S0弧度夾角的1/2,除以所消毫的時間,就得到此次角度碼盤運動位移角速度。S0等于S1時,且S2等于S0的1/2時,1/4個運動周期就可以得到運動方向位和位移角度,如果S0不等于S1,S2不等于S0的1/2,那么要1個運動周期才可以得到運動方向位和位移角度了。

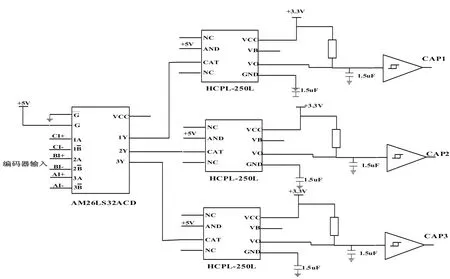

3.2 編碼器脈沖采集的差分電路設計

由編碼器輸出的六路差分信號,經過差分信號處理芯片AM26LS32ACD及其處理電路,轉化為DSP芯片能夠接受的捕獲信號,該差分信號處理電路如圖7所示[5]。

其中AI+、AI-、BI+、BI-、CI+CI-為編碼器六路輸入信號,CAP1、CAP2、CAP3為提供給DSP的捕捉信號。

4 VHDL語言實現

在該系統中,主CPU為DSP控制平臺,主要完成數字信號的處理運算,它把位置、方向和速度信號通過數據總線寫入FPGA(脈沖發送模塊)內的相關寄存器,然后發送啟動信號,這樣脈沖發送模塊會自動完成電動機的定位和調速,達到精確的位置和速度控制。該系統用硬件描述語言(VHDL)編寫了精插補器中的各個功能模塊,并進行了功能和時序仿真,然后把代碼通過專用下載線下載到電路板上的FPGA芯片中進行調試。以下為奇偶分頻選擇器的VHDL語言實現。

圖7 編碼器差分信號處理電路

5 結束語

FPGA是一種非常有前途的新技術,很適合于科研工作中的樣機及新產品的開發應用。本文主要是研究二次插補算法中的精插補器在FPGA中的實現方法。綜合仿真和實際測試表明,設計的基于DSP系統的FPGA精插補器能比較靈活方便的控制伺服電機的速度和方向,達到了設計的要求。

[1] Roche,Stephan.Implement a stepper-motor driver in a CPLDE[J].EDN,2007(2):90.

[2] 劉昌華.數字邏輯EDA設計與實踐—— MAX+PLUS與Quartus[M].北京:國防工業出版社.2006.

[3] 王金明.數字系統設計與Verilog HDL[M].北京:電子工業出版社,2006.

[4] 曹東杰,韓峰,任云燕.單片機控制步進電機按S形曲線升降頻設計[J].彈箭與制導學報,2006,26.(2):157- 169.

[5] 孫佐.基于8XC196單片機的EPA和PTS實現伺服電機控制[J].控制與檢測.2005.