基于A結E構S 共享和多級流水線的加密算法的研究

王 群

(青島科技大學信息學院 山東 青島 266061)

2000年10月,美國國家標準技術局(NIST)選擇了兩位比利時研究者Daemen和Rijmen提出的Rijndael算法,即AES(高級加密標準)。它具有128bits的分組長度,三種可選的密鑰長度,即128bits、196bits和 256bits。

AES可以抵抗所有設計中已知的攻擊方法,具有較高的安全強度。文中闡述了AES算法的原理,并對其加解密模塊進行優化,提出了一種基于結構共享和多級流水線的AES算法實現方案,并重點闡述了實現過程。

1 AES算法介紹

AES算法是一種迭代分組算法,采用128bits的分組長度,三種可選密鑰長度128bits,192bits和256bits。對于不同的密鑰長度,所需的加解密輪數不同。本文主要討論分組長度和密鑰長度128bits的情況。

整個加密過程包括11輪迭代。其中Round0只有Add Round Key操作。Round1-Round9具有完全相同的操作, 依次經過 SubBytes、Shift Rows、Mix Columns和Add Round Key四種操作。Round10只包括 SubBytes、Shift Rows和 Add Round Key 三種操作。解密過程是加密過程的逆過程。關于AES算法的詳細描述見參考文獻[1]。

2 加解密模塊的結構共享

2.1 字節變換(SubBytes)

當前實現字節變化的方法有兩種:一是有限域運算的方法;一是查找表的方法。前者運算復雜,后者容易實現,并且運行速度更快,但是硬件開銷較大。考慮到可以利用FPGA自帶的Block RAM資源,在設計中采用了查找表的實現方式。

如果將用于加密的Sbox表和用于解密的Inverse Sbox表同時存放在FPGA的Block RAM中,會造成RAM資源的大量消耗。為降低硬件資源的消耗,設計中采用重新配置的方法。加密時一次性加載16個Sbox表,而在解密時,對存放這些Sbox表的RAM重新寫入Inverse Sbox表的數據。

2.2 行移位(Shift Rows)

本文采用128bits并行算法,行移位變換可按照移位的方向和字節數連線,幾乎不占用硬件資源和產生延時,然后通過選通器選擇正向或逆向行移位變換。

2.3 列混合(Mix Columns)/逆列混合(InvMix Columns)

根據算法原理,列混合變換就是輸入狀態矩陣與一個系數矩陣相乘。

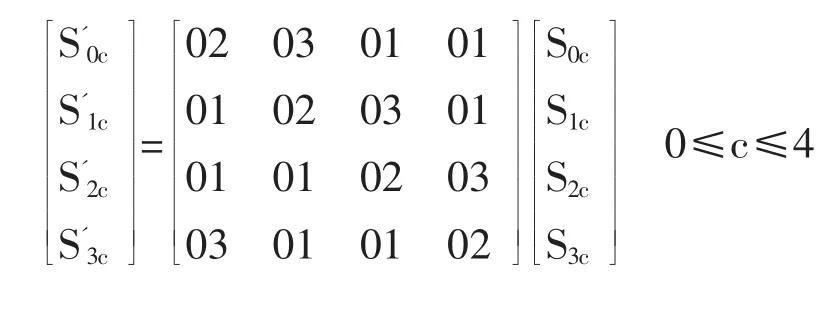

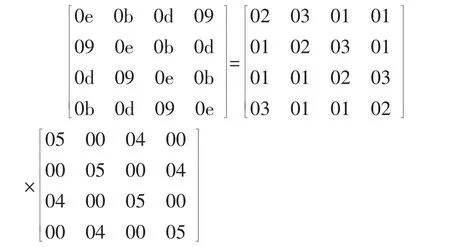

列混合變換表示為:

逆列混合變換表示為:

逆列混合變換的系數矩陣與列混合變換的系數矩陣存在如下關系:

因此,在實現逆列混合變換時,只需在列混合變換之前先執行個邏輯電路。將列混合變換和逆列混合變換進行整合,使得列混合電路可以復用于解密過程中,并由選擇器來實現加密/解密操作,實現了硬件資源的共享。

3 流水線結構的設計

3.1 AES算法實現流水線的可行性

第一,AES算法加解密過程的核心是10次輪操作,前一輪操作的輸出即為下一輪操作的輸入。第二,AES算法每次對一個128bits的數據塊進行編碼,當采用ECB工作模式時,前后進行編碼的數據塊間不存在相關性。由于上述特點,AES算法完全能夠以流水線的形式實現。

3.2 兩類典型的流水線結構

AES算法的流水線結構分為輪內流水線結構和輪間流水線結構兩種。輪內流水線結構就是把在一個時鐘周期內欲完成的運算劃分為若干子運算,采用寄存器輸出模式。輪間流水線結構就是在相鄰的兩輪加解密模塊之間加入寄存器,每個時鐘周期各加解密模塊都有一次輸出,從而實現輪間流水線設計。

輪內流水線結構被很多人討論并使用,這種結構既可縮短延時路徑,提高時鐘頻率,又可使各子運算同時進行。但是這種結構增加了控制的復雜度同時占用大量的存儲單元,對于FPGA實現來說將是很大的負擔。另一方面,這種結構雖然能提高仿真頻率,但是系統吞吐量并沒有明顯的提高。因此,本設計采用輪間流水線結構。

3.3 AES算法的5級流水線設計

傳統的AES算法流水線為10級流水線結構或2級流水線結構。這兩種設計結構都存在弊端。10級流水線結構能夠最大限度的利用流水線技術,提高系統的運行速度,但是要耗用大量FPGA的邏輯單元和存儲單元;而2級流水線結構設計,雖然占用FPGA資源較少,但是沒有有效的利用好流水線技術。本文提出的5級流水線結構是上述兩種設計結構的折中方案,能夠最大限度的利用FPGA資源來實現流水線設計,從而提高系統運行速度。

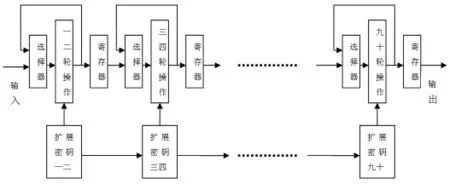

具體實現為將原來的0-10輪循環迭代結構進行分解。第0輪只是實現了Add Round Key操作,可以使用單獨的“異或電路”加以實現。將剩下的1-10輪通過2輪一組,組內循環的方式設計為5級流水線結構。如圖1所示。

圖1 AES算法5級流水線結構

由于1-9輪的運算模式與第10輪存在不同,因此將第9輪和第10輪作為一組在控制上要使用不同的控制信號。通過狀態機來對兩輪的控制信號賦不同的值。而1-8輪的的運算模式是相同的,即其控制信號也是相同的。因此前4組流水線可以使用一組固定的控制值。

本設計是組內循環與輪間流水相結合的模式,必須要解決好輸入的問題,即要協調好來自上一級流水線的輸入數據與本級流水線循環反饋的數據,使系統正常工作。這里通過設計一個2選1(MUX2_1)選擇器來實現。選擇器的使能信號也是由狀態機來實現。

輪密鑰的匹配輸入問題。由于每級流水線包括兩次加/解密的運算,而每次加/解密運算所需的輪密鑰各不相同。要實現此操作就必須為每級流水線設置一個寄存器堆。寄存器堆中存放兩次加/解密運算所需的不同輪密鑰。對輪密鑰的選擇也是由狀態機來實現。

4 結束語

本文提出了一種基于結構共享和多級流水線的AES算法實現方案。字節變換采用可重構設計,用同一組RAM資源在加解密時,分別加載Sbox表數據和Inverse Sbox表數據,節約了RAM資源。通過在列混合變換之前執行個邏輯電路(PreInvmix),來實現逆列混合變換。從而實現了逆列混合變換與列混合變換的結構共享。采用5級流水線結構設計,實現了芯片面積的節省和系統工作頻率的提高。

[1]Federal Information Processing Standard (FIPS)for the Advanced Encryption Standard[J].FIPS-197.November 26,2001.

[2]武玉華,李艷俊,周玉坤.基于FPGA的AES_128密碼算法實現研究[J].微計算機信息,2007(2).

[3]李雪梅,路而紅,歐海文.AES算法的快速硬件設計與實現[J].電子技術應用,2006(5).

[4]吳曉成,高琳.AES IP Core的一種高速流水線實現方法[C].西安電子科技大學學術年會,2007.