基于FPGA的數字邏輯新型實驗方法研究

徐尚中,李 靖

(周口師范學院 計算機科學與技術學院,河南 周口 466001)

基于FPGA的數字邏輯新型實驗方法研究

徐尚中,李 靖

(周口師范學院 計算機科學與技術學院,河南 周口 466001)

針對《數字邏輯》實驗教學目前存在的問題,對《數字邏輯》課程的實驗方法進行了分析和探討,提出了一種基于FPGA的新型實驗方法.該方法不僅具有很大的靈活性與可重構性,而且能提高實驗的準確性和成功率,具有很大的發展空間.

實驗方法;FPGA;數字邏輯

1 引言

《數字邏輯》是計算機、自動化和電子工程等專業的專業基礎課程之一,具有很強的工程實踐性,是深入了解計算機內核的一門最關鍵的基礎課程.作為課堂所授理論知識的必要的補充,《數字邏輯》課程實驗是學生獲得所學知識和進行能力訓練的重要途徑,對學生能否真正掌握所學的課程內容以及能否靈活運用所學知識去解決實際問題起著決定性的作用.

2 《數字邏輯》課程實驗的現狀分析

目前,在地方師范院校《數字邏輯》實驗課程的開設主要有兩種情況:一是部分高校雖然開設了《數字邏輯》課程,但由于種種原因并不開設相應的實驗課程,即純粹的理論講解;二是絕大部分高校開設了《數字邏輯》實驗課程,但實驗設施和實驗方法相對落后,實驗效果不佳.在具體的實驗方法上,也有兩種情況:

2.1 基于硬件的傳統實驗方法

當前許多高校在進行《數字邏輯》實驗教學時,還是沿用傳統的實驗箱來實現組合邏輯實驗和時序邏輯實驗.傳統的實驗方法都是在集成電路等各組成部件相對固定的情況下進行的,如基本的組合邏輯器件:與、或、非門、編碼器、譯碼器、觸發器、寄存器、計數器等,通過連線,學生用這些器件可以完成一些基本的功能性驗證或簡單的設計性實驗.其優點是:通過這些看得見摸得著的實物儀器裝置,學生可以較容易的獲得感性認識,從而將抽象的理論變成直觀的現實,這種傳統實驗室為學生提供了真實的實驗環境,使學生身臨其境,理論上來講教學效果應當非常好.但是這種實驗方法局限性很大.首先,學生的設計很難突破實驗箱的限制,難以實現一些綜合性、設計性實驗.其次,在傳統實驗室中,由于實驗設備較為復雜,實驗環境等客觀因素對實驗有很大的影響,其中有些問題是由學生操作不當引起的,有些問題可能是當時的設備狀態出了問題,如不能及時檢查糾正,過后就很難確定問題出現的原因,這樣往往使學生無法找到問題的本質,嚴重影響學生對實驗的理解.另外,有些實驗需要學生插接的連線可能比較多,在實驗過程中,只要有一個連線或元器件出現接觸不良現象就會影響到整個實驗的完成情況,實驗的成功率很低,也會影響到學生的學習興趣.所以,學生盡管花了許多的時間去做實驗,卻收獲甚微.

2.2 基于軟件的虛擬實驗方法

另一種常用的方法是采用所謂的“虛擬實驗室[1]”,如 EWB、Multisim、QuartusⅡ等都是專門用于電子電路仿真的“虛擬電子工作平臺”,它以軟件為基礎,軟件即為儀器,以計算機為操作平臺,采用一定的數學模型和仿真算法,在輸入即將實驗的電路模型及元器件參數后,軟件會依據元器件的特性對電路模型進行仿真,虛擬儀器、儀表可將電路測試點的波形和數據顯示出來,能方便地應用在實驗教學中,有效地降低實驗成本,提高實驗效率.同時,“虛擬實驗室”提供了傳統實驗室無法相比的大量的虛擬元器件庫,提供了修改電路設計的靈活性、提供了實驗室在數量、質量上難以相比的虛擬儀器、儀表,使得學生在實驗中能夠打破傳統實驗方法的束縛,自主的從事一些綜合性、創新性的實驗設計,大大提高學生的學習興趣[2,3].虛擬實驗室有效的彌補了傳統實驗室存在的不足,在教育領域得到了越來越廣泛的應用.目前,國內許多高校都根據自身需求建立了虛擬實驗室,取得了很好的教學效果.但是虛擬實驗方法也有其自身的缺點.首先,虛擬實驗方法采用虛擬環境,虛擬設備與真實的實驗設備還有一定的差距,無法使學生掌握對真實元器件進行識別和引腳功能判斷的方法,無法掌握實際電路元器件的安裝與連接的方法以及真實儀器、儀表的使用方法等.其次,實際電路中各元器件之間及連線之間的相互干擾問題也是虛擬實驗設備所無法表達的.因此,這種實驗方法不能培養學生在元器件識別、電路連接,電路調試、儀器操作等方面的實踐動手能力[4].

通過對傳統實驗方法和虛擬實驗方法進行比較,可以看出,二者各有優缺點,只有將二者結合起來,才能為學習者營造一個不受時間、地點、實驗設備約束的實驗環境,使學生既可以感受到逼真的實驗過程,提高實驗數據的準確性,又能節約學校專用實驗室的投入,提高實驗的成功率.

3 基于VHDL的新型實驗方法

EDA技術的快速發展使數字系統的設計發生了革命性的變化[5],將這一技術運用到《數字邏輯》實驗中,即可構建出基于計算機平臺“虛實結合”的《數字邏輯》實驗系統.

3.1 基于VHDL的新型實驗的設計流程

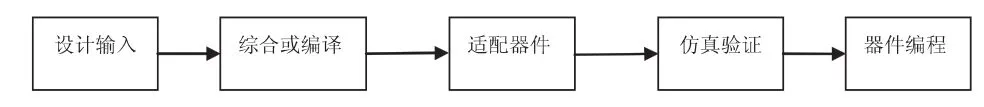

具體來講,基于EDA技術的《數字邏輯》實驗系統就是選用高性能的FPGA芯片作為硬件平臺,采用VHDL語言在QuartusⅡ環境中設計實驗電路模型并進行仿真[6,7],即首先運用虛擬實驗的方法在計算機軟件平臺上設計出實驗電路模型和進行初步的軟件仿真,確認無誤后再將設計好的相應程序經數據線下載到實驗系統中的實驗電路板上進行實際驗證.學生在實驗過程中可以節省出大量的接線時間,把實驗的重點放在電路模型的設計、仿真和驗證上,從而培養學生的分析設計能力和實踐操作能力.其設計流程如圖1所示.

圖1 FPGA設計器件的一般流程

圖1中,設計輸入是將設計者所要設計的電路模型以VHDL代碼形式或以原理圖的形式表達出來.綜合是將VHDL語言或原理圖等設計輸入進行編譯、優化、轉換和綜合,生成門級電路.適配是將邏輯綜合生成的網表文件映射到某一具體的器件.仿真驗證則是驗證設計輸入邏輯功能的正確性.器件編程是指設計輸入編譯成功后,設計者使用器件編程器將程序下載到實際器件的過程.

以帶使能端的四位二進制計數器為例,要完成一個計數器實驗,首先需要編寫計數器VHDL程序來作為實驗的設計輸入,其核心代碼如下:

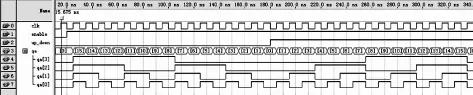

代碼中enable為使能控制端,高電平時有效.cnt為計數變量,每當clk來一個上升沿時且使能端有效時進行一次計數.將計數器VHDL代碼所形成的.vhd文件作為QuartusⅡ的設計輸入進行編譯,檢查無誤后對計數器進行時序仿真,得到計數器輸出波形如圖2所示.

圖2 QuartusⅡ環境下計數器波形仿真

由圖2可知,計數器在軟件環境下通過編譯、仿真,輸出波形完全符合實驗設計的要求,說明在虛擬環境下所做的實驗設計是完全正確的.下面要做的工作就是綁定FPGA芯片引腳,將程序下載到FPGA芯片中,進行實驗的實際驗證.由此可以看出,這種實驗方法真正做到了實驗的虛實結合,它既能提高實驗的成功率,又能觀察實驗的實際運行效果.

3.2 新型實驗設計的靈活性與可重構性

與傳統的實驗方法相比,基于VHDL虛實結合的實驗方法的優點還體現在它的靈活性與可重構性上.采用傳統的實驗方法,一旦所設計的實驗出現了問題,設計者必須重新對實驗電路檢查一遍,實驗電路越復雜,連線也會越多,出現的問題也越多.有時辛辛苦苦連了一兩個小時候的線,卻不到實驗結果,有時也會有一些粗心的同學出現燒壞芯片的事情.但是,基于VHDL的新型實驗方法卻不會有這些現象發生.

3.2.1 新型實驗設計的靈活性.

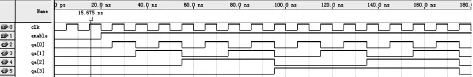

在VHDL語言中,電路模型都是通過程序來編寫的.實驗電路的正確與否可以在軟件環境中進行檢測,當出現問題時,只需修改VHDL代碼就行了.另外,由于實驗系統的硬件平臺采用的是可編程的FPGA芯片,掉電后設計好的電路就不復存在了,所以在同一個系統下,可做多次實驗、多個實驗.編寫不同的程序,即可實現不同的功能電路.比如:對帶有使能端的四位二進制計數器進行適當的修改,即可變成一個加/減計數器電路.VHDL關鍵代碼如下:

上述代碼中加入了一個加/減計數控制端(up_down),為高電平時進行加法計數,為低電平時進行減法計數.可得到其仿真波形如圖3所示.

圖3 QuartusⅡ環境下加減計數器波形仿真

此外,新型實驗設計的靈活性還體現在QuartusⅡ環境下設計輸入的多樣化.QuartusⅡ軟件支持模塊/原理圖輸入、文本輸入、第三方EDA工具輸入等多種輸入方式.因此,在進行實驗設計時,即使學生不懂得VHDL語言,也能通過原理圖的輸入方式設計出相應的實驗電路.

3.2.2 新型實驗設計的可重構性

FPGA是英文Field Programmable Gate Array的縮寫,即現場可編程門陣列,它是作為專用集成電路 ASIC(Application Specific Integrated Circuit)領域中的一種半定制電路而出現的,FPGA能夠完成任何數字邏輯器件的功能,上至高性能的CPU,下至簡單的74系列電路,都可以用FPGA來實現.FPGA如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法,或是硬件描述語言(VHDL)自由地設計一個數字系統.

基于FPGA的電路設計采取的是一種自頂向下的設計方式[8],即按照數字系統的功能描述,把系統劃分為若干個功能模塊,然后再把每個模塊劃分為不同層次,從高層次到低層次逐步細化.把這種思想應用到《數字邏輯》實驗中,可以大大簡化實驗設計的復雜程度.采用模塊化設計的方法,把每個實驗課題內容逐步細化為若干個具體的模塊,每個模塊具體為一個或若干個程序,能夠完成一定的功能.同時若干個模塊又可以組合成一個大的模塊,即可實現電路設計的可重構.比如:本次設計好的實驗電路可以作為一個模塊保存下來,當下次實驗設計剛好需要用到這個模塊的時候,可以隨時取過來作為新的實驗設計的一部分,這樣做的實驗越多,積累的模塊也越多,學生做起實驗也就越方便.

4 結束語

實驗教學是培養學生實踐和創新能力的一個重要環節.作為傳統實驗方法和虛擬實驗方法的給合體,基于FPGA的新型實驗方法具有很大的發展前景,代表了未來的發展方向.然而,這種先進的實驗方式并沒有在中國大多數著名高校廣泛使用,由此可見,實驗教學在國內的創新研究和推廣工作無疑任重而道遠的.

〔1〕汪航,孫琪.教學型虛擬實驗室的應用研究[J].現代遠距離教育,2010(4).

〔2〕劉輝,曾松.計算機類課程虛實結合的實驗構建[J].計算機教育,2011(10)

〔3〕湯書森,李蜀嫻,饒增仁.仿真技術在數字邏輯電路實驗教學中的應用與實踐[J].高校實驗室工作研究,2012(1).

〔4〕徐尚中,崔仲遠.高校《數字邏輯》課程教學改革的思考與探討[J].現代計算機(專業版),2010(9).

〔5〕江晉劍.基于FPGA的可重構性數字邏輯實驗方法[J].安慶師范學院學報(自然科學版),2011(4).

〔6〕羅苑堂.CPLD/FPGA常用模塊與綜合系統設計實例精講[M].北京:電子工業出版社,2007.

〔7〕劉福奇.基于VHDL的 FPGA和NoisⅡ實例精煉[M].北京:北京航空航天大學出版社,2011.

〔8〕鄭亞民,董曉舟.可編程邏輯器件開發軟件QuartusⅡ[M].北京:國防工業出版社,2006.

TP302.2

A

1673-260X(2012)09-0020-03

河南省教育廳自然科學項目(No.2010B520035),周口師范學院校級教改項目(No.J2010086)