SOC 中嵌入式存儲器陰影邏輯的可測性設計

施文龍,林 偉

(福州大學福建省微電子集成電路重點實驗室,福州350002)

集成電路已經發展到了系統芯片SOC(System On Chip)時代,芯片集成度越來越高,結構越來越復雜,對集成電路測試又是芯片設計不可或缺的重要環節,測試的可行性、有效性以及測試功耗,極大地影響了芯片設計的成本與上市時間。嵌入式存儲器是芯片設計的關鍵部分,是系統芯片中集成密度最高的器件,同時又是對制造過程中存在的缺陷最敏感的器件之一。各種類型的存儲器在當前的SOC 設計中已經被廣泛應用,占用了SOC 系統大部分面積[1]。針對SOC 芯片設計中存在著的嵌入式存儲器模塊,傳統的固定故障模型不適合用于對存儲器模塊進行測試。因此,對于使用自動測試圖形生成ATPG(Automatic Test Pattern Generation)工具用固定故障模型進行測試時,通常把嵌入式存儲器模塊當作“黑盒子(black box)”處理[2]。在黑盒子模型中,所有的輸入都被禁止,所有的輸出都被置為未知狀態X,于是,存儲器模塊的輸入引腳前與輸出引腳后就存在著兩塊不可觀察或不可控制的組合邏輯,這部分不可測試的組合邏輯就稱為存儲器陰影邏輯。由于存儲器模塊被簡化成只含有輸入引腳與輸出引腳的無功能黑盒子,ATPG 工具產生的測試圖形無法順利通過該模塊,陰影邏輯的故障不能被傳遞,所以無法被檢測出來,ATPG 工具只能完成對掃描鏈路中的寄存器單元以及不包含陰影邏輯的外圍組合邏輯電路進行控制和觀察測試。當芯片中集成了更多、更大的嵌入式存儲器模塊,大量的不可測試的陰影邏輯會在很大程度上影響測試覆蓋率,造成故障覆蓋率低于設計要求。因此,陰影邏輯的影響不能忽視。

覆蓋率的提高主要需要提高改善設計的測試可觀測性和測試可控制性[3]。可測性設計DFT(Design For Test)就是為了確保復雜設計能夠得到全面徹底地測試而提出的。其思想是在設計的初期就考慮芯片的測試問題,通過增加測試邏輯完善設計,把難測或者不可測故障轉變為易測、可測的故障,爭取在芯片設計前端就解決棘手的測試問題。可測性設計技術有多種結構,目前應用最廣泛的可以有效提高芯片可測性的實現方法是基于掃描結構的可測性設計。掃描設計具有結構簡單、對芯片的面積影響較小、測試覆蓋率高以及可以與EDA 工具緊密結合等特點[4]。

1 基于掃描結構的可測性設計原理

1.1 設計原理

在集成電路設計中都含有大量的時序電路,時序電路的測試生成相當復雜,生成的測試圖形非常多,因此測試施加時間也就相應長,而且很難對電路內部節點設置邏輯值,電路的內部狀態則難以觀察,測試起來非常復雜。掃描設計的提出,為時序電路的測試提供了可能[5],其基本原理是將電路中的時序元件替換成具有掃描能力的掃描寄存器,然后將它們連接起來形成掃描鏈,為時序元件增加了控制點和觀察點,從而可以改善電路的可控性和可觀察性[6]。

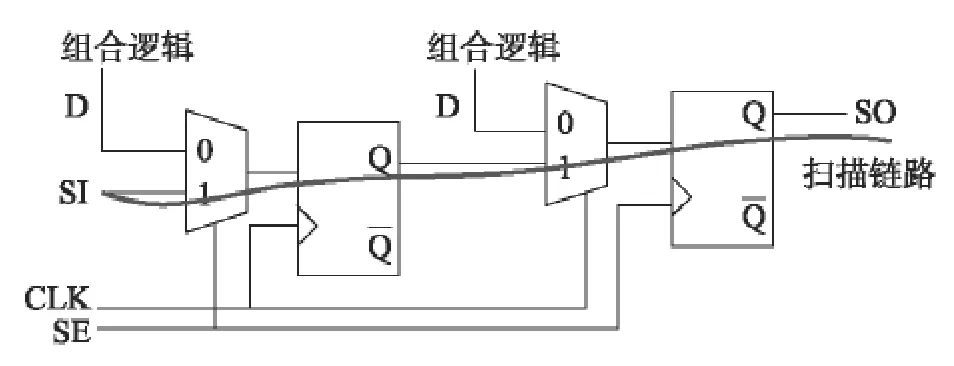

掃描設計的具體實現方式為:每一個觸發器前面都接入一個兩輸入的多路選擇器,其中一個輸入接到前一個觸發器的輸出,另一個輸入接到原始設計中所接的信號,即把普通寄存器轉化為掃描寄存器[7]。這些修改的時序元件一個接一個串在一起形成移位寄存器,所有掃描寄存器的控制線都連接到一起,稱為掃描鏈或掃描路徑[8-9],這些時序元件連到掃描鏈中就形成掃描可控和掃描可觀察。如圖1 所示,SI 表示掃描輸入,SE 表示掃描使能控制線,CLK 表示時鐘輸入端口,D 端口表示正常的數據輸入端口,第一個寄存器的輸出Q 接到第二個掃描寄存器的多路選擇器的輸入,最后一個寄存器的輸出標記為掃描輸出SO,形成掃描鏈路。當一個時序元件通過串行移入一個特定的邏輯值(0 或1)可以被設置成一個已知狀態,那么這個時序元件是掃描可控的,ATPG 工具就把這個掃描可控元件作為偽原始輸入。當一個時序元件的狀態通過串行移出數據端口可以被觀察到,那么這個時序元件是掃描可觀察的,ATPG 工具就把這個掃描可觀察元件作為設計的偽原始輸出。通過偽原始輸入,掃描路徑能夠實現對所有組合模塊的輸入控制;通過偽原始輸出,掃描路徑能夠把所有組合模塊的邏輯值傳遞到輸出可觀察。

圖1 掃描設計結構圖

掃描測試分為3 個步驟,首先是掃描移入(shift in)操作,將設計中的時序元件設置為期望的目標值,這個過程需要與內部最長掃描鏈長度相同的時鐘數,掃描使能SE=1,電路工作在掃描移位測試狀態。然后是給電路施加測試向量并捕獲(Capture)響應,此時掃描使能SE=0,電路工作在正常的功能狀態。最后對捕獲的組合邏輯部分的響應執行掃描移出(Shift out)操作,掃描使能SE=1,電路工作在掃描移位測試狀態。

掃描設計的顯著優點就是把設計中的普通時序元件替換為掃描元件,從而把對時序邏輯電路的測試轉變成對組合邏輯電路的測試,使得測試圖形生成變得十分容易,處于掃描路徑上的觸發器不僅可以串行地移入所需要設置的電路狀態,也可以把電路狀態串行地移出去,最后實現對故障點的可控可觀察。

1.2 存儲器陰影邏輯DFT 方案

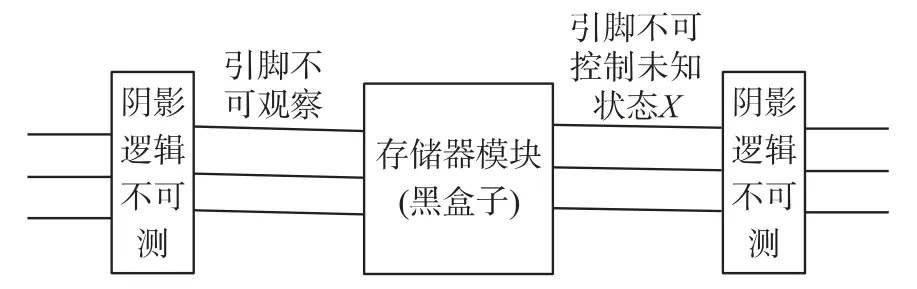

由于芯片設計中的嵌入式存儲器模塊在掃描插入時將作為黑盒子處理,因此在這些模塊周圍將為出現無法檢測和控制的陰影邏輯,其結構圖如圖2 所示。

圖2 嵌入式存儲器陰影邏輯結構圖

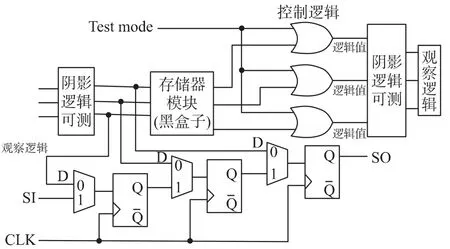

圖3 陰影邏輯測試結構圖

針對設計中出現的存儲器陰影邏輯不可測試情況,通過適當增加測試點的方式,使原來不可控和不可測的邏輯變化反映到掃描鏈寄存器上,使其變得間接可控和可觀測,從而提高整個系統芯片的測試覆蓋率。如圖3 所示,在存儲器數據和地址引腳周圍構造觀察邏輯,觀察邏輯為存儲器輸入引腳周圍的陰影組合邏輯提供了一條通路,使得陰影邏輯的固定故障可以傳遞到觀察點上;在存儲器輸出引腳周圍構造控制邏輯電路,控制邏輯為存儲器輸出引腳周圍的陰影邏輯提供了可控信號,使得輸出引腳后的陰影邏輯有了具體邏輯值,不再是原先的X 狀態,從而實現了故障傳遞。在測試模式下,ATPG 工具很容易就可以把陰影邏輯故障傳輸到掃描鏈觀測點寄存器上。

2 在數字信息安全芯片設計中的應用

2.1 設計過程

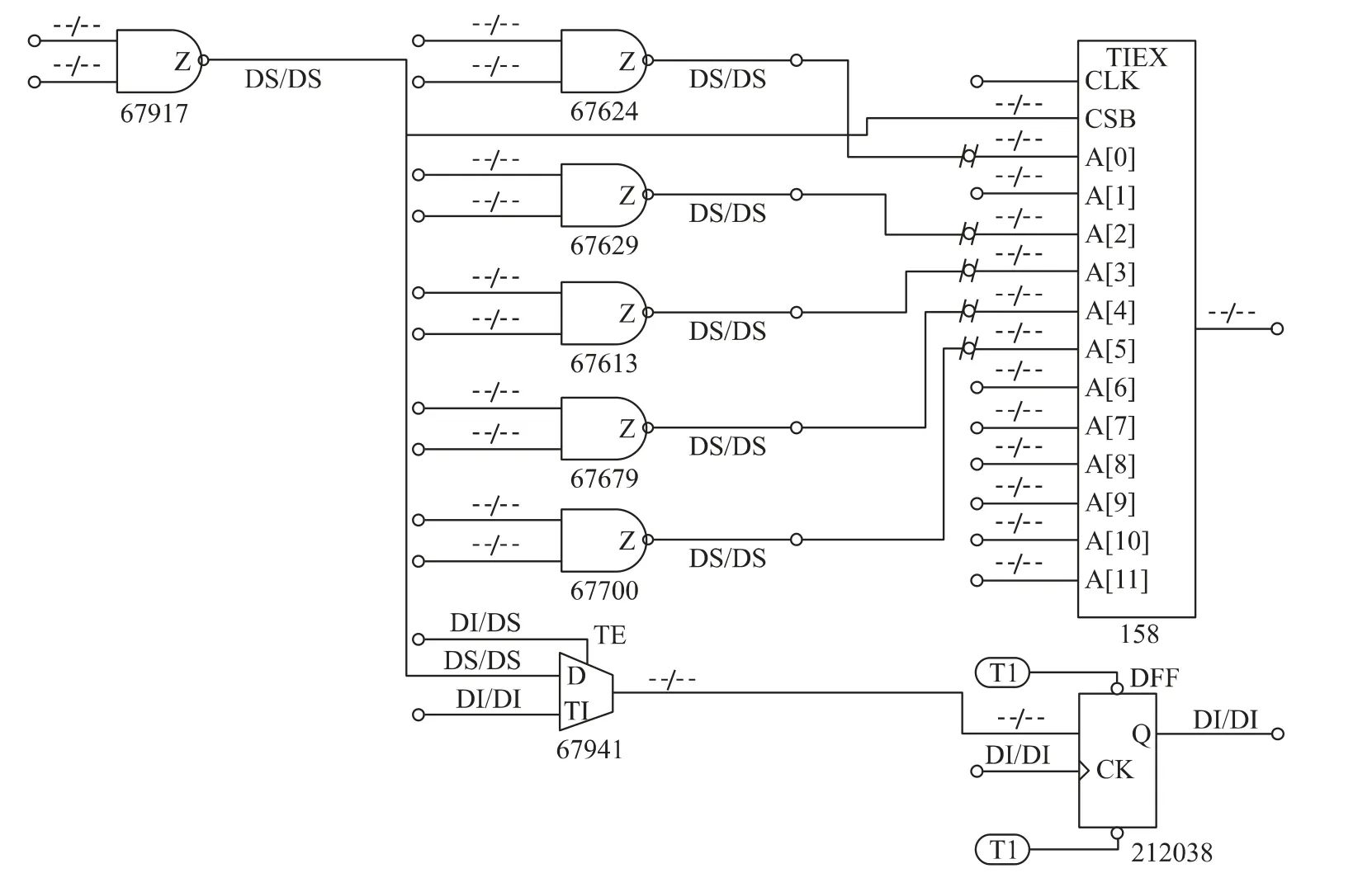

在本次設計的數字信息安全芯片中,以ROM模塊為例,該模塊的輸入引腳有CLK,CSB,A[11:0],輸出引腳D[31:0]。其陰影邏輯實現可測的具體實現方式:針對該ROM 存儲器輸入引腳前的陰影邏輯,在輸入管腳添加一個帶有選擇端的寄存器,當控制信號TE 為0 時,電路工作在正常邏輯功能狀態下,功能邏輯傳遞正常的輸入數值,當控制信號TE 為1 時,電路工作在掃描測試模式下,通過在測試鏈預置相應的值進行移位操作過程,之后給電路施加激勵向量并實現捕獲,最后移到掃描輸出端進行觀測。在這種方式下,存儲器前的陰影邏輯的故障完全得到測試,ATPG 工具測試報告如圖4 所示。

圖4 ROM 存儲器前添加觀察寄存器后ATPG 報告圖

圖4中DS 與DI 分別為Detected by Simulation 和Detected by Implication 的縮寫,表示該點可測試。DS/DS 表示固定故障0 和固定故障1 都可測。

針對該ROM 存儲器輸出引腳后的電路邏輯,使用或門與測試模式信號Testmode 進行或操作,當測試模式信號Testmode=0 時,電路處在正常功能狀態,當測試模式信號Testmode=1 時,電路工作在測試模式下,通過測試信號控制存儲器輸出端,使得原先不可控輸出變為可控,如圖5 所示,與ROM 輸出引腳連接的或門后的組合邏輯部分都實現了可測試。

圖5 ROM 存儲器輸出引腳添加控制邏輯后ATPG 報告圖

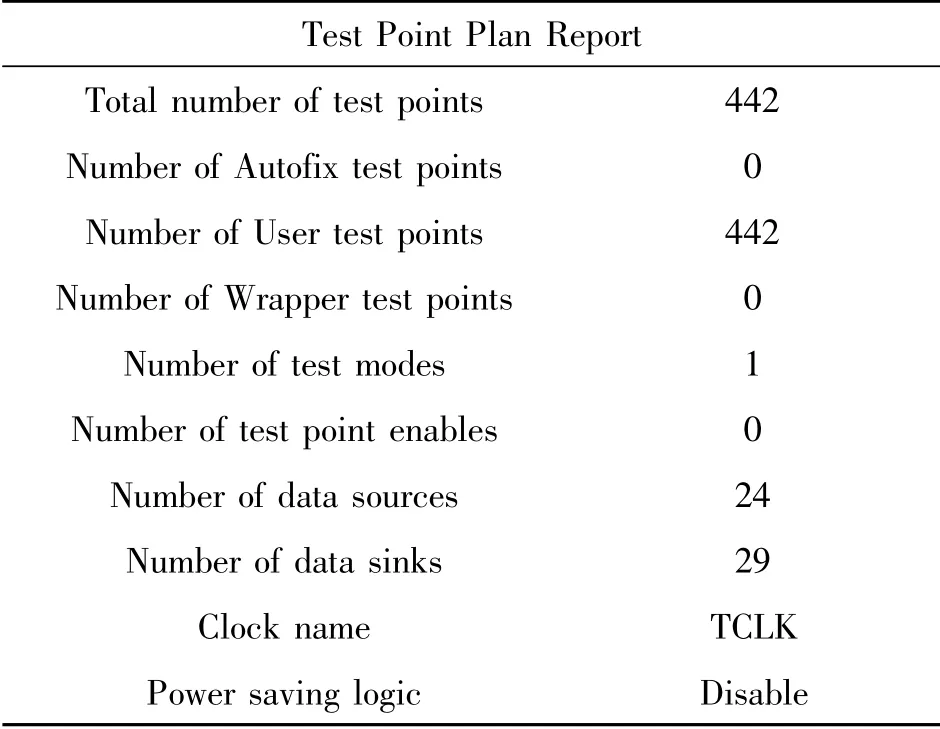

對于芯片設計中其它的嵌入式存儲器模塊如SRAM,FLASH 等,采用類似的方法,使用DFT 工具插入測試點,在該數字信息安全芯片設計中的所有嵌入式存儲器周圍一共插入了442 個測試點(如表1 所示)。

表1 DFT 測試點插入報告

2.2 測試報告結果分析

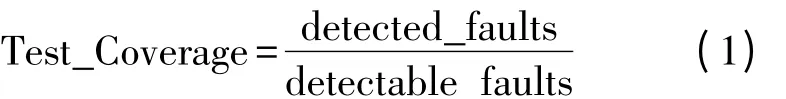

測試覆蓋率(Test Coverage)是反應測試圖形質量的最有效的手段,其計算公式為:

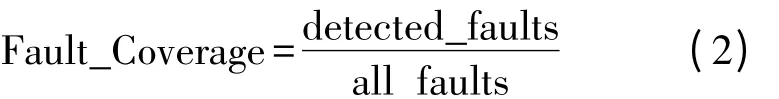

故障覆蓋率(Fault Coverage)定義了檢測出的故障占總故障的百分比,其計算公式為:

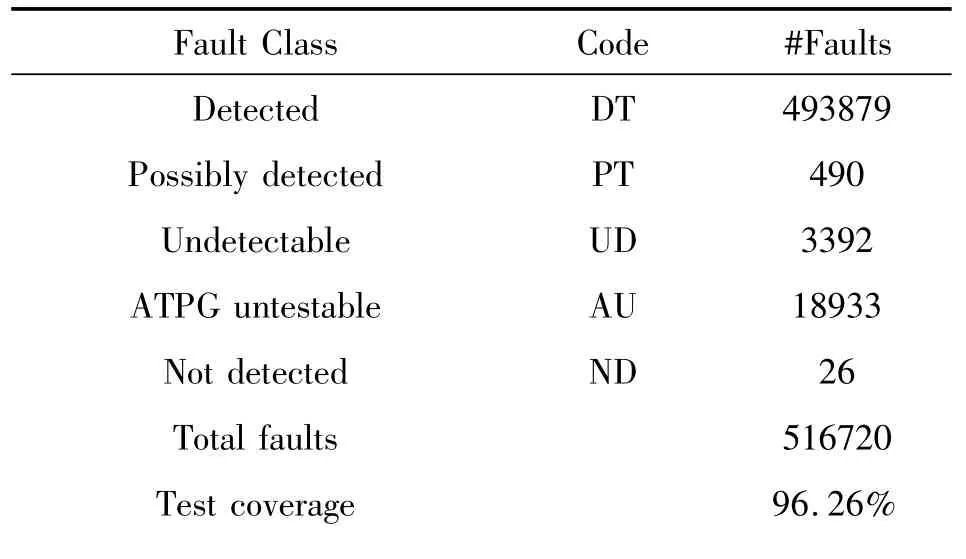

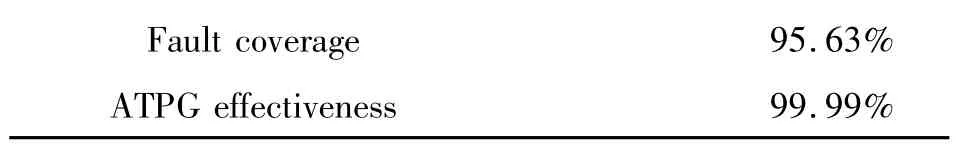

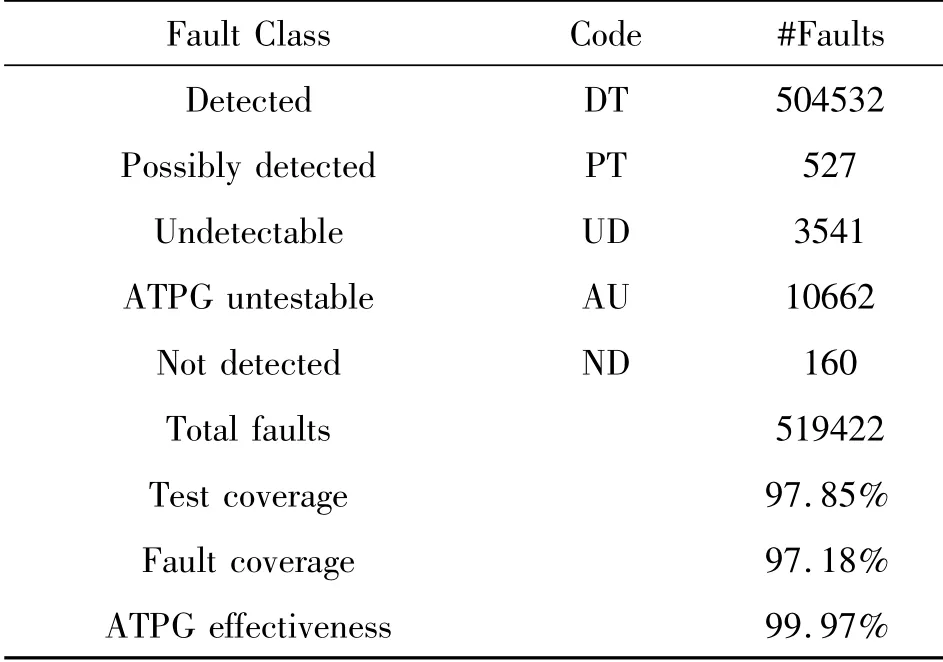

測試覆蓋率和故障覆蓋率是測試技術有效性的重要度量方法,是用來表征測試完整性的重要手段。在該數字信息安全芯片設計中,針對嵌入式存儲器陰影邏輯增加適當的觀察寄存器和控制邏輯后,故障覆蓋率較原先設計得到了改善。表2 為修改設計前ATPG 工具測試報告,表3 為修改設計后ATPG工具的測試報告。

表2 設計前的ATPG 測試報告

?

表3 改進設計后的ATPG 測試報告

比較后可以看出,該方法使得測試覆蓋率提高了1. 59%,故障覆蓋率提高了1. 55%,達到了97.18%,芯片的可測性有了很大的提高。設計前后芯片的面積如表4 所示,該方法對芯片面積影響甚微,最后測試了全芯片的功耗為137.9013 mW,滿足低功耗要求。

表4 修改設計前后芯片面積報告單位:μm2

3 結束語

本課題介紹了SOC 中嵌入式存儲器陰影邏輯在固定故障測試時的不利影響,深入分析了基于掃描結構的可測性設計原理的測試應用,提出了一個測試陰影邏輯的有效方法,對于降低芯片測試成本,提高產品的可用性指標,減少產品的維護費用具有重要意義。本設計雖是針對一個具體數字信息安全芯片的應用,但具有普遍性意義。在實際項目中,測試工程師還需要明晰設計的功能測試結構,要注意測試控制信號的選擇是否與測試模式相匹配,否則無法完成相應的測試期望,對于某些陰影邏輯不能使用DFT 工具自動插入測試點的,要盡早與設計工程師進行協商,將測試電路寫入RTL 中。

[1] 雷紹充,邵志標,梁峰. 超大規模集成電路測試[M]. 北京:電子工業出版社,2008.

[2] Synopsys Inc.Synopsys Online Documentation[CP/DK].2010.

[3] Hao Zhang,Wally Li. Design for Test with DFT-MAX Adaptive Scan in Low Power Design[EB/OL]. http://www. synopsys.com.cn/information/snug/2006-collection/design-for-test-with-dft-max-adaptive-scan-in-low-power-design,2006.

[4] 劉文峰.全掃描結構在MCU 設計中的應用[EB/OL]. 中國科技論文在線,http://www. paper. edu. cn/index. php/default/releasepaper/content/200702-30,2007-02-03.

[5] 成立,王振宇,高平,等.VLSI 電路可測性設計技術及其應用綜述[J].半導體技術,2004,29(5):20-34.

[6] 克拉茨.數字集成電路與嵌入式內核系統的測試設計[M]. 何虎,馬立偉,等譯.北京:機械工業出版社,2006.

[7] 唐玉蘭,于宗光,李天陽,等.一種改進的基于掃描的電路設計[J].微計算機信息,2006,22(2):235-237.

[8] 劉峰,梁勇強.大規模集成電路可測性設計及其應用策略[J].玉林師范學院學報,2005,26(5):29-33.

[9] 陸思安,史崢,嚴曉浪.面向系統芯片的可測性設計[J]. 微電子學,2001,31(6):440-442.