基于FPGA 的高速數據采集系統的設計與實現*

常高嘉,馮全源

(西南交通大學微電子研究所,成都610031)

電子信息技術近些年來持續迅猛發展,通信信號的帶寬已變得越來越寬,調制方式也從傳統的模擬調制發展到數字調制、矢量調制,編碼方式也在不斷地趨于復雜化。為了滿足對較寬頻域范圍內高頻、瞬態信號細節的精確、實時檢測分析,必須要有一種數據采集系統,這種系統必須具有高采樣率、高分辨率,以便于對高速、復雜的信號進行快速的采樣、存儲、傳輸和分析。應用可編程門陣列FPGA 可使數據采集系統具有高度的靈活性,基于FPGA 的高速數據采集是現代測試系統中非常重要的一種數據記錄與處理設備[3]。

本文設計了一種由AD、FPGA 和DSP 組成的數據采集系統,系統的采樣精度為12 bit,采樣率為100 MSPS。該系統主要用于對盲信號的分離及信號參數的識別。

1 系統結構

數據采集系統的原理框圖如圖1 所示。該系統使用的ADC 芯片為ADI 公司的AD9233,采樣精度為12 bit,采樣率為100 MSPS;FPGA 選用的是Altera 公司的CycloneⅢ系列EP3C16Q240C8;DSP為TI 公司的TMS320C6416,其最高主頻為1 GHz。該數據采集系統主要由前端信號調理電路、模數轉換電路、FPGA 電路和DSP 電路組成。

圖1 數據采集系統結構圖

模擬信號首先經過前端調理電路使其幅度轉換成適合AD9233 處理的范圍,并將單端信號轉換成差分信號后輸出給AD9233,AD9233 在采樣時鐘的控制下完成模數轉換,然后FPGA 將ADC 量化后的信號寄存在FIFO 中,最后DSP 通過接口電路從FPGA 的FIFO 中讀取數據并做后續的一些處理。整個系統中,DSP 起主控作用,它控制著FPGA 是否對AD 的輸出數據進行寄存及是否從FPGA 的FIFO 中讀取數據。

本高速數據采集系統的關鍵是前端調理電路的設計與實現。前端調理電路完成對輸入信號幅度的調整,阻抗匹配,并把單端信號變成抗噪性更好的差分信號。前端調理電路的抗干擾能力、增益控制特性、頻率特性、時延特性等是設計中需要重點考慮的因素,本設計中使用變壓器模式和放大器模式來完成前端調理電路的設計。

2 設計實現

2.1 前端調理電路

前端調理電路的作用是將模擬信號的幅度調整為適合ADC 芯片處理的范圍,同時將單端信號轉變成AD 需要的差分信號。本設計中采用了兩種方法設計前端調理電路,一種是使用變壓器,一種是差分放大器的方法。兩種方式的電路如圖2 和圖3 所示。

圖2 采用變壓器分式的前端調理電路

圖3 采用差分放大器方式的前端調理電路

兩種方法各有優缺點,需要根據模擬信號的特點和設計目標來確定選擇哪種處理方式。由于變壓器是無源交流耦合器件,所以產生的噪聲很小,只能將交流信號輸出到ADC 芯片,同時它的通帶平坦性和驅動能力差,無動態隔離能力,提高增益會降低AD 的模擬帶寬。而放大器是有源器件,會產生較大的噪聲,但是它的通帶平坦性和驅動能力好,可以提高動態隔離,增益提高后對AD 的模擬帶寬影響很小。通過分析變壓器和放大器的特點,前端調理電路優先器件的選擇可以總結為表1 所示。

表1 ADC 前端調理電路中變壓器和放大器的性能對比

2.2 時鐘電路

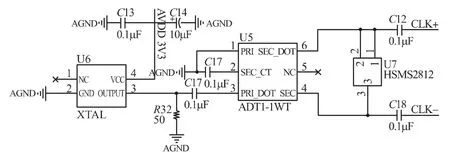

ADC 芯片的采樣是在時鐘的控制下完成的,所以時鐘信號的質量對AD 的影響非常大,特別是高速、高分辨率ADC 或是中頻欠采樣時對時鐘輸入信號的質量尤為敏感。所設計的電路如圖4 所示。

圖4 系統的時鐘電路

本設計用一個100 MHz 的有源晶振產生時鐘源,然后用一個變壓器將單端時鐘信號轉成差分信號后交流耦合到AD 的CLK+和CLK-引腳端,并在變壓器的次級,靠近CLK+和CLK-引腳處跨接一組背對背肖特基二極管。這兩個二極管可以將輸入到AD 的時鐘信號限制為約差分0.8 V 峰峰值。這樣,既可以保留信號的快速上升和下降時間,還可以防止時鐘的大電壓擺幅饋通至AD9233 的其他部分,這一點對時鐘的低抖動性能來說非常重要。

2.3 FPGA 程序設計

ADC 芯片輸出數據的速度是100 Mbyte/s,而DSP 接口速度低于100 Mbyte/s,所以需要通過FPGA對數據進行緩存。FPGA 通過使用FIFO 的方法來完成數據的緩存。FPGA 的程序設計由Verilog 語言實現,主要由4 部分組成,與AD 的接口程序、與DSP 的接口程序、循環FIFO、控制器。控制器的作用是對DSP 發送的控制命令進行譯碼,然后控制循環FIFO的讀和寫狀態;FPGA 與AD 的接口程序根據AD 的數據時鐘輸出信號將AD 輸出的數據正確存入FPGA的FIFO 中;FPGA 與DSP 的接口程序根據DSP 的控制信號將地址總線和數據總線上的值傳送給控制器,由控制器來對DSP 的命令進行譯碼。

設計完成后整體的系統實物如圖5 所示。

圖5 系統的整體實物圖

3 PCB 設計及硬件電路的調試

3.1 PCB 設計

高速數據采集系統中,PCB 的設計也是非常關鍵的一方面。PCB 的設計的好壞決定走線上信號的質量。本設計中采用了以下方法來提供信號的質量。

①差分信號要走嚴格的等長差分線。差分線可以提高信號的抗噪性,減小外界對信號的干擾。

②電路中的數字地和模擬地分割開,最后在一點通過0 Ω 電阻連接起來,這樣做能夠減小數字地中的高頻雜波對模擬電路的影響。

③對晶振部分的電路做包地處理。時鐘信號是ADC 轉換中的又一關鍵特性。為保證時鐘的頻譜純度,設計中將晶振部分的電路做了包地處理,這樣可以很好地降低外界對晶振的干擾。

④AD 的10 bit 數字輸出到接口部分的各條走線要等長。等長線可以保證AD 輸出的各個bit 位的數字信號到達接口處的延時相同。

3.2 硬件電路的調試

本電路的調試分3 個階段完成,電源電路的調試、前端調理電路的調試和數字電路的調試。

(1)電源電路的的調試 首先焊接各個電源芯片,并測試電源芯片輸出電壓的紋波。

(2)前端調理電路的調試 本設計中的前端調理電路有變壓器和放大器兩種模式,需測試兩種模式適合處理的輸入信號。經調試發現,變壓器模式適合處理信號幅度較大噪聲大的輸入信號,而放大器適合處理信號幅值小的輸入信號。

(3)數字電路的調試 該部分完成對AD 控制電路的調試,如AD 差分輸入的最大峰峰值、是否使用AD 內的占空比穩定器、各bit 位的數字輸出到接口處的延時情況等。

4 系統測試

系統測試選用的信號源是Tektronix 公司的AFG3252,選用的是頻率是1 MHz,峰峰值為5 V 的正弦波。通過在DSP 中編程讀取FPGA 的FIFO 中的數據,得到的波形如圖6 所示。可以看出DSP 得到的數據穩定且基本上沒有雜波,為后續的數據處理奠定了良好的基礎。

圖6 DSP 中讀取到的系統處理完成的波形

5 結論

本文完成了由AD、FPGA 和DSP 組成的高速數據采集系統設計。本文對硬件電路中的前端調理電路和時鐘電路做了詳細的介紹。前端調理電路采樣了變壓器和放大器的兩種設計方法,根據輸入信號特性選用不同的設計電路;時鐘電路采用差分信號以減小外界的干擾,同時還在時鐘輸入端加了背對背肖特基二極管以增加穩定性。用Verilog 語言完成了FPGA 部分的控制電路、FIFO、FPGA 與AD 和DSP 的接口程序設計,完成了對數據的緩存,最后在DSP 中可以穩定地讀取到ADC 量化后的波形。

[1] Zhang Baofeng,Wang Ya,Zhu Junchao.Design of High Speed Data Acquisition System Based on FPGA and DSP[C]//Artificial Intelligence and Education(ICAIE),International Conference,2010:132-135.

[2] Xiao Jinqiu,Wang Xinglong,Feng Yi.High-Speed Real-Time Data Acquisition System Based on FPGA[C]//Electronic Measurement& Instruments,9th International Conference,2009:378-391.

[3] 何鵬.基于FPGA 的高速數據采集系統[J].機械與電子,2010(11):96-97.

[4] 肖金球,劉傳洋,仲嘉霖. 基于FPGA 的高速實時數據采集系統[J].電路與系統學報,2005,10(6):128-131.

[5] 李和平,王巖飛.高速數據采集模塊的設計和實現[J].電子器件,2008,31(4):1245-1248.

[6] 何寅生,高俊,婁景藝.基于SOPC 的PCI 數據采集卡的設計與實現[J].電訊技術,2009,49(7):77-80.

[7] 賈龍,林巖.基于DSP 和FPGA 的高速數據采集系統的設計及實現[J].電子測量技術,2007,30(5):95-97.

[8] 王建秋.基于FPGA 的高速數據采集系統的電路設計[J]. 濰坊學院學報,2011,11(4):16-19.

[9] 江明.基于FPGA 的高速數據采集系統的研制[D].哈爾濱:哈爾濱理工大學,2011.

[10] 葛遠香,金燕,胡開明. 基于FPGA 高速數據采集系統控制電路的設計[J].浙江工業大學學報,2009,37(1):96-99.

[11] 李少東.數據采集系統的通道電路設計[J]. 電子質量,2012(3):15-16.

[12] 周曉玲,沈愷煜,吳校生,等.基于DSP 高速外擴FLASH 的高精度數據采集系統[J].電子器件,2012,35(1):111-114.