基于選擇進位32位加法器的硬件電路實現

高建衛

(北京外企徳科人力資源服務上海有限公司 上海 200335)

在數子電路設計中,高性能加法器是現代微處理器中的重要部件,是實時圖象處理和數字信號處理的核心,同時也是微處理器中數據處理的關鍵路徑,而且完成一次操作的周期影響微處理器得主頻,因此人們對提高加法器的性能進行了大量的研究。

1 工作原理

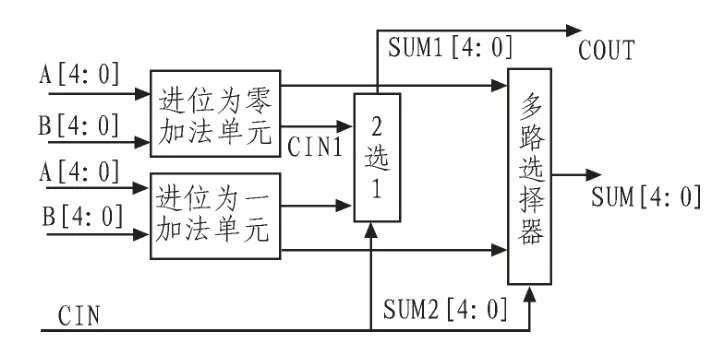

超前進位加法單元首先進行進位為零和進位為一的加法運算,由于加法運算是并行進行的運算速度相當快,硬件電路原理圖分別為:加法單元,二選一,多路選擇器[1]。如圖1所示。

圖1 加法運算硬件原理圖Fig.1 Adder schematic

圖1 中A,B為輸入數據,CIN為進位輸入,CIN1,CIN2分別為兩加法單元產生的進位,SUM1和SUM2分別為兩加法單元產生的和,SUM為兩數最后之和,COUT為最后進位5[2]。

對于32位加法運算從原理上說,首先將其加法單元進行分組[3],也就是說把n位(一般n≥16)分成若干組不一定就是平均分組,因為平均分組以后,每一組加法單元都相同,電路運算花費時間相同,因而產生的選擇進位信號的時間也相同,所以每一組加法單元的進位輸出和最后和的輸出都通過前一級的進位信號選擇產生延時比較長。根據以上所述本文采用一種新的分組算法,也就是差額分組算法。首先將32位(作為例子,這里僅介紹32位,本設計可推廣至2k位,K≥4,K∈N)進行差額分組,分別分為5位,6位,7位,8位,6位,形成階梯形狀運算單元,因為采用這種階梯分組算法可以減少進位選擇時間。例如:在運算的二組6位相加的同時,第一組5位也在進行相加,當第二組運算完成時,第一組運算結果和進位也以完成,通過第一組產生的進位選擇第二組的運算結果和進位信號。以此類推可以得到第三,四,五組運算結果和最后進位結果。在運算32為加法時,其實與8位加法運算時間相當。

圖2是超前進位(CLK)加法器的結構框架(作為例子,這里僅介紹4位CLA,本設計可推廣至k位CLA,K≥2,K∈N)。圖中,PG模塊分別計算各組的進位傳送函數(P)進位生成函數(G)得在值,與以往的超前進位算法相比版圖容易實現,因為以往的超前進位算法計算各組的進位傳送函數(P)和進位生成函數(G)用異或門和與門。

圖2 超前進位加法器結構圖Fig.2 Advanced carry selected adder

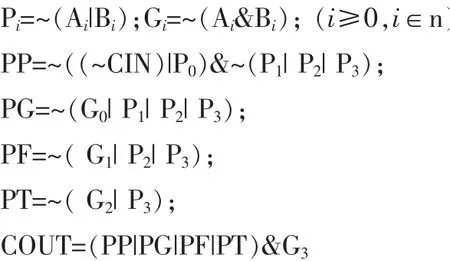

而本設計所用的超前進位算法計算各組的進位傳送函數(P)和進位生成函數(G)用與非門和或非門。如圖3所示即

圖3 帶進位生成函數的運算Fig.3 Operation with carry function

2 邏輯仿真

邏輯仿真是設計校驗的重要步驟。利用ACTIVE HDL軟件可直接提供這一功能。在ACIVE HDL中可以進行邏輯仿真和由SYNPILCITY提供綜合后仿真,以及加入器件和線延時的時序仿真[4]。第一,在OPTION中選擇上層模塊,然后進行功能仿真。首先,用鼠標右擊輸入信號,彈出對話框選擇STIMULATORS,可以加入任何想要的信號。第二,同樣在SYNTHESIS的OPTION中選擇上層模塊和所需的器件(這里我們選用XILINX SPARTAN2提供的25200PQ208),然后進行綜合后仿真。在此過程中我們可以通過SYNPLIFY進行電路優化,然后例如上面所述的相同的方法得到波形圖。這時的波形圖是已經加了器件延時后的結果。第三是在XILINX IMPLEMENTATIN中進行布局布線的時序仿真。在仿真前可以在OPTION中加入相應的約束條件,使其提高運行頻率,圖4即為仿真結果,這個仿真基本上與FPGA的仿真相接近,FPGA是近年來發展迅速的大規模可編程專用集成電路,它在它在電路設計中的應用使設計的電子產品達到小型化和集成化,大大縮短了設計周期,減少了設計費用,降低了設計風險。FPGA器件必將成為電子系統設計的重要手段,具有極其廣闊的發展前景。

圖4 仿真結果Fig.4 Simulation results

3 目標文件產生和器件下載

設計校驗完成之后,利用ACTIVE HDL軟件系統自動處理和生成目標文件(BIT文件),且可經一定方式(主動模式或被動模式)把目標文件配置于XILINX SPARTAN2芯片中,從而完成編程工作。

這里采用被動串行方式(PS)進行配置。專用下載電纜的一端與微型機USB口相連,另一端連至目標系統PCB板的配置插座,經一定的控制方式,把計算機內存中的目標文件配置于PCB板上的XILINX SPARTAN2芯片中[6]。

4 結 論

綜上所述,這種選擇進位加法器運行速度相當快,已經通過FPGA[7-8]驗證,可以運行40—50兆的頻率,如果制成芯片速度應比在FPGA上運行的更快,因為版圖的布局布線比FPGA更加合理,基本上滿足實際工程需要。

[1]RABAEY J M.數字集成電路設計透視[M].2版.北京:清華大學出版社,1999.

[2]Mittal M,Salama C A T.DPTL 4-6 carry looks head adder[J].IEEE J.of Solid State circuits,1992,27(11):1644-1684.

[3]于敦山.沈緒榜.32位定/浮點乘法器設計[J].半導體學報,2001(1):91-95.YU Dun-shan,CHEN Xu-bang.Design of a 32-Bit CMOSFix floating point multiplier[J].Chinese Journal of Semiconductors,2001(1):91-95.

[4]張亮.數字電路設計與Verilog HDL[M].北京:人民郵電出版社,2000.

[5]Agrawal V D.A tutorial on built-in self-test[J].part 1:principles.IEEE Design&Test of Computers,1993(2):73-82.

[6]Configuration and Readback of the Spartan-II and Spartan-IIE FPGA Families[M].Xilinx Company,2008.

[7]周建,祝連慶,張蔭民.基于FPGA的脈沖光纖激光器功率控制系統設計[J].電子科技,2012,25(12):52-55.ZHOU Jian,ZHU Lian-qing,ZHANG Yin-min.Design of pulse fiber laser power control system based on FPGA[J].Electronic Science and Technology,2012,25(12):52-55.

[8]歐亞軍,陳杰.基于FPGA的頻率特性測試儀的設計[J].現代電子技術,2011,34(6):113-115.OU Ya-jun,CHEN Jie.Design of Frequency Characteristic Instrument Based on FPGA[J].Modern Electronics Technique,2011,34(6):113-115.