基于FPGA的數字存儲示波器設計

耿新力,王中訓

(煙臺大學光電信息科學技術學院,山東 煙臺 264005)

示波器作為一種常用儀器,在實驗室和工業化生產線是不可缺少的,并且至今成功完成了從第1代到第7代的改革,八十年代之后數字信號處理技術和微處理器的運用在該行業興起,不久之后便出現了目前廣為使用的高性能數字存儲示波器[1]。數字存儲示波器一般采用微處理器進行數據采集和系統控制,具備組合觸發、超前觸發、波形處理、毛刺捕捉、數字濾波、輸出并拷貝、波形識讀、長時間波形存儲等模擬示波器所不具備的功能[2]。隨著產業的發展,對數字存儲示波器的功能和性能指標的需求不斷提高,更高性能的數字存儲示波器必將是發展的必然。本設計基于Altera公司的EP2C35系列處理器,在模擬數據的采樣、信號頻率的測量、自檢信號的產生、個性化的波形顯示等環節分別進行了創新性優化,最終設計制作出一款更高性能且廉價的數字存儲示波器[3]。

1 系統方案

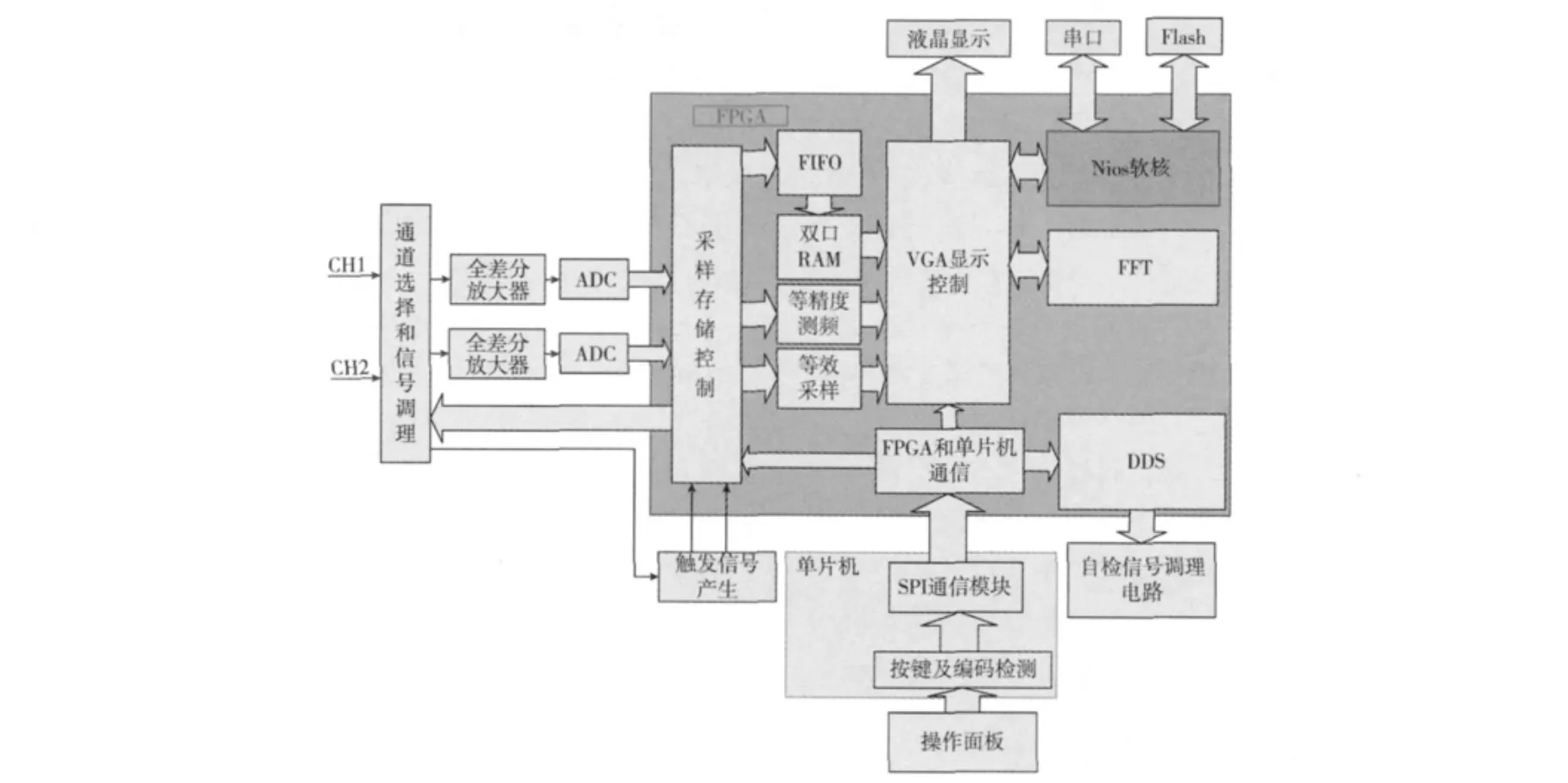

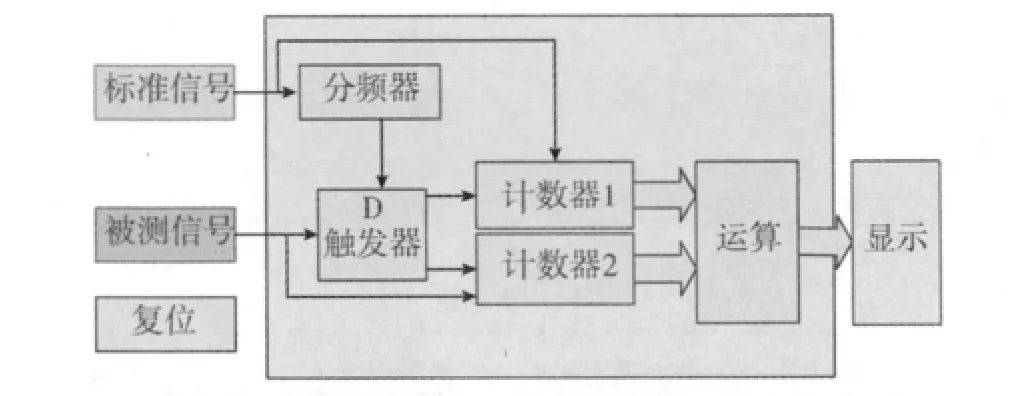

當信號進入數字存儲示波器時,首先示波器將按一定的時間間隔對信號電壓進行采樣,之后對這些采樣值進行數字化,即通過轉換器變換得到代表每一個實際電壓的二進制數字,進一步把這些數字貯存在存儲器中,最終根據數字大小按一定比例把每一個采樣點重現在顯示器上,這樣就能看到清晰的波形[4]。本設計的總體框圖如圖1所示。

本系統在采樣和數字化階段對電路進行了改進,首先要模擬信號經過全差分放大器的預處理將單端信號轉化為差分信號,由高速ADC芯片將差分信號轉換成二進制數字信號,通過采樣存儲控制模塊控制FIFO(First Input First Output)[5]和雙口RAM協調工作完成前端數據采集,通過FIFO來匹配信號采樣時鐘和系統時鐘的不同,雙口RAM存儲采樣后的數據,后端VGA顯示控制模塊從雙口RAM中定期讀取數據,并送至液晶屏實時刷新顯示。為了給示波器提供自檢信號,利用了DDS(Direct Digital Synthesizer)原理產生自檢信號,另外為提高數據的利用效率,采集到的波形數據可以由FPGA內嵌的Nios軟核編程傳到計算機,也可存儲到Flash中用于波形的回放。

2 系統各模塊設計

2.1 垂直靈敏度和水平靈敏度

圖1 系統總體框圖

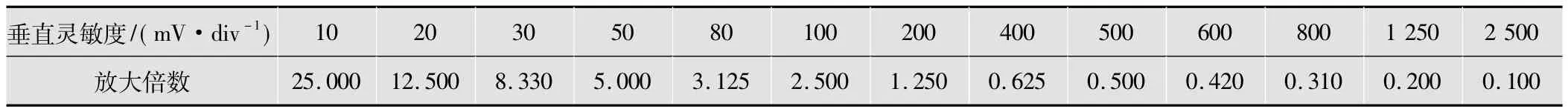

垂直靈敏度對應著對信號的放大倍數,設計由TI公司生產的高速運放Opa690構成的電壓跟隨器以隔離各模塊并提高驅動后級電路的能力,配合VCA810實現了自動增益控制電路,部分檔位的垂直掃描靈敏度所對應的調理電路放大倍數如表1所示[6]。

表1 部分檔位與放大倍數的關系

水平靈敏度對應著ADC的采樣速率,顯示屏選用7 in(1 in=2.54 cm)寸液晶屏 AT070TN92,分辨率為800×480(RGB),將波形有效顯示區域制定為600×400,垂直分為8個格,水平分為12個格,得到50×50像素的格子。對于每個格子有50個點,那么采樣速率和時間檔(水平靈敏度)的關系滿足

式中,T為每個水平格代表的時間,和時間檔相對應。

2.2 高速ADC采樣模塊

模擬信號到數字信號的轉換電路主要由TI公司全差分運算放大器THS4503ID、RC組合接口以及高速ADC芯片ADS828構成。全差分運算放大器THS4503ID實現了單端信號到差分信號的轉換,差分信號具有抑制共模干擾的能力,差分信號相當于一對相位相差180°的單端信號相減,因此能提供2倍于單端信號的輸入信號動態范圍,如圖2所示,若同樣提供2 V(峰峰值)的信號,差分信號每一條僅需1 V(峰峰值),這樣凈空較大,失真較小。

放大器和高速ADC之間的RC接口電路可以提供隔離,并且可以起一個低通的噪聲濾波器的作用,10 bit高速ADC轉換器ADS828的最高采樣頻率為75 MHz,滿足最大實時采樣頻率為70 MHz的要求[7]。

圖2 單端信號轉化為差分信號

2.3 觸發信號產生電路

為了在屏幕上顯示比較穩定的波形,對于周期信號必須保證每次采樣的起始位置相同。為了兼顧高速電壓比較器TL3016良好的高頻特性和LM311滯回比較器優良的低頻特性,本系統利用TL3016和LM311制作雙路觸發信號產生電路,根據實際信號頻率選擇不同的觸發信號產生電路。

2.4 波形數據采集模塊

由圖1的系統框圖以及本系統控制水平靈敏度的方法(通過改變高速ADC采樣時鐘頻率來改變水平靈敏度)可以看出,這個設計必然帶來ADC的采樣時鐘和FPGA系統時鐘的不匹配問題,為解決前后時鐘不匹配問題本系統引入了一個深度為1024 點的FIFO來匹配采樣時鐘和系統時鐘,輔以雙口RAM來暫存采樣數據,兩者協調工作不僅提高了本系統的工作效率也保證了顯示的穩定。

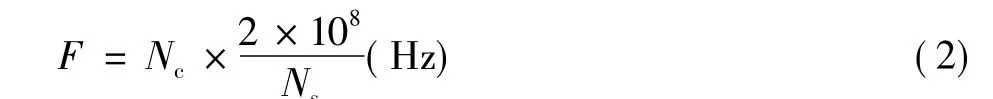

2.5 等精度頻率測量模塊

如圖3所示,被測信號經過觸發信號產生電路和相應的整形電路產生比較標準的方波信號,由FPGA的I/O口輸入頻率測量系統,標準信號由50 MHz系統時鐘倍頻至200 MHz,在系統初始狀態預置一個預置閘門,當預置閘門為高電平(允許計數)時,當被測信號的下降沿到達D觸發器輸入端時同時啟動計數器1和計數器2分別對標準信號與被測信號計數,而當計數到預置閘門拉低的時候實際閘門并不是立即關閉,而是等待下一個被測信號的下降沿的到來,當D觸發器采樣到該下降沿時才能關閉實際閘門[8],假定一次測量過程中實際的閘門時間內對標準信號的計數值為Ns,對被測信號的計數值為NC,由于該系統采用的標準信號為200 MHz,所以被測信號頻率為

圖3 等精度頻率測量系統框圖

2.6 幅度測量

示波器要能夠對被測量信號的頻率、峰峰值和有效值進行實時性的準確測量,本系統利用FPGA在數字信號處理方面的速度和精度的優勢,可以直接對采集到得數字量結合統計學原理很方便地測得被測信號的峰峰值和有效值并予以顯示。

2.7 基于DDS的自檢信號發生器

由于示波器在特定的場合需要校正,特制作基于DDS(直接數字合成)的自檢信號發生器,使本系統使用場合更廣,功能更加強大。DDS從相位角度考慮能夠產生正弦波、三角波、方波以及任意編輯波形,而且波形的頻率、幅度、相位均可以靈活調整,并且精度較高、具有較高頻率切換率。

DDS方程為

其中:fO為需要輸出的模擬信號的頻率,K為頻率控制字,fc為DDS模塊的系統時鐘頻率[9]。

2.8 SOPC資源配置及波形存儲

軟件部分利用了FPGA內嵌的軟核Nios,來控制波形的存儲、回放,并且將波形數據通過串口傳送到計算機,之后便可以利用圖形化設計軟件VB或LabVIEW在計算機上設計比較人性化的顯示界面,或者對采集到的波形數據進行處理。

Flash存儲器使用AMD公司的AM29LV320DB90EI,存儲區可以配置成兩種,一種模式是,存取2 Mbyte個字,每個字16 bit,分別為D0~D15。另一種存取模式是存取4 Mbyte個字,每個字8 bit,分別為D0~D7。系統選用的高速ADC是10 bit,所以將AM29LV320DB90EI配置成第一種模式。根據存儲波形的多少控制存儲地址。掉電后波形數據存在Flash相應空間中,需要再次顯示上次或某個波形時只要按該波形對應的存儲地址讀出即可。

3 測試結果及分析

3.1 測試條件

測試溫度為26℃,信號發生器為RIGOL-DG1022型,選用RIGOL-DS1102C型示波器作為標準示波器。采用分模塊的測試方法依次測試各項功能。

3.2 測試結果

3.2.1 波形測試

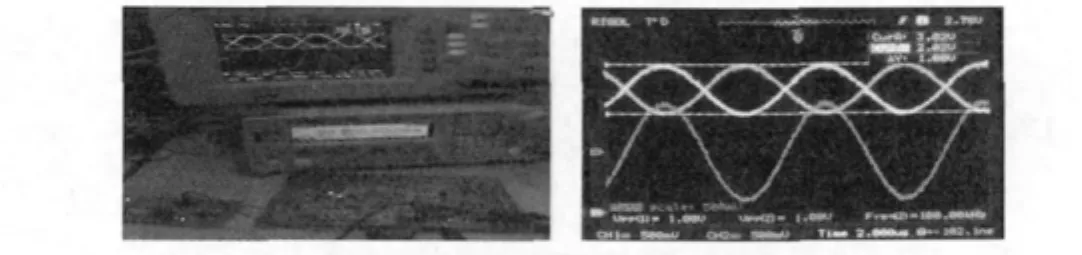

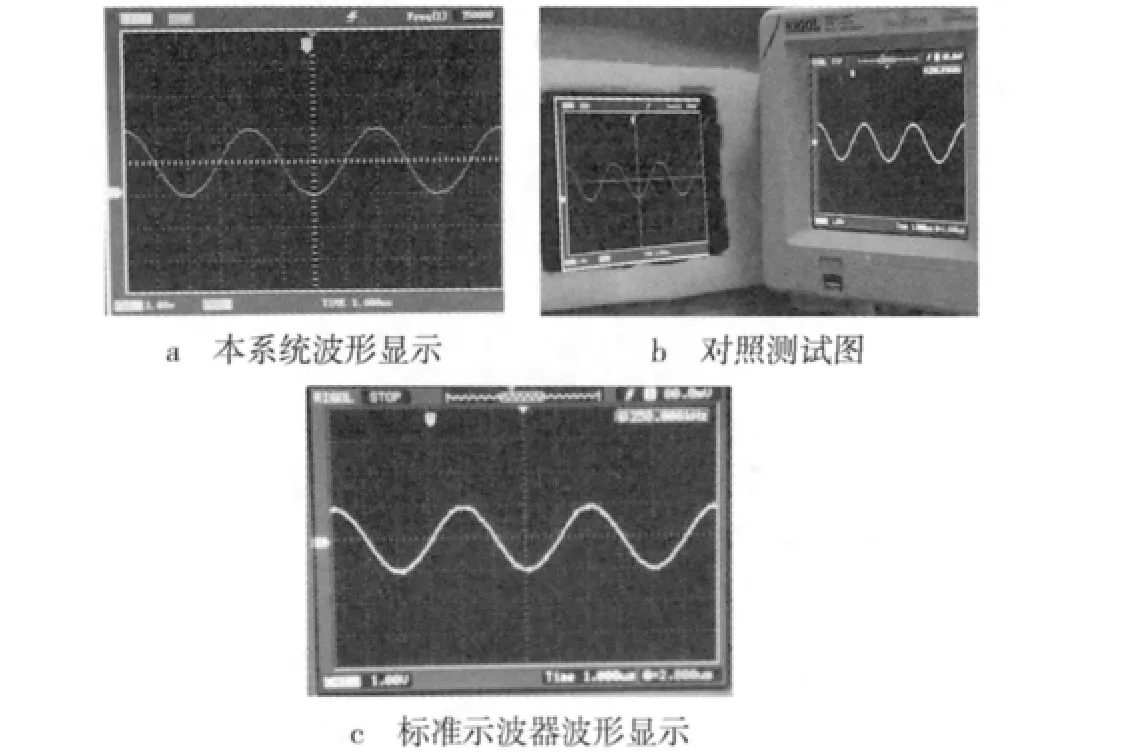

測試結果如圖4所示。

圖4 本系統波形顯示與標準示波器波形顯示對照圖

通過對比標準示波器和本系統的波形顯示可以看出系統工作穩定,各項基本指標顯示正確,同時也驗證了對模擬信號預處理、觸發方式、數據存儲機制的優化的正確性。

3.2.2 頻率、電壓測試

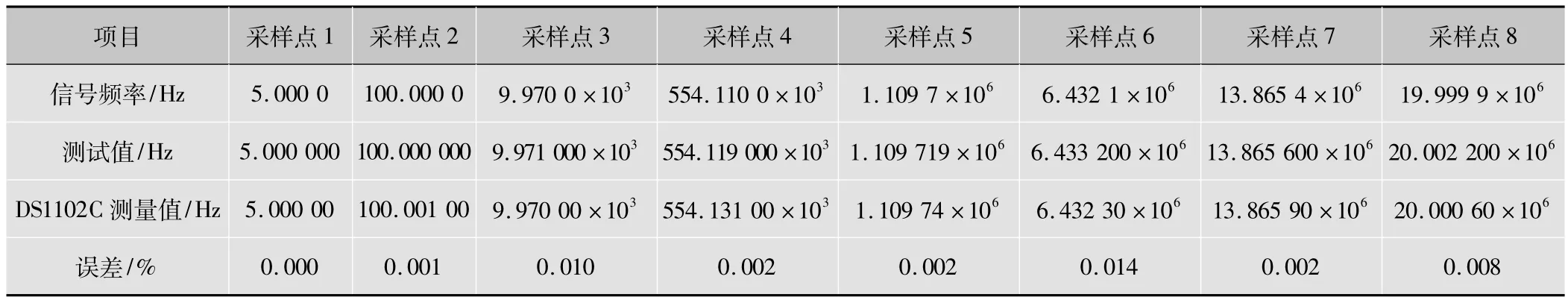

調節函數發生器,依次保持輸入信號的電壓、頻率不變,將輸入信號的頻率、電壓依次以一定步進值步進,觀察系統測量值,測量數據如表2、3所示。

通過頻率和電壓的測試結果可以說明,系統可以準確的測試頻率5~20 MHz,幅度(峰峰值)0~10 V的模擬信號,并且頻率的誤差控制在0.000% ~0.015%之間,幅度測試誤差1.00% ~4.50%之間,在允許范圍內。

3.2.3 波形數據多方位存儲測試

經測試,當需要存儲波形數據時可正確通過NIOS調用雙口RAM里的波形數據,并將這些數據存儲在Flash中,當需要回放原來的波形數據時也可以正確的調出原來存取的數據,并在顯示屏上顯示,不丟失采樣點,另外系統與上位機的交互正常,完成了數據到Flash和上位機的多方位存儲。

表2 頻率測試結果及誤差表

3.2.4 基于DDS的自檢信號測試

經多次檢測,自檢信號產生模塊可以正確輸出頻率0~5 MHz,幅度(峰峰值)0~10 V的無失真模擬信號,另外也可對波形的頻率和幅度以任意步進值進行編輯,達到了預定要求。

4 結論

本設計通過FPGA進行了數字存儲示波器的設計,克服了同步信號的提取和高頻噪聲的消除等難點問題。采用雙路觸發信號產生電路既兼顧了低頻信號的測量也兼顧了高頻信號的采集,解決了采集高速信號和低速信號之間的矛盾,取得了良好的效果,另外在等精度測頻模塊對標準信號的選取也經過了多次仿真和實施,使得數值的選取和理論的研究真正具有實用性。該系統提出FIFO+RAM存儲機制、數據的多方位存儲、信號預處理等優化方法,對數字存儲示波器的發展具有一定的參考和實用價值。

[1]朱明強.基于單片機及CPLD的數字存儲示波器的研究與設計[D].北京:北京交通大學,2008.

[2]湯向恒.模擬示波器擴展為數字示波器[J].自動化與儀器,2003,18(5):26-28.

[3]劉君華.現代檢測技術與測試系統設計[M].西安:西安交通大學出版社,1999.

[4]徐欣,于紅旗.基于FPGA的嵌入式系統設計[M].北京:機械工業出版社,2005.

[5]ROBERTO P A.A versatile linear insertion sorter based on an FIFO scheme[C]//Proc.Symposium on VLSI,2008.[S.l.]:IEEE Press,2008:357-362.

[6]TESSIER R,BETZ V,NETO D,et al.Power-efficient RAM mapping algorithms for FPGA embedded memory blocks[J].IEEE Trans.Computer-Aided Design of Integrated Circuits and Systems,2007,26(2):45-52.

[7]王松武.電子創新設計與實踐[M].北京:國防工業出版社,2005.

[8]夏宇聞,黃然.Verilog SOPC高級實驗教程[M].北京:北京航空航天出版社,2009.

[9]CAO X H,LUO F L,BAI F T,et al.A DDS waveform generator for electromagnetic nondestr-uctive testing[J].Key Engineering Materials,2005(6):12-21.