基于TQ 時序分析器的時序分析和約束

李 珈

(湖北科技職業學院,湖北武漢,430074)

0 引言

一般的FPGA 工程師在進行電路設計的時候更加側重于代碼的編寫與硬件測試,若是最高頻率沒有達到要求,最先想到的也是換一個速度更快的芯片,而不會去關注時序分析和約束的問題。實際上,當設計比較簡單,且運行頻率比較低的時候,不加任何的時序約束,FPGA 軟件都可以綜合出來可用且相對較可靠的代碼,但當設計比較復雜,運行頻率比較高的時候,不做時序分析,不加上一些必要的約束,就很難保證設計能且穩定的運行在所設定的頻率上。

所有的FPGA 廠商都提供靜態時序分析(STA,Static Timing Analysis)工具,可對設計的時序性能作出評估。TQ(TimeQuest)是Altera 公司的第二代靜態時序分析器,它采用業界標準的設計約束文件(SDC 文件,Synopsys Design Contraint File),能夠適應FPGA 的密度和速率增長的趨勢,完成傳統的FPGA 時序分析工具很難分析的設計接口。TQ 提供多種約束命令和圖形化的操作界面,簡化了生成時序約束文件的方法,提高了時序報告閱讀的效率。

1 靜態時序分析的概念

靜態時序分析是相對于動態時序仿真而言的,由于動態的時序仿真占用的時間非常長,效率低下,因此STA 成為最常用的分析、調試時序性能的方法和工具。那么什么是靜態時序分析呢?它可以簡單地定義為:設計者提出一些特定的時序要求(或者說是添加特定的時序約束),套用特定的時序模型,針對特定的電路,通過分析每個時序路徑的延時,計算出設計的最高頻率,查看系統時序是否滿足設計者提出的要求,同時可以發現時序違規。

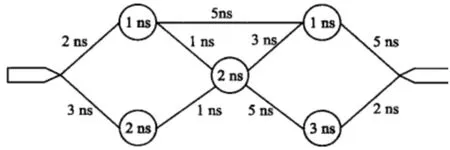

所謂條條大路通羅馬,在實際的電路中,一個信號從起始點傳播到終點可能會經過不同的傳輸路徑,所以對于同一組起始點和終點,會存在不同的時序路徑(timing path),而由于不同的傳輸路徑的參數會有差異,所以這些時序路徑的延遲就不同。舉一個簡單的例子,假設信號從輸入到輸出需要在FPGA 內部經過一些邏輯延時和路徑延時,系統要求這個信號在FPGA 內部的延時不能超過15ns,而開發工具在執行過程中找到了如圖1 所示的一些可能的布局布線方式。那么,怎樣的布局布線能夠達到系統的要求呢?仔細分析一番,發現所有路徑的延時可能為14ns、15ns、16ns、17ns 及18ns,有兩條路徑能夠滿足要求,那么最后的布局布線就會選擇滿足要求的兩條路徑之一。

圖1 靜態時序分析模型

STA 工具以約束作為判斷時序是否滿足設計要求的標準,因此要求設計者正確輸入時序約束,以便STA 工具能輸出正確的時序分析結果。因此靜態時序分析的前提是設計者先提出要求,然后時序分析工具才會根據特定的時序模型進行分析,即有約束才會有分析。若設計者不添加時序約束,那么時序分析就無從談起。

2 基于TQ 時序分析器的時序分析和約束

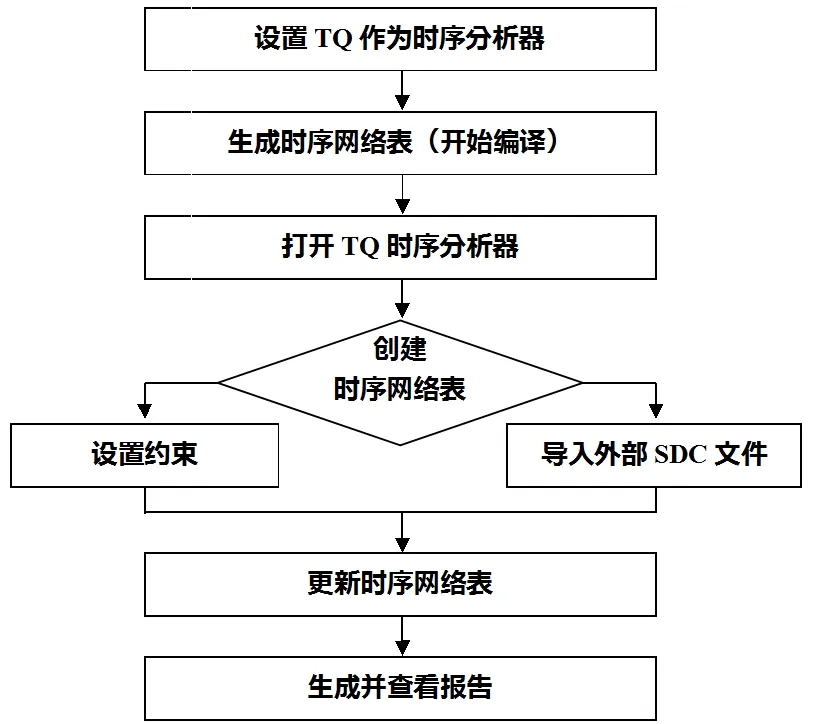

TimeQuest 時序分析器可用于分析設計中所有邏輯,并有助于指導Fitter 達到設計中的時序要求。設計者可以使用時序分析器產生的信息來分析、調試并驗證設計的時序性能;還可以使用快速時序模型進行時序分析,驗證最佳情況(最快速率等級的最小延時)條件下的時序。TQ 時序分析器采用SDC 文件格式作為時序約束輸入,不同于Timing Analyzer采用QSF(Quartus Settings File)約束文件。這正是TQ 的優點:采用行業通用的約束語言而不是專有語言,有利于設計約束從FPGA 向ASIC 設計流程遷移;有利于創建更深入的約束條件。TQ 分析器的操作流程如圖2 所示。

由此可見,TQ 時序分析器進行約束和分析的對象是FPGA 器件的底層物理單元,均來自Quartus II 編譯流程各階段的編譯結果,因此二者是緊密結合在一起的。Quartus II 編譯中的“分析與綜合”之后,會進行“映射”,生成的數據庫對應FPGA 器件的物理結構,可以供TQ 進行時序約束之用。由于“映射”過程實際是預先布局過程,尚未執行時序驅動的布局和布線工作,也沒有讀入引腳位置等約束信息,所以在這一步進行的時序分析是時序預估,不能獲得準確的時序分析結果;在獲得時序約束信息后進入編譯中的“適配”環節,對應的操作是布局和布線,這一環節會努力按照時序約束的要求進行布局和布線優化,并生成FPGA 最終實現結果的時序網表,TQ 根據這一網表進行分析,可以反映最終的時序特性,檢查適配結果是否滿足了時序約束的要求。

好的約束必須以好的設計為前提,沒有好的設計,在約束上下再大的功夫也是沒有意義的。不過,通過正確的約束也可以檢查設計的優劣,通過時序分析報告可以檢查出設計上時序考慮不周的地方,從而加以修改。通過幾次分析-修改-分析的迭代也可以達到完善設計的目標。因此,設計是約束的根本,約束是設計的保證,二者是相輔相成的關系。

圖2 TQ 時序分析器操作流程圖

3 結語

對自己的設計實現方式越了解,對自己的設計的時序要求越了解,對目標器件的資源分布和結構越了解,對EDA 工具執行約束的效果越了解,那么對設計的時序約束目標就會越清晰,相應地,設計的時序收斂過程就會更可控。

[1] Altera 公司.TimeQuest 時序分析儀為FPGA 設計分析提供自然的SDC 支持[J],半導體技術,2006 :86.

[2]周海斌.靜態時序分析在高速FPGA 設計中的應用[J].電子工程師,2005:31(11),41-43.

[3]劉福奇.FPGA 嵌入式項目開發實戰[M].北京:電子工業出版社,2009.