基于NiosⅡ軟核處理器的圖像數據緩存系統的設計

孟令軍,李鵬飛,安航行,趙 林

(中北大學電子測試技術國家重點實驗室儀器科學與動態測試教育部重點實驗室,山西 太原 030051)

責任編輯:魏雨博

基于遙測系統的蓬勃發展,尤其是在圖像遙測方面的深入研究,當今已經實現了在多個領域的發展與應用。本文設計了一種由全硬件FPGA實現的圖像采集系統,以FPGA卓越的并行處理能力為依托,對系統關鍵模塊進行合理的設計,將大量運算采用并行處理的方式實現,不僅可以大幅提高數據處理度,而且可以極大地提高系統的信息處理能力。同時內嵌的Nios II處理器提高了圖像處理速度并精簡了系統的體積。因此,廣泛深化研究基于Nios II的視頻圖像處理技術,對開發高成效的視頻圖像采集系統有著廣闊而深遠的理論與現實意義。

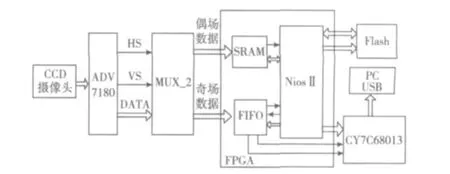

1 系統原理與基本架構

圖像采集存儲系統的主要功能是完成對單路模擬圖像信號的模數轉換并對轉換后數據進行實時采集、存儲,同時系統也可以根據遙測命令將數據通過通信接口上傳給PC或者下發給對應的遙測接收設備。系統結構如下圖1所示,主要包括4個模塊:圖像獲取模塊,主要實現模擬圖像的采集,為后端信號轉換提供輸入;圖像信號轉換模塊(A/D),完成圖像信號由模擬到數字的轉換、圖像信號與其它信號的分離、視頻信號的格式轉換等,為后端提供可以處理的數字信號;圖像數據處理模塊,接收前一模塊的數字圖像信號,對數據進行計算、存儲和各種處理等,一般數據接收可以采用單片機、DSP等實現,本文采用FPGA實現;通信模塊,實現系統與外界的數據和命令交互,有多種工業接口可以選擇。如圖1所示,簡明地表示出了系統內各模塊的關系。

圖1 系統結構流程圖

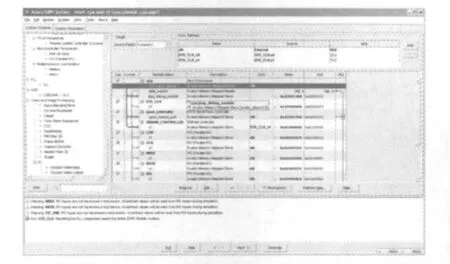

2 基于NiosⅡ的嵌入式處理器設計

SOPC系統的開發流程主要從硬件開發和軟件開發兩個方面來進行。硬件開發的主要目的是使用SOPC Builder搭建Nios II系統,然后在Quartos II中經過邏輯綜合、布局布線生產硬件結構,它將處理器、存儲器、I/O接口等系統設計的功能模塊集成到一個PLD上,構成一個可編程的SoC(片上系統);根據設計的需求來開發軟件,在Nios II IDE環境中利用C/C++語言和系統自帶的API函數編寫實現功能的程序,系統軟件程序主要在Nios II IDE環境中編寫C語言程序實現,主要目的是給VHDL硬件模塊提供模塊啟動、結束等信號,同時進行一些模塊的配置和時鐘控制,使各模塊都能正常工作,最后將硬件與軟件一起下載到硬件進行聯合調試來驗證設計,如圖2所示。

圖2 構建嵌入式處理器模塊(截圖)

3 I2C總線的設計

IIC(Inter-Integrated Circuit)或I2C即集成電路總線,是PHILIPS公司開發的兩線式串行總線,主要是用來連接整體電路(ICS)或微控制器及其外圍設備。它由可同時發送、接收數據的串行總線:數據線SDA和時鐘SCL構成。所有接到I2C總線設備上的串行數據SDA都接到總線的SDA上,各設備的時鐘線SCL接到總線的SCL上。I2C總線上允許連接多個微處理器以及各種外圍設備,如存儲器、LED及LCD驅動器、A/D及D/A轉換器等,串行的8位雙向數據傳輸位速率在標準模式下可達100 kbit/s快速模式下可達400 kbit/s高速模式下可達4 Mbit/s。它在傳送數據過程中共有3種類型信號:開始信號、結束信號和應答信號。在I2C總線傳輸過程中,將兩種特定的情況定義為開始和停止條件(如圖3所示):當SCL保持“高”時,SDA由“高”變為“低”為開始條件;當SCL保持“高”且SDA由“低”變為“高”時為停止條件。開始和停止條件均由主控制器產生。

圖3 I2C數據傳輸圖

在硬件開發時,需要在軟核中添加2個IO模塊(如圖4),并將其命名為 SCL和 SDA,其中,SCL為output ports only(僅輸出),SDA 為 Bidirection(tristate)port(雙向),建好以后,如圖4所示。

圖4 SOPC中構建I/O模塊

4 視頻處理芯片ADV7180

在系統設計中,采用了可以實現模擬圖像信號到數字圖像信號轉換的是ADI公司推出的一款10位、4倍過采樣的視頻圖像解碼器ADV7180,它可實現對多格式模擬視頻信號采樣分析。ADV7180接口設計極為簡單,只需要通過設計簡單的數字輸出接口ADV7180便可以與各種編解碼器、移動視頻處理器及ADI公司的數字圖像壓縮芯片(如ADV212等)實現無縫連接。同時,與其數據同步輸出的HS、VS、數據時鐘和FIELD信號也可為LCD控制器和其它視頻解碼芯片提供時序基準,擴展非常方便。由于在設計中不對其寄存器進行讀數操作只進行寫配置操作,所以,在設計中將其ALSB管腳直接接地。在系統中ADV7180是掛載在I2C總線上的I2C從設備,總線通過從設備地址識別ADV7180進而完成對其進行配置。解碼器ADV7180要實現正常轉換功能必須與I2C總線的正確配置。系統控制核心Nios II軟核在獲取啟動信號后啟動I2C控制器完成芯片配置,啟動芯片開始工作。正確配置后啟動ADV7180可以自動檢測輸入的視頻信號制式,并將相應的模擬信號轉換成對應數字信號輸出來,關鍵處理如何正確配置ADV7180中各寄存器。

5 USB通信模塊

根據設計時提出的要求,既要實現設備控制,又要完成高速數據傳輸,為了滿足需要選用了Cypress公司的EZUSB FX2接口芯片CY7C68013。它采用通用可編程接口(GPIF)方式通過FPGA與Flash進行數據操作。數據的讀取通過GPIF口來實現,命令的下發通過PE口來實現。PE口是單一功能口,只要在固件架構中的初始化程序中將PE口使能為輸出口,在主程序中接收通過上位機下發的命令,然后通過PE口將相應命令值輸出,Flash控制器根據接收到的PE口的不同命令對Flash進行不同的操作。GPIF是一個對于FX2端點FIFO的內部主控制器,它代替了外部的“膠合”邏輯電路,在整個數據讀取過程中,為了匹配USB2.0于FPGA內部Flash控制器之間的數據傳輸,硬件擴展了16 kbyte的硬FIFO(IDT7206)來匹配讀數時序來完成Flash數據的讀取。

6 系統調試結果及分析

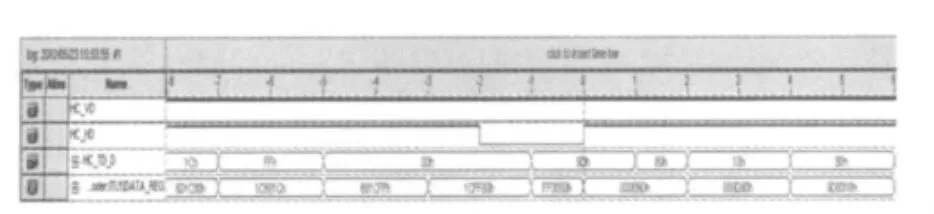

通過Quartus II下的嵌入式邏輯分析儀SignalTap II Logic Analyzer對圖像數據上傳進行了實時采樣的時序分析,圖5是8位圖像數據和PIC_Decoder模塊中數據寄存器DATA_REG關系圖。經過上位機軟件還原數據后,得到的圖片信息清晰無誤碼率,達到了預設的效果,可進一步完善用于實際應用。

圖5 SignalTap處理后的邏輯圖(截圖)

[1]凌六一,伍龍.基于軟件模擬的51單片機IIC總線的實現[J].電子技術,2004(05):13-15.

[2]祝長鋒.肖鐵軍.基于FPGA的視頻圖像采集系統的設計[J].計算機工程與設計,2008,9(17):4404-4406.

[3]陳國柱,劉濤,李元宗.基于FPGA的圖像采集與存儲系統的設計[J].機械工程與自動化,2007,8(4):44-45.

[4]張國兵,孟令軍,李寶剛.CCD相機高速數據存儲系統中的無縫緩存技術[J].水電能源科技,2010,2(2):70-71.