音頻信號數字化光纖通信實驗系統的程序設計與實現

尹華山,孫 立

(南京航空航天大學 理學院,江蘇 南京 211100)

微電子技術的發展將數字電路技術推向一個新紀元,而在微電子領域中,可編程邏輯又擔任著重要角色。如今,幾乎所有的數字產品的開發都離不開可編程邏輯技術(PLD)。基于PLD技術的重要性,有必要在我國高等院校本科階段的課程實踐環節引入更多與之相關實驗教學。考慮到在當代通信領域,信號基本都以數字形式進行處理,若將通信與PLD技術相結合設計一套數字電路實驗教學設備,不失為一個不錯的方案。

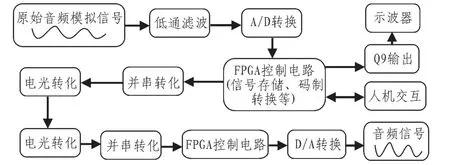

1 儀器的基本構架

本實驗儀以音頻信號數字化光纖通信作為演變處理與測試內容,囊括了數字電路技術的A/D與D/A轉換技術、串化解串技術、編解碼技術、數字信號傳輸以及PLD技術。從功能上劃分,系統包括音頻發生電路,抗混疊濾波電路,FPGA控制電路,串化/解串電路,電/光與光/電轉化模塊及音頻功放模塊等,如圖1所示。

圖1 音頻信號傳輸系統構架圖Fig.1 Audio signal transmission system frame diagram

該系統的FPGA控制芯片采用Altera公司cyclone系列芯片EP1C6T144C8,用Verilog語言編寫[1-2]。文中重點介紹該系統中FPGA控制電路邏輯程序語言的設計構思與編制方法。

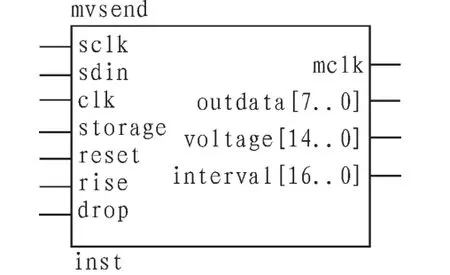

2 信號采樣與數據緩存

采用12位串行輸出的A/D芯片,圖2中sdin為數據輸入端,sclk是對應的數據讀取時鐘,上升沿有效。clk是發送端系統時鐘,由外部晶振提供。該部分分兩條工作路線,一條傳送音頻信號,由sdin串行輸入,再經outdata[7..0]并行輸出,一條檢測信號頻率并在storage置低(按下存儲鍵時)的情況下開始從10個周期中均勻時間間隔地抽取160組數據并按先后順序存儲。每次按下上鍵(或下鍵)時,后一位數據(或前一位數據)便分別從 voltage[14..0](電壓值)和 interval[16..0](時間間隔)輸出,提供給下一級處理[3]。

圖2 A/D采樣與數據處理Fig.2 A/D sampling and data processing

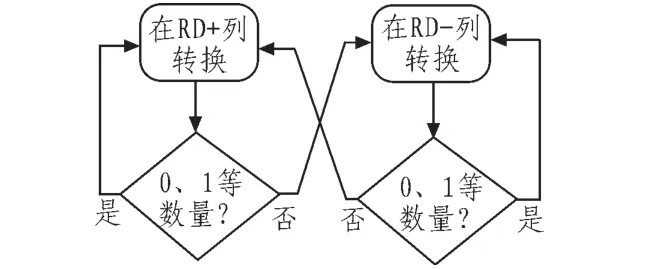

3 8B/10B編解碼

8B/10B編碼(以下簡稱8B/10B)作為一種高性能的串行數據編碼標準,其基本思想是將一個字節寬度的數據經過映射機制(Mapping Rule)轉化為10位寬度的字符,但是平衡了位流中0與1的個數,也就是所謂的直流平衡特性。同時規定位流中0或1的游程長度(Run Length)的最大值不能大于5,以使得傳輸過程保持足夠高的信號變換頻率,這樣不僅確保了時鐘恢復也使信息流的直流頻譜分量為零或近乎為零,而正是這些特性使得8B/10B編碼特別適合光纖等介質的連接和信息傳輸[4]。

3.1 8B/10B編碼原理

8B/10B可以看做是5B/6B和3B/4B編碼的組合,組合后有些編碼可能有兩個值,“1”和 “0”的差值稱為平衡度,用RD-表示平衡度+2和0,用 RD+表示平衡度-2和 0,將轉換后的數據按平衡度分為RD-和RD+兩列。若設DISPIN表示正在轉換的數的平衡度,DISPOUT表示下一個數的轉換的平衡度。起初設兩者相等,先從RD-列開始轉換,如果轉換后“1”和“0”的數量相等,繼續在 RD-列中轉換下一個數,如果不等,則轉到RD+列中轉換。同樣若在RD+列中轉換后二者數量相等,則繼續在該列中轉換,否則轉到RD-中轉換[5]。

圖3 8B/10B編碼流程圖Fig.3 8B/10B code flow chart

3.2 8B/10B編碼的FPGA設計

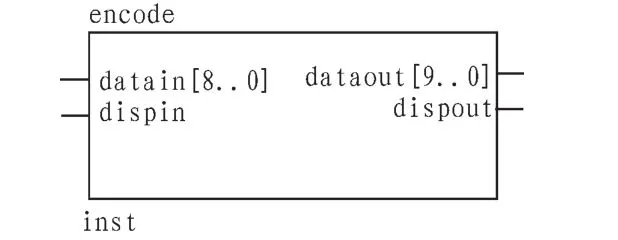

8B/10B編碼模塊圖設計[6]構思如圖4所示。datain[8:0]為編碼數據輸入引腳,其中的datain[4:0]為5B/6B編碼數據輸入端,datain[7:5]為3B/4B編碼數據輸入端。datain為控制字符編碼標示位,為1表示為控制字符編碼,為0表示為數據字符編碼。dispin為8B/10B編碼前的RD輸入引腳;dispout為8B/10B編碼后的RD輸出引腳。dataout[9:0]為編碼數據輸出引腳。

圖4 8B/10B編碼模塊圖Fig.4 8B/10B coding module chart

4 數字信號輸出

經過權值計算處理得到的信號電壓值與基礎時間間隔的數字信號分兩路輸出,一路直接在液晶屏上顯示電壓值大小,一路經過自然二進制碼、8421BCD碼、4221BCD碼等碼制轉換后,由數字信號輸出(儀器的Q9端口)給外部示波器進行邏輯分析,讀取數值大小,比較與液晶屏上顯示的數值的對應關系。

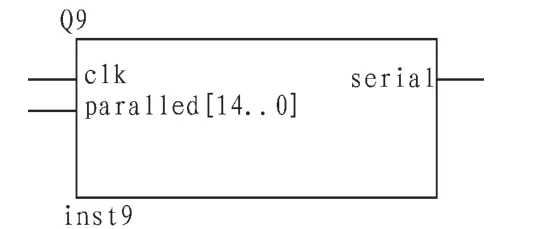

圖5 數字信號輸出(Q9輸出)端口Fig.5 Digital signal output(Q9 output)port

如圖5所示,clk為時鐘輸入,paralled[14..0]為并行輸入端,serial為串行輸出端。由于示波器有幾種觸發方式,比如脈寬觸發、上升沿觸發、下降沿觸發等,為了使一組數據在示波器中顯示出穩定的波形,需選定一種觸發方式。考慮到通用性使用方式,一般選擇脈寬觸發,故serial的數據前端還要設計插入一個單觸發脈沖信號,用于示波器重復掃描獲得的起始觸發脈沖。

5 BCD碼制轉換

常見的BCD碼有8421碼、5421碼、4221碼、格雷碼、余三碼等。為方便起見,系統只進行由自然二進制碼向8421碼、4221碼及5421碼有權BCD碼的轉換。由于8421碼、4221碼和5421碼之間的轉換相對簡單,直接查表即可,故不贅述。而自然二進制碼到8421碼轉換的硬件實現則相對復雜,程序設計實現如下:

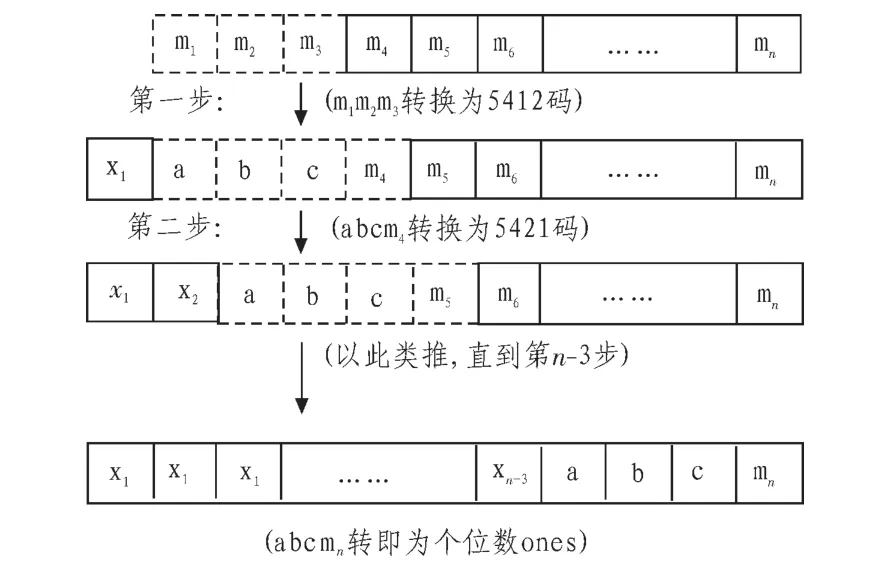

首先假設原自然二進制碼m有n位,從右往左依次遞增,即最低位為第1位。第一步將n、n-1、n-2三位進行5421碼轉換,取第n+1位作為進位位,1代表數值,然后加入下一位即第n-3位,此時一共構成5位,最高位x1則代表數值10,低四位(n、n-1、n-2、n-3 位)為 8421 碼;第二步,將第一步中得到的低四位進行5421碼轉換,然后同樣加入下一位即:

第n-4位,此時又構成5位,最高位x2代表數值10,低4 位(n-1、n-2、n-3、n-4 位)構成 8421 碼;以此類推,依次進行第三步、第四步……一直到第n-3步,并分別得到x1,x2,x3,……xn-3,以及所需要的個位數ones(第n-3步中得到的低4位),如圖 6 所示。 x1,x2,x3,……xn-3再次構成自然二進制碼 x1x2x3……xn-3,按照同樣方法,可得到所需要的十位數tens,百位數hundreds,以及千位數thousands。

圖6 自然二進制碼向5421碼的轉換Fig.6 Natural binary code to 5421 code conversion

6 液晶顯示控制

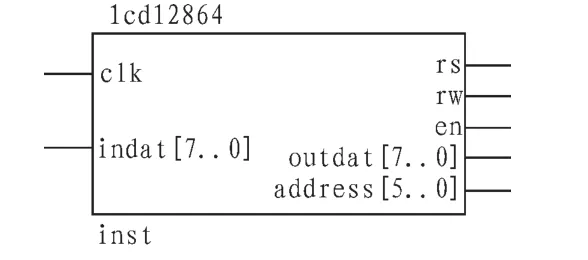

采用12864型液晶屏,其控制時序較為簡單。用單片機軟硬件結合形成的控制方法來實現較為普通,但設計用可編程邏輯芯片FPGA形成的全硬件電路實現則有相當復雜的技術難度。另外,由于顯示的文字(漢字與數字)較多,而調用了ram存儲器,增加時序關系的復雜性。圖7為液晶時序控制的邏輯實現模塊,clk為系統時鐘,連接外部晶振,進入后再由分頻模塊對其分頻,以降低寫入頻率。address[5..0]連接至ram的讀地址端,indat[7..0]連接至ram的數據輸出端,在en使能時,由outdat[7..0]將數據輸出給液晶屏。

圖7 液晶顯示時序控制模塊Fig.7 Liquid Crystal Display(LCD)sequential control module

ram存儲器的基本構成有6個輸入端和一個輸出端。6個輸入端中,兩個分別為讀時鐘 (rdclock)和寫時鐘(wrclock), 另外兩個分別為讀地址 (rdaddress)和寫地址(wraddress),其 余 兩 個 為 數 據 輸 入 端 (data[7..0])和 使 能 端(en)。 輸出端為數據輸出(q[7..0])。

7 結束語

以上主要描述在硬件電路采用FPGA芯片環境下,實現音頻數字信號的采集與傳輸的實時處理,幅度與頻率的測量方法,8B/10B編碼、BCD碼制轉換、數字信號輸出處理以及液晶屏時序控制等設計原理與技術處理。

科技進步使人類已經進入信息化時代,其中的數字技術是最重要的標志之一。而數字技術迅速發展與不斷變化,讓當今人們感到目不暇接,日新月異。而目前國內大學的許多基礎性教學內容,還停留在過往的模擬體系內容中,這與現實的狀況和發展的需要,嚴重地相脫節與背離。本實用新型實驗儀的研制成功,不僅集現代電子技術與數字通信技術的特點與優點于一身,而且在對音頻信號數字化處理及數字信號光纖傳輸方面,具有獨特的教學示范效果。它可以引導實驗者,由淺入深的教學實踐和深入淺出的漸進式學習。不僅可以深刻認識模擬變量與數字變量,以及二者在形式上的區別與內在的相互關聯;而且可以深入了解二者之間的自然演化與時代變遷,在技術進步與科技發展上面對人類帶來的巨大作用、深刻影響和長遠意義。不僅可以獲得現代通信技術的基本概念與基礎理論等初步知識;而且提升了實驗儀器的技術水平和豐富了實驗教學科目的內容。在國內大學的基礎實驗教學領域是首次研制出的實驗用儀器,填補了這一領域的應用空白。

[1]羅杰,康華光.兩種硬件描述語言VHDL/Verilog的發展及其應用[J].電氣電子教學學報,2002,24(4):4-5.

LUO Jie,KANG Hua-guang.The development and application of two hardware description languages-VHDL/Verilog[J].Jounual Electrical&Electronic Education,2002,24(4):4-5.

[2]蔣敬旗,劉明業.芯片設計方法學的基礎——硬件描述語言Verilog[J].計算機輔助設計與圖形學學報,2002,14(11):1092-1095.

JIANGJing-qi,LIUMing-ye.Thebasisofchipdesignmethodology verilog hardware description language[J].Journal of Computer-Aided Design&Computer Graphics,2002,14(11):1092-1095.

[3]尹作友.數據采集系統中碼制轉換的處理方法[J].錦州師范學院學報:自然科學版,2002,23(1):45-47.

YIN Zuo-you.The method for resoluing code convert in data collecting system[J].Journal of Jinzhou Teachers College:Natural Scienec Edition,2002,23(1):45-47.

[4]李欣,管紹軍,胡曉天.基于FPGA的光纖通信系統的設計與實現[J].電子設計工程,2012,20(8):86-87.

LIXin,GUANShao-jun,HUXiao-tian.Designandimplementation of optical fiber communication system based on FPGA[J].Electronic Design Engineering,2012,20(8):86-87.

[5]錢皓,成龍,孫立,等.音頻信號數字化光纖傳輸實驗儀信道的設計與實現[J].電子設計工程,2012,20(12):84.

QIAN Hao,CHENG Long,SUN Li,et al.Design and realization ofaudiosignaldigitizationopticalfibertransmissionexperiment instrument channels[J].Electronic Design Engineering,2012,20(12):84.

[6]戴居豐,賀傳峰,毛陸虹.一種新的光纖通信8B/10B編解碼實現方法研究[J].電路與系統學報,2005,10(2):30-33.

DAI Ju-feng,HE Chuan-feng,MAO Lu-hong.Study on a new implementing method of 8B/10B encoding and decoding for fiber communication[J].Journal of Circuits and Systems,2005,10(2):30-33.