面向遙感圖像高速壓縮的多FPGA處理器設計

徐瀟審 姜宏旭 肖朝升

(北京航空航天大學 計算機學院,北京100191)

隨著遙感技術的飛速發展及空間傳感器分辨率的不斷提高,遙感數據量成倍增加,已達到Gbit級甚至更高的計量單位;此外,遙感設備在空間環境溫度、氣壓、宇宙射線等因素的影響下,故障率較高.針對上述應用條件,遙感圖像壓縮處理系統應具備高效處理、可靠運行、高速通信3個基本要求.目前實現圖像壓縮的硬件處理系統可分為3類:①采用全定制專用集成電路(ASIC,Application Specific Integrated Circuit),它對算法進行單獨硬件處理,具有外部RAM和外圍接口,能獲得良好的處理效果,滿足高速通信的要求,現有圖像處理ASIC芯片(如AD公司的ADV212)得到了很好的應用[1],但無軍品級和宇航級,可靠性方面存在隱患,不適合用于遙感設備;②采用通用數字信號處理(DSP,DigitalSignal Processing),DSP具有先進的哈佛和流水結構,適于計算的乘加單元和優化的內部結構設計,使其得到了優異的處理性能,是遙感壓縮中較好的解決方案[2],但由于 DSP外圍接口性能的限制,DSP間的數據交互以及任務分配協調困難,難以滿足高速通信的要求;③采用半定制現場可編程門陣列(FPGA,Field-Programmable Gate Array),FPGA相當于可編程ASIC,又比DSP內部資源豐富,可以達到較大的數據吞吐量,且保密性好,適合于遙感壓縮設備,但現有的FPGA方案[3-4]多為特定的結構,只解決了中低數據量的快速壓縮,無法滿足海量遙感圖像的高速壓縮應用要求.

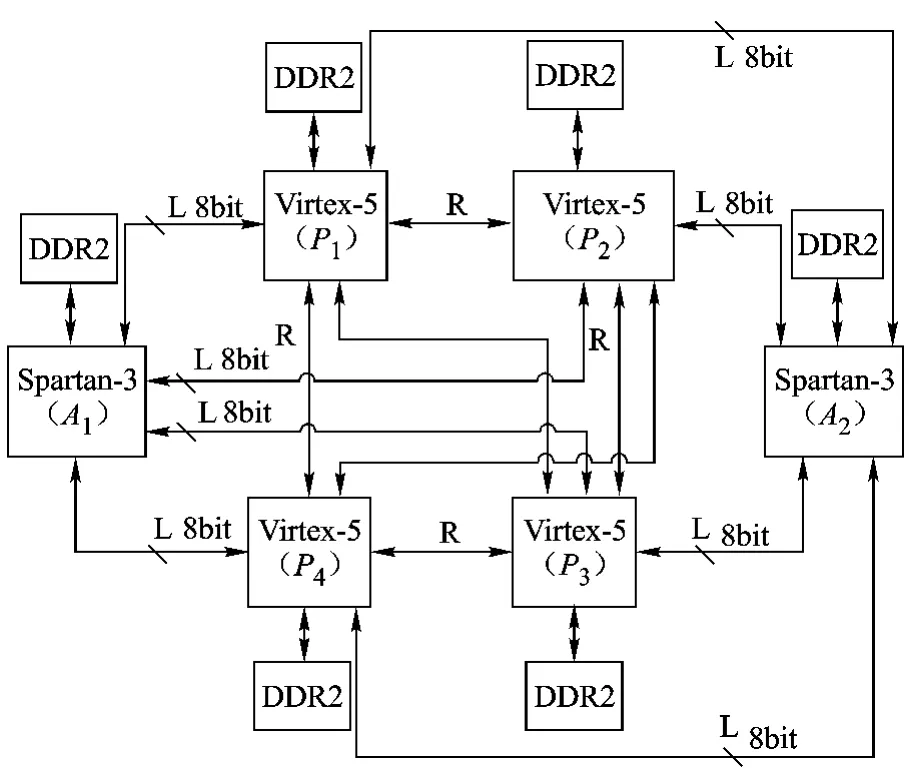

因此,本文提出一種基于多FPGA的壓縮處理器結構,包括 4片 Virtex-5 FPGA和 2片Spartan-3 FPGA,針對該結構分別給出了高并行壓縮處理機制、容錯性設計以及高速通信策略.并將此結構應用于遙感圖像高速壓縮系統中,壓縮性能達到1.6 Gbit/s以上.

1 遙感圖像壓縮任務概述

海量遙感圖像壓縮任務需采用高速高保真的壓縮算法.壓縮算法應盡可能地保持圖像細節,保證弱小目標不丟失,同時應結構簡單、易于硬件流水和并行處理,具體采用基于小波變換和基于上下文的位平面預測編碼并算術編碼的壓縮算法[5].該算法一方面利用基于小波域中紋理失真敏感性模型的視覺量化方法,不均勻量化各頻帶各系數塊,提升了恢復圖像的主觀質量;另一方面通過改進位平面預測模型,利用系數塊內及塊間的多維相關性,進一步提升了熵編碼的效率.因此,在高倍壓縮條件下與JPEG2000相比,該算法能夠實現目標無畸變、無明顯失真、小目標不丟失,能將PSNR值提高0.5~0.7 dB.另外,由于采用了定點化的小波變換和無乘操作的熵編碼,該算法僅有簡單的整數運算和移位操作,壓縮速度快、易于數字邏輯電路高速實現.

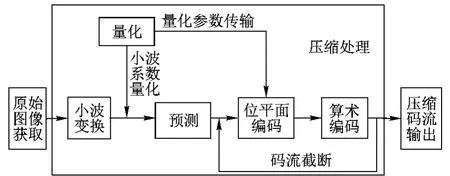

基于上述算法的遙感圖像壓縮任務從功能上可劃分為數據獲取、壓縮處理和碼流輸出3個模塊,壓縮處理模塊又可分為小波變換、量化、預測、位平面編碼和算術編碼5個單元,如圖1所示.

由圖1可得知,該遙感圖像壓縮任務具有2個特點:①3個模塊的處理任務是串行執行,模塊間耦合性弱;②壓縮處理模塊執行步驟復雜,各單元間數據關聯性強,通信重疊性高.

圖1 海量遙感圖像壓縮處理任務的處理流程

2 多FPGA壓縮處理器設計

2.1 總體解決方案

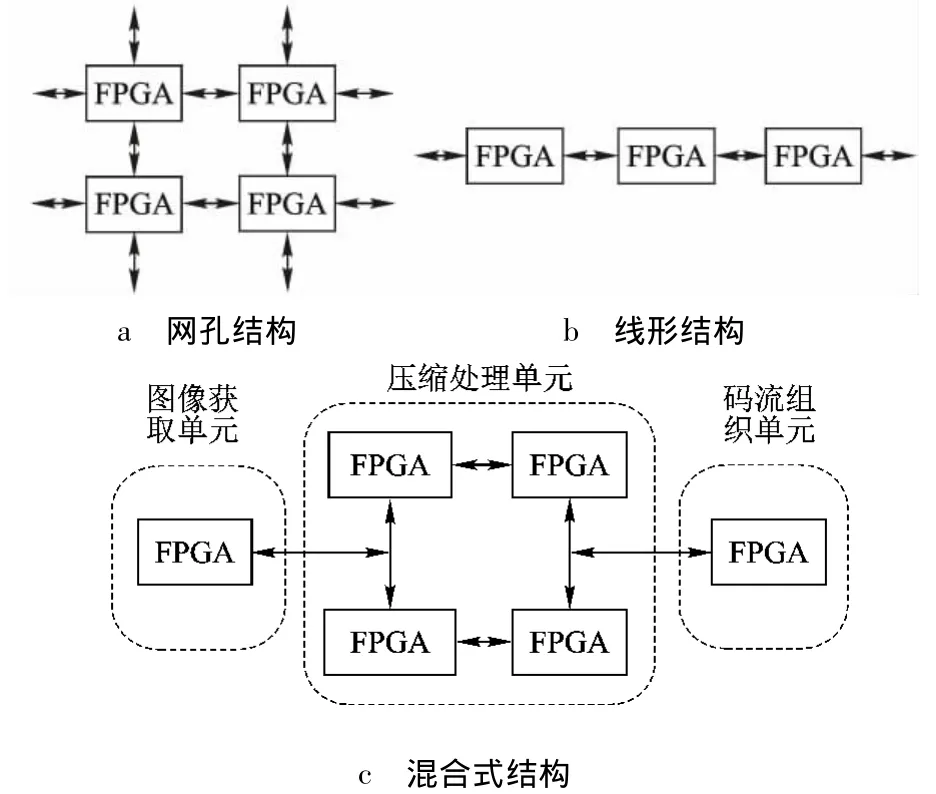

針對上述特點,考慮到單個FPGA處理器難以完成海量遙感圖像高速壓縮的實際情況,較優的方案是采用多FPGA并行壓縮.在多FPGA處理器的連接方式方面,經典的并行結構包括網孔、線形、樹形、星形等,每種結構適配于不同種類的壓縮算法.網孔結構[3](如圖2a所示)具有較好的擴展性,任務并行度高,但遙感圖像壓縮3個任務模塊耦合性弱,特別是圖像獲取和碼流輸出2部分很難進行任務劃分,只能由單個FPGA處理,采用此結構會造成任務分配不均衡,出現并行等待現象;而線形結構[4](如圖2b所示)中,多處理器單元針對性強,模塊化高,資源可有效利用,從而達到良好的加速效果,但是難以滿足遙感圖像壓縮處理模塊內數據關聯性強、通信重疊性高的特點,若采用此結構會加大芯片級的通信開銷,通信路徑長,降低壓縮處理效率.

圖2 多FPGA并行計算體系結構

結合網孔結構并行度高和線形結構針對性強的共同特點,設計了一種混合式的多FPGA處理器結構,如圖2c所示.共由6片FPGA組成,其中圖像獲取、壓縮處理和碼流組織3個處理單元線形連接,適合壓縮任務中模塊間耦合性弱的特點;并將壓縮處理單元設計為網孔結構,采用4片同構FPGA,每片同構FPGA執行整個壓縮處理算法,使各單元在FPGA片內直接通信,解決了壓縮任務中壓縮處理模塊內各單元間數據關聯性強的問題,4片FPGA并行實現對海量遙感數據的高速壓縮.為了便于描述,碼流獲取FPGA簡稱為A1,碼流組織FPGA簡稱為A2,4片處理FPGA統稱為 FPGA-P,分別簡稱為 P1,P2,P3,P4.

混合式處理器結構的解決方案滿足了遙感圖像壓縮任務模塊間耦合性弱及壓縮處理模塊內關聯性強的特點,但是要實現海量數據的高速可靠壓縮,仍需在軟件層考慮多處理器的高并行調度機制;在硬件層考慮結構間的容錯性設計;在通信接口層考慮海量數據的高速通信策略.針對以上3方面內容,分別逐一介紹.

2.2 高并行壓縮處理機制

使用多處理器的目的是為了獲取高并行,如何將海量數據壓縮任務分配到多處理器并行處理并合理回收是高并行壓縮處理機制的設計難點.

高并行的關鍵就是讓并行處理器達到負載均衡,針對混合式多FPGA的結構特點,較優的負載均衡策略是讓4片同構FPGA運行相同的壓縮算法,同時處理相同的數據量,所以需要對遙感圖像進行平均分配;為了保證解壓后圖像拼接的正確性,壓縮后碼流的輸出順序還必須與壓縮前數據拆分順序一致.為此給出了高并行壓縮處理的兩條規則:數據的均衡分發和碼流的規則回收.

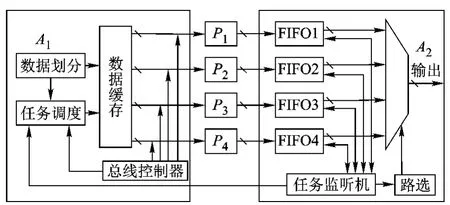

遙感數據均衡分發流程如圖3所示,A1作為數據分發處理器來實現數據的分發調度以及傳輸功能.圖像數據進入A1之后,存入數據緩存中,數據劃分模塊按照一定的策略對圖像數據進行塊大小平均劃分,任務調度模塊接著對劃分后的數據塊順次調度,并通知總線控制器將數據傳送至FPGA-P進行壓縮處理.

圖3 數據均衡分發與順序回收示意圖

碼流的順序回收由A2完成.在此過程中,4片FPGA-P是按照異步方式將碼流傳入A2,但傳入時鐘初始時刻并不確定,因此在A2內采用FPGA內嵌異步軟先入先出隊列(FIFO,First Input First Output)的機制來進行數據回收,實現4路數據的時鐘鎖相功能;另外,對于固定尺寸的圖像塊而言,遙感壓縮算法的處理速度略有不同,高頻信息豐富的圖像處理速度稍快[5],為了保證并行同步性,任務監聽機通過監聽FIFO內的數據量來判斷4片FPGA-P的運行情況,并通過反饋信號通知A1中數據調度模塊,對數據分發時序進行微調,實現整個過程的閉環;最后,路選根據當前任務的完成情況,按照順序將碼流依次輸出,這樣便形成了基于軟FIFO的閉環回收機制.

此并行機制針對混合式多FPGA處理器的結構特點,將數據進行平均分配,發揮同構FPGA的資源利用率,提高并行效率;基于異步軟FIFO的回收機制保證了碼流回收的同步性和一致性,使整個壓縮處理過程具有高效并行性.

2.3 結構容錯性設計

在混合式多 FPGA處理器中,具有 6片FPGA,FPGA間具有多條通信鏈路,連接相對復雜,在結構容錯性設計中,應充分分析其可能故障情況,保證系統可靠性.

FPGA-P作為處理器結構中的主處理器,其故障模型有2種:一種是處理器故障(本文只討論處理器完全失效,且FPGA重構程序不能恢復正常性能的情況),另一種是鏈路故障.當處理器出現故障時,需要考慮的是刪除故障結點,并保證其它結點正常工作;當鏈路出現故障時,應設計冗余鏈路,保證數據的傳輸通路.

根據以上2點考慮,將4個FPGA-P的連接設計為獨立鏈路來解決鏈路故障問題,并將FPGA-P間設計為全連通的連接方式,用以鏈路故障后的橋接通信.用無向圖模型表示多處理器的連接方式,如圖4所示.設圖 G=(V(G),E(G))表示多處理器互連網絡,V(G)表示處理器集,稱為結點集,E(G)表示通信鏈路集,稱為邊集.處理器單元稱為結點,而通信鏈路稱為邊.

圖4 多FPGA處理器級聯抽象圖模型

采用確定性方法[6]通過網絡拓撲結構的連通度評價多處理器系統的容錯性.對于一個特定的多處理器互連網絡,用G表示,假定其連通度為k(G),則該多處理器互連網絡最多可以允許k(G)-1個處理器發生故障,此時互連網絡的連通性仍然可以保證.如圖4所示,用k(G)表示圖G的連通度,則k(G)=4.由于4個FPGA-P結點都與 A1,A2結點連通,所以,任意刪除某個FPGA-P結點,仍然可以保持系統連通性,其代價是系統性能降低.例如刪除圖4中的P1,P2和P3三個結點,結點 A1,P4,A2依然保持連通,其連通度k(G)=1,系統處理性能為原有性能的1/4,可以保證對較慢速率或部分圖像數據的壓縮處理.另外,由于FPGA-P結點間兩兩相連,若刪除與A1或A2相連的某條邊,其對應結點可以利用其它節點作為通信橋接來保證其連通性,此時FPGA-P結點正常工作,處理性能基本沒有變化.

結構容錯性設計同時解決了處理器故障和鏈路故障兩個問題,使系統在正常工作的同時盡量保證處理性能,提高了系統可靠性.

2.4 FPGA高速通信策略

在遙感圖像高速壓縮過程中,FPGA需要對數據進行頻繁的組織、搬運和計算,只靠有限的片內空間無法滿足海量數據的處理要求,必需借助片外存儲器來實現.這便引出了FPGA高速通信的2個設計難點:FPGA與外部存儲器的高速通信方式以及FPGA之間的高速通信接口.

利用片外存儲器進行通信的方式有2種:共享存儲系統和分布式存儲系統.共享存儲系統是指多片FPGA共用一套總線和共用外部存儲器,分時使用存儲器,系統雖然節約了成本和功耗,但是難以實現多FPGA與存儲器的頻繁通信,導致通信等待,造成性能下降;分布式存儲系統是指每個FPGA具有獨立的總線和存儲器,存儲器服務于指定FPGA,較大程度的發揮了存儲性能.因此,針對遙感圖像高速壓縮中頻繁通信的特點,對6片FPGA分別采用獨立外部存儲芯片DDR2 SDRAM以提高通信效率.

在FPGA間的通信方面,必須有靈活高效的通信接口才能滿足海量數據的高并行壓縮,容錯性設計中的鏈路橋接設計致使每條鏈路至少達到兩或多路的數據通信要求.目前常用的TTL電平并行總線技術由于總線間串擾和外部干擾,限制了實際的傳輸速率和可靠性;而低電壓差分信號(LVDS,Low-Voltage Differential Signaling)串行總線技術采用3.5mA的恒流源模式驅動信號發送,保證了信號穩定性,具有傳輸速度快、抗干擾能力強的特點,單路 LVDS信號最高傳輸速率可達400 Mbit/s,更適合高速鏈路通信;另外,Xilinx公司所推出的RocketIO技術[7]采用兩對差分對來實現Gbit級的速度傳輸,在滿足通信性能的同時,還保證了PCB布線規模.因此,采用LVDS串行總線和RocketIO技術共同實現FPGA間高速數據通信,其連接方式如圖5所示.

圖5 FPGA間通信接口示意

考慮遙感圖像壓縮任務的處理規模和成本,采用兩片Xilinx公司一般性能的Spartan-3 FPGA分別實現圖像獲取與碼流組織2個任務,采用4片Xilinx公司高性能的Virtex-5 FPGA實現高速壓縮任務.其中,Spartan-3與 Virtex-5之間采用LVDS的傳輸方式,4路總線相互獨立,互不影響,每路采用8對串行差分對總線,按照150 MHz時鐘計算,每路速率可達到1.2 Gbit/s(150 MHz×8 bit);4片Virtex-5之間采用全連通的RocketIO連接方式,兩兩之間具有一組RocketIO通道,可以進行全雙工的串行差分傳輸,通信速率達到1.25 Gbit/s.

各FPGA獨立DDR2存儲器的設計滿足了壓縮處理器與外存頻繁通信的要求,FPGA間2種通信接口均可達到1 Gbit/s以上的通信速率,保證了海量遙感圖像壓縮中的高速數據通信.

3 結果與分析

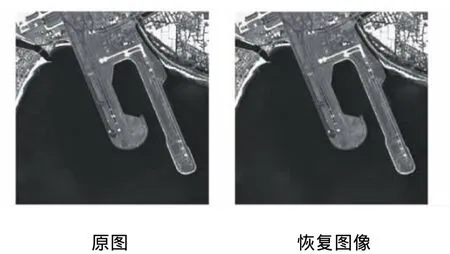

3.1 遙感圖像壓縮效果

設計專用的遙感圖像發送卡,模擬遙感相機的數據格式對以多FPGA實現的硬件系統進行測試,采用基于小波變換和基于上下文的位平面預測編碼并算術編碼的壓縮算法,壓縮倍率16∶1,圖6是測試圖像與解壓圖像片段的對比結果.

通過與壓縮算法的軟件實現進行比較,硬件系統的壓縮結果與軟件結果完全一致,恢復圖像相比原圖無視覺失真,不同的測試圖像計算平均PSNR(峰值信噪比)值在33 dB以上.

圖6 測試圖像與解壓圖像

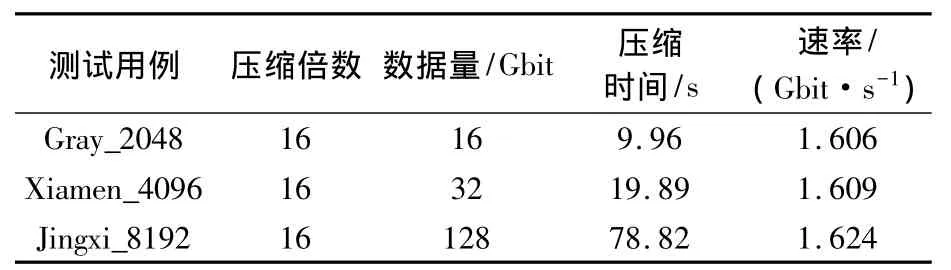

3.2 壓縮性能測試

測試壓縮處理單元中4片Virtex-5 FPGA的并行性能.使用1片Virtex-5對16 Gbit大小的遙感測試圖像進行壓縮,記錄壓縮耗時為37.24 s,同時使用4片Virtex-5對相同的測試數據進行壓縮,記錄壓縮耗時為 9.96s,根據 Amdahl[8]定律得出:4個Virtex-5的并行處理加速比Sp=T1/Tp=37.24/9.96=3.74倍,平均每個Virtex-5的并行效率Eff=Sp/p=93.5%.

對以多FPGA實現的硬件系統進行整體壓縮性能測試.通過遙感圖像發送卡發送不同數據量的遙感圖像測試數據,分別記錄壓縮處理時間,得出整體壓縮性能,測試結果如表1所示.可見,不同數據量的遙感圖像測試用例,其壓縮時間與數據量成正比關系,系統的整體壓縮性能穩定在1.6 Gbit/s以上.

表1 整體壓縮性能測試結果

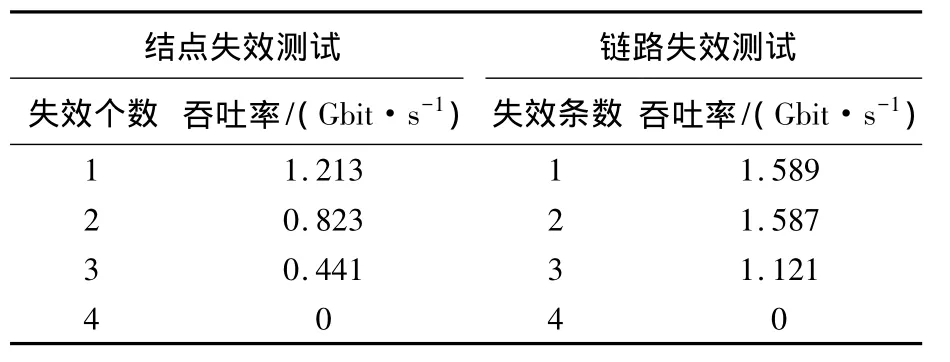

3.3 系統容錯性

使用確定性方法在理論上分析多FPGA處理器結構容錯性能,具體見本文2.3節,本節通過實驗測量的方法評測系統容錯性指標.根據故障模型的不同,設計壓縮處理單元中FPGA(FPGA-P)結點失效和鏈路失效2種用例,測試遙感壓縮系統數據吞吐率,如表2所示.

表2 系統容錯性測試結果

由表2可見,結點失效后系統可以正常工作,但性能與正常處理器的個數成正比;根據2.4節可知,每條鏈路的傳輸速率為1.2 Gbit/s,所以當失效3條之后處理性能下降較大,而鏈路在失效2條之內時,整體性能較為穩定.本文所設計的多FPGA處理器同時支持處理器故障和鏈路故障的容錯,系統可靠性強.

4 結論

本文設計了一種適用于海量遙感圖像高速壓縮的多FPGA處理器結構,根據遙感圖像壓縮任務中模塊間松耦合和模塊內強關聯的特點,采用6片FPGA芯片,給出數據均衡分發和基于FIFO的閉環回收機制,實現了處理器結構的容錯性設計,利用外部存儲方式提高了通信效率,并通過LVDS與RocketIO兩種連接方式保證數據傳輸吞吐量.應用測試結果表明:同構FPGA的并行效率達93.5%,壓縮處理板可達1.6 Gbit/s以上的處理速率,恢復圖像質量好,并具有較高的可靠性.

References)

[1]Hu H.A real-time high resolution image compression system based on ADV212[C]//2009 IEEE International Conference on Image and Signal Processing(CISP).Piscataway,NJ:IEEE Inc,2010:1-4

[2]葛寶珊,李波.基于多DSP的遙感圖像壓縮系統[J].計算機工程與設計,2007,28(21):5139-5140,5155 Ge Baoshan,Li Bo.Remote sensing image compression system based on multi-DSP[J].Chinese JournalofComputer Engineering and Design,2007,28(21):5139-5140,5155(in Chinese)

[3] Tao Qu,Cong Tang,Zhang Yuyu.The design and implementation of the core algorithm of embedded real-time image compression technology[J].Journal of Key Engineering Materials,2011,480/481:1618-1622

[4]熊君君,王貞松.星載SAR實時成像處理器的FPGA實現[J].電子學報,2005,33(6):1070-1072 Xiong Junjun,Wang Zhensong.The FPGA design of on board SAR real time imaging processor[J].Chinese Journal of Acta Electronica Sinica,2005,33(6):1070-1072(in Chinese)

[5]文義紅.面向遙感圖像壓縮的視覺量化與位平面編碼的算法研究[D].北京:北京航空航天大學計算機學院,2011 Wen Yihong.The study of visual quantization an bit-plane coding algorithms for remote-sensor image[D].Beijing:School of Computer Science and Technology,Beijing University of Aeronautics and Astronautics,2011(in Chinese)

[6] Bouriciusw G.Reliability modeling for fault to lerant computers[J].IEEE Tranctions on Computers,1971,C-20:1306-1311

[7] Virtex-5 family overview[DB/OL].San Jose:Xilinx Inc,2009[2009-02-06].http://www.xilinx.com/support

[8] Saripalli V.Exploiting heterogeneity for energy efficiency in chip multiprocessors[J].Emerging and Selected Topics in Circuits and Systems,IEEE Journal on,2011,1(2):109-119