一種采用硬件加速器的衛星導航接收機通用驗證平臺

陳 雷,黃仰博,葛 銳,歐 鋼

(國防科技大學 電子科學與工程學院,長沙 410073)

1 引言

隨著集成電路(integrated circuit,IC)設計規模日益增大,制造水平逐步提升,其仿真驗證成為了當前IC設計的主要瓶頸之一。硬件加速器強大的仿真速度和查錯能力使之成為大規模設計驗證的優秀解決方案之一[1]。縱觀全球,隨著全球定位、導航服務需求飛速增長,用戶對定位精度、接收機各方面性能都提出更高的要求。同時,包括北斗衛星導航系統(BeiDou navigation satellite system,BDS)、全球定位系統(global positioning system,GPS)和伽利略衛星導航系統(Galileo navigation satellite system,Galileo)在內的全球衛星導航系統(global navigation satellite system,GNSS)逐漸采用新型信號結構和新調制方式[2-3],這使得接收機基帶數據處理的通道數倍增。為了適應如同復合二進制偏移載波(composite binary offset carrier,CBOC)信號、時分二進偏移載波(time multiplexed binary offset carrier,TMBOC)信號、改進的二進制偏移載波(alternate binary offset carrier,AltBOC)等調制的新體制信號的接收[4-5],其捕獲跟蹤算法的復雜度也逐漸提高,這對接收機基帶處理芯片的設計提出了更高要求。當前,主流的集成電路功能仿真驗證方法依舊是動態模擬仿真,即產生測試向量,并將測試向量加載到設計上,通過硬件描述語言(hardware description language,HDL)模擬器得到測試結果。將這些結果與參考結果相比較,以此來驗證設計的正確性。然而,軟件模擬器進的仿真速度會隨著設計規模的急劇增大迅速降低。在PentiumⅣ的設計驗證中,Intel公司使用了6 000個節點的PC Farm進行仿真,而測試的向量不過相當于實際系統運行2min所執行的測試向量[6]。

隨著數字集成電路模塊化,設計由很多IP核(intellectual property core,IP Core)幫助完成,芯片功能日益復雜,芯片的 “流片”成本越來越昂貴,一次 “流片”甚至需要上百萬美元。為保證設計出的芯片性能是理想的,必須在流片前進行全面的有效的驗證。當前,IC設計已經實現了標準化,而驗證設計還沒有一個規范的標準,其效率和速度還有很大的提升空間。根據系統完備性計算公式,假設每個IP有一個缺陷且導致系統5%的缺陷,那么10個IP缺陷將導致整個系統的完備性降為(95%)10=59.9%。因此一個完備的仿真對于IC設計是至關重要的。

當前主流的仿真手段主要有:軟件仿真、硬件加速仿真器和現場可編程門陣列(field-programmable gate array,FPGA)在線仿真。軟件仿真主要依賴 ModelSim、NC-Sim、ISE-Simulation等工具,其特點是調試方便,可見波形數量多,采樣點數沒有限制,瀏覽方便,但速度較慢,目前只有kHz量級。FPGA在線仿真速度最快、價格較便宜,但對于調試和故障排查非常不方便,需要添加Chip-Scope抓取波形,每改一次抓取信號就必須重新編譯、布局、布線、生成二進制文件,對于稍微復雜的工程設計,一次流程就是幾個小時,且抓取波形數量、長度都受到器件和內核空間制約(最長只有131 072點)。這對于故障調試、信號分析非常不利。硬件仿真加速器兼具了以上兩種仿真方法的優點:調試方便、可見波形數量多、采樣點數沒有限制,可見波形長度沒有限制、不需要綜合布局布線,編譯上線快、仿真速度快(相對軟件仿真而言)通常在MHz級。對于設計師來說,最方便的是可以設置觸發條件(斷點),讓程序在仿真觸發條件滿足時暫停,并可從斷點處繼續運行,這是前兩種仿真手段所無法達到的,但其成本是三種仿真方法中最貴的。因此,中小規模的IC設計可以采用軟件仿真;而中大規模或團隊在多地點共同設計的情況更適合用硬件加速器[7]。本文所設計的驗證平臺主要采用Cadence公司推出的 Cadence?Incisive?Palladium?Ⅲ硬件加速器仿真器,其外形如圖1所示。

圖1 Palladium?Ⅱ加速器/仿真器

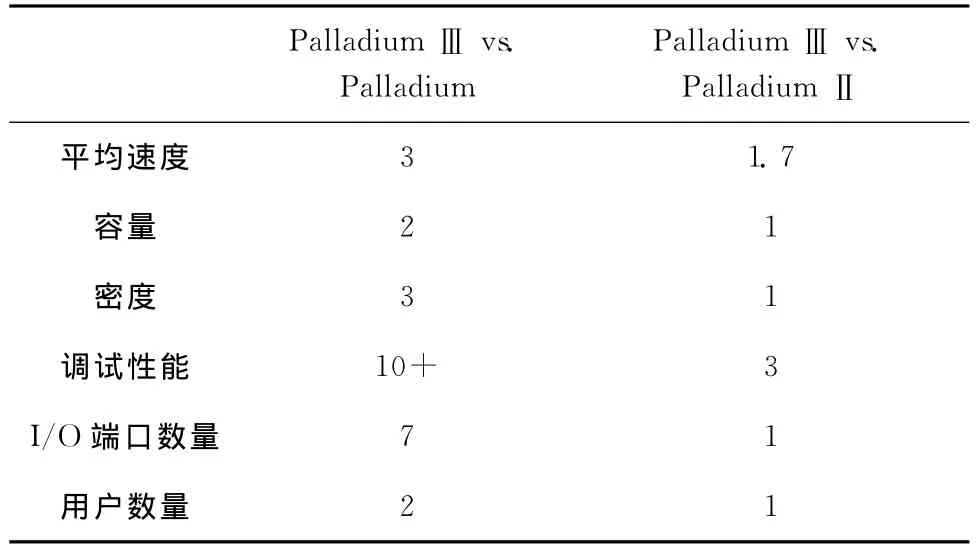

該仿真平臺是業界第一個結合了高性能系統級驗證自動化和驗證管理、快速設計輪轉,同時適合系統級芯片各個階段設計及驗證的硬件輔助驗證解決方案。實現了所有工程設計和功能驗證的硬件、軟件以及全系統確認的自動化[8]。如表1所示,相比PalladiumⅡ,PalladiumⅢ的運行時間性能提升近1倍,調試環境優越。復雜設計的仿真速度接近2MHz,比普通仿真的性能高100萬倍[8]。

表1 PalladiumⅢ與上一代系統的運行時間性能對比(倍數)[9]

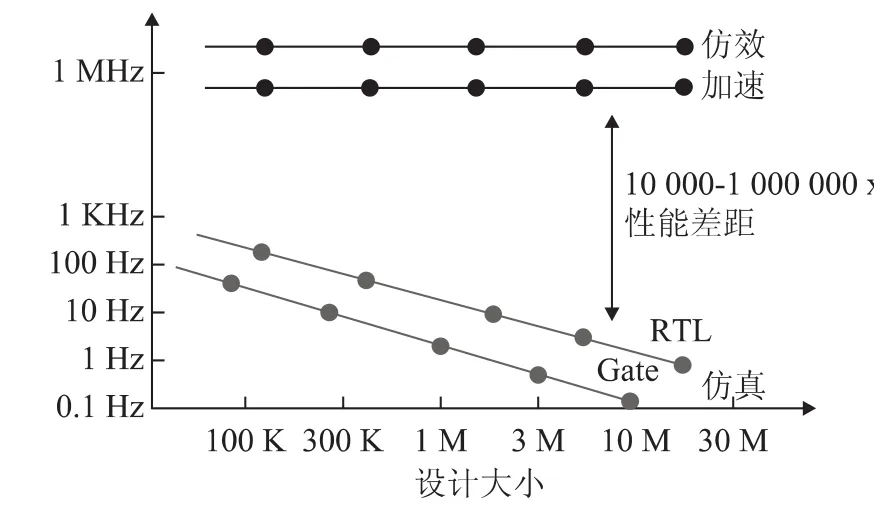

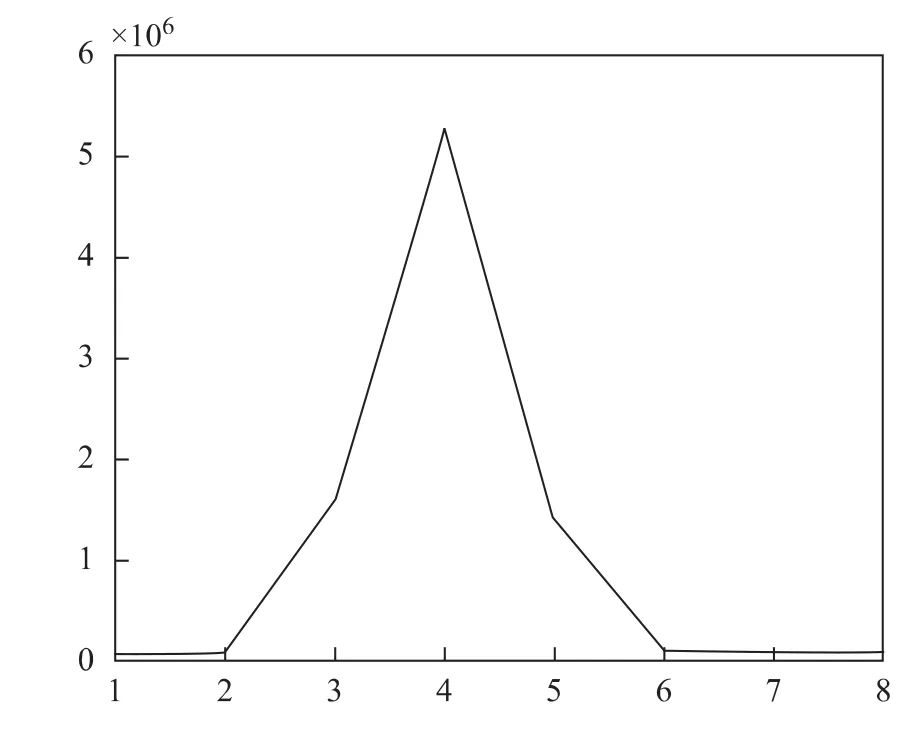

圖2給出了大系統仿真速率(emulation)和軟件仿真(simulation)隨著規模增大變化曲線[9]。由圖2可知,Palladium仿真時效性能并不隨硬件規模增大而降低,而傳統的仿真性能隨著規模增大成比例的下降。對于10MHz規模的IC仿真,Palladium仿真效率相對傳統仿真可提1 000萬倍。

圖2 大規模設計的在線仿真效能相比傳統仿真提升10 000~1 000 000倍

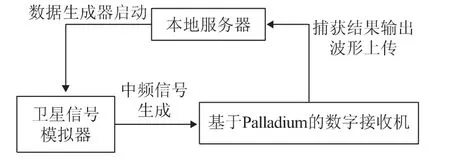

2 基于Palladium加速器的衛星導航接收機通用驗證平臺基本框圖

基于Palladium加速器的衛星導航接收機通用驗證平臺主要由本地服務器、衛星信號模擬器、Palladium硬件加速器組成。其基本框圖如下圖3所示:

圖3 衛星導航接收機通用驗證平臺基本框圖

其中本地服務器的主要功能是完成測試向量的配置、初始化參數設置、啟動控制Palladium設備上傳波形以及檢查確認。

衛星信號模擬器的主要功能是產生導航接收機所需要的各類導航衛星信號。特別的對于多體制導航接收機設計驗證,信號生成器可以模擬產生實時的GPS、Galileo的民用信號以及BDS的軍、民用衛星信號。并將產生的中頻或者基帶信號直接輸出給Palladium加速器中的待測模塊。

Palladium硬件加速器的主要功能是將測試工程導入設備,通過中央處理器(central processing unit,CPU)陣列模擬專用集成電路(application specific integrated circuit,ASIC)的基本單元,通過硬件電路實現邏輯功能的加速仿真驗證。并將測試狀態及結果實時輸出給本地服務器,并在觸發點處采集內部信號波形上傳。

3 基于Palladium加速器的衛星導航接收機通用驗證平臺運行策略

3.1 實時數據生成策略

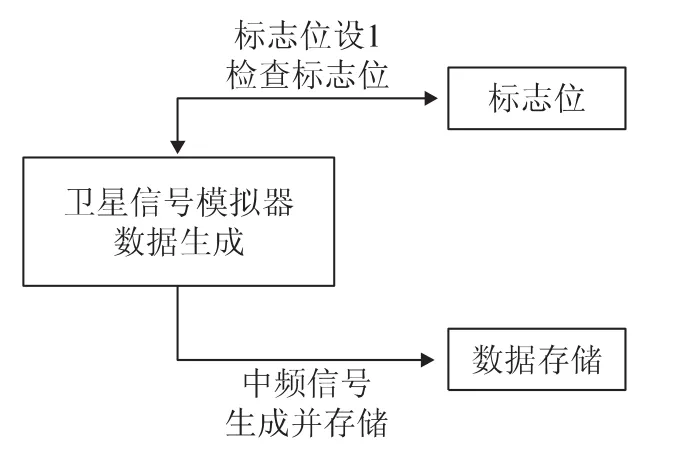

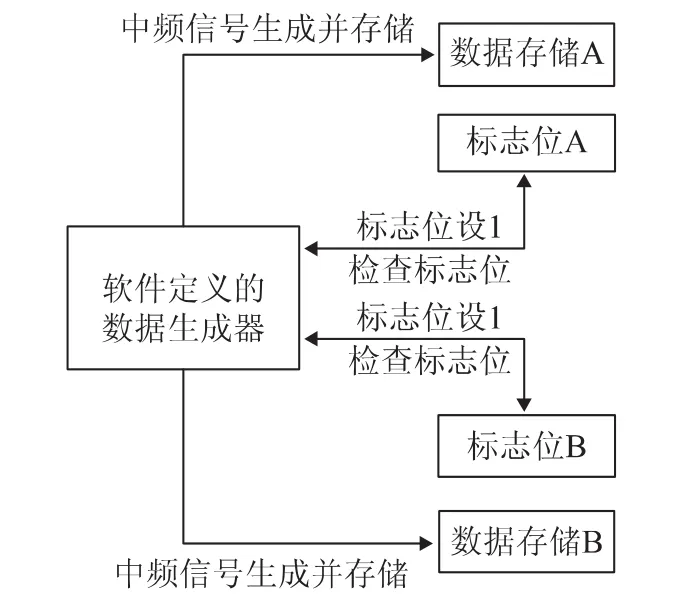

如圖4所示,實時數據生成策略是通過軟件定義的信號生成單元,配置衛星參數,啟動并生成1ms的BDS某顆衛星某頻點中頻信號的數據。

信號生成單元在存儲區設定標志位,當數據生成完畢并且未被提取存在的時候,標志位為1,生成器停止并等待數據提取;當數據被提取完畢后,標志位清除,數據生成單元繼續生成下1ms中頻數據。

圖4 導航衛星信號模擬單元實時數據生成策略示意圖

如圖5所示,由于數據生成需要一定的運行時間,等待數據提取也需要一定的時間,為了使輸入Palladium仿真器的數據保持連續,必須采取乒乓操作的策略。數據生成器設置2個1ms的數據存儲區A和B,當仿真器從存儲區調去數據文件A的同時,生成單元產生下一個1ms數據文件B,產生完畢后提示等待提取數據。前1ms數據文件A調用完畢并將標志位清0后,生成單元再產生下1ms數據生成并存儲于A文件。標志位A置1。仿真器讀完B文件后再切換到文件A。

圖5 數據生成單元乒乓操作示意圖

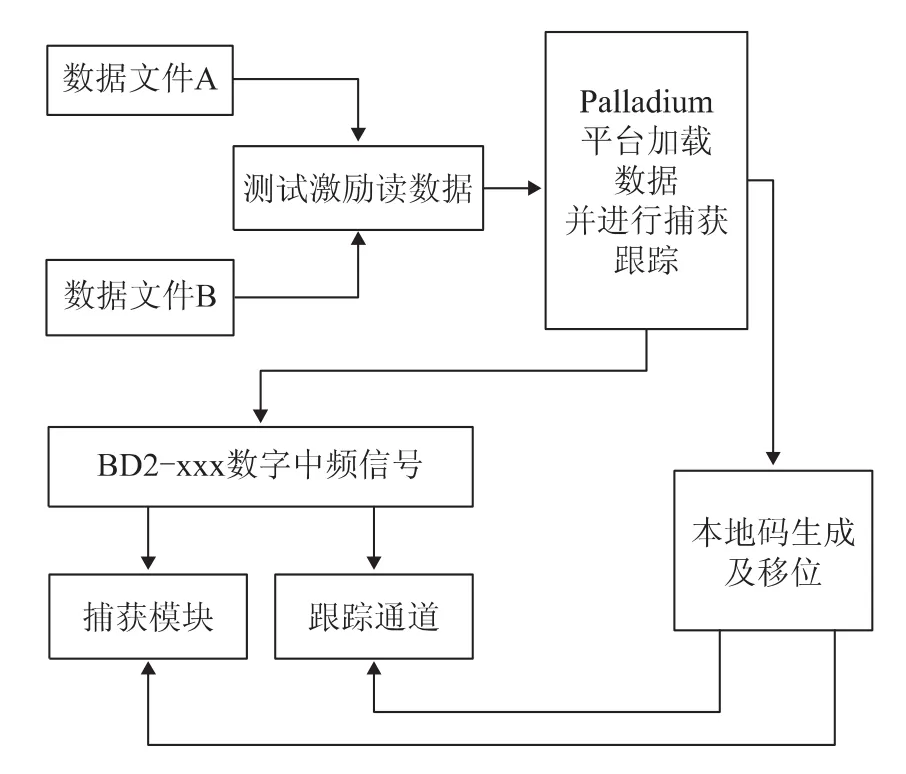

3.2 Palladium數據讀取策略

Palladium仿真驗證平臺數據讀取策略如圖6所示,Palladium讀取文件時,首先調用A文件,并將A文件中的數據置入仿真測試激勵中定義的虛擬隨機存取存儲器(random access memory RAM)中,通過測試模塊將數據輸入待測模塊。A文件數據讀取完畢后產生page_switch標志,調取文件B,并將A文件標志位清零。測試激勵讀入數據后,將數據分別送入捕獲模塊和跟蹤模塊。于此同時,本地碼生成模塊也將通過測試激勵將本地碼加載到捕獲跟蹤通道中。

圖6 Palladium仿真平臺數據讀取策略

其中,捕獲模塊通過移位相關累加后搜索最大值對應碼片,獲得捕獲結果,并將捕獲結果送入跟蹤單元,跟蹤單元轉換捕獲結果后進行精細跟蹤。具體算法及實現不在此贅述。

4 芯片仿真驗證流程與結果

4.1 芯片方針驗證流程

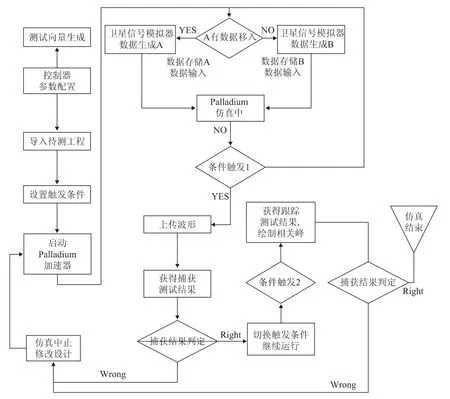

為了驗證芯片設計的功能和性能,有必要對芯片進行全面細致的仿真。正如引言中所述,任何一個細小的錯誤,其迭代的結果對系統完備性的影響是非差嚴重的,并且對于接收機芯片設計來說也是必須避免的。這就要求對芯片的功能仿真和性能仿真必須準確且完備。對于衛星導航接收機基帶芯片來說,有非常多的功能和性能項目需要仿真驗證,由于本文側重于介紹芯片研發所使用的Palladium仿真驗證平臺的設計,故在此僅對芯片仿真驗證的主要流程進行介紹,完備的功能性能驗證不在此贅述。采用Palladium硬件加速器的衛星導航接收機通用驗證平臺運行流程圖如圖7所示。

圖7 芯片仿真驗證流程圖

芯片仿真驗證的主要流程依次為:測試向量生成、控制器參數配置、導入待測工程、設置觸發條件、啟動Palladium加速器、數據移入(同時生成下一段數據)、Palladium仿真進行、捕獲觸發條件滿足后暫停、上傳波形、輸出捕獲結果、捕獲結果判定、啟動跟蹤、跟蹤觸發條件滿足、輸出數據并繪制相關峰、根據相關峰判定跟蹤結果。

4.2 具體驗證步驟

1)測試向量生成

測試激勵生成并會同待測模塊共同編譯。現實情況下的數字信號處理器(digital signal processor,DSP)完成的功能在此由RTL實現的微處理器(advanced reduced instruction set computer machines,ARM)核實現,完成總線控制信號的產生和控制,集成在處理器子模塊中。配置好Palladium工程編譯所需要的各類IP庫,將測試工程代碼和測試激勵在服務器中進行工程編譯。此階段可驗證代碼語法的正確性,如果編譯工具報告錯誤,則返回上一步驟修改后重新上傳編譯。

2)控制器參數配置

控制器參數通過Metrowerks Code Warrior for ARM Developer Suite軟件配置信號類型、總線地址譯碼、寄存器讀寫以及捕獲、跟蹤通道的相關參數。具體過程不再贅述。將編譯后將產生hex文件存放于服務器中,啟動Palladium工程后將加載上述配置文件。

3)導入待測工程

通過工具命令語言(tool command language,TCL)啟動Palladium工程的用戶界面,導入預先設定好的工程腳本,系統將按照腳本配置好仿真所需的各類數據、代碼文件的路徑和參數。

4)信號仿真啟動

待測工程導入完畢后,啟動Matlab定義的數據生成單元,根據需要模擬的信號類型配置相關參數,并開始運行,生成數據文件。待乒乓操作的2組數據都生成完畢,即Matlab軟件界面給出等待用戶提取數據的提示時,可啟動Palladium工程。

5)設置觸發條件并啟動Palladium加速器

在Palladium硬件加速仿真驗證軟件界面中的SDL Editor中,修改所需要的觸發條件。這類似于Chip-Scope中的觸發條件,不同點在于Palladium仿真既可以在觸發條件處上傳波形,又可以在觸發條件處暫定整個工程的運行,這是硬件調試無法完成的。并且Palladium仿真可在工程仿真過程中隨時暫定并修改觸發條件。

6)條件觸發、上傳波形

相對于Chip-Scope中抓取實際數據波形而言,Palladium硬件加速仿真的優勢在于它的可見波形多,容量大。在Palladium仿真過程中,可以看到代碼中的所有信號的波形,并且能夠逐段上傳波形,而在Chip-Scope中,受制于FPGA硬件規模和工程規模,抓取的波形數量是有限的,抓取數據長度也是有限的;相對于Modersim、NCSim等軟件仿真而言,Palladium硬件加速仿真的優勢在于它的仿真速度急快。基于CPU模擬ASIC最小邏輯單元的原理,Palladium仿真雖然無法達到FPGA片上實際運行的時鐘速率,但相對NCSim仿真提高了1 000倍[10]。

當Palladium工程滿足觸發條件,會在觸發條件設置處(相當于C程序中的斷點)中止運行,停等待用戶響應。此時,可通過腳本上傳觸發條件滿足后任意時間長度的數據波形。通過Sim-Vision軟件可以查看波形和仿真結果。

7)獲得捕獲測試結果

捕獲結果可以實時輸出,也可以通過設置觸發條件中止仿真并上傳波形后通過波形數據找到數字接收機捕獲模塊的計算結果。Palladium仿真平臺中的數字接收機將該捕獲結果轉換后送入跟蹤通道,跟蹤通道通過捕獲結果修正相關峰的搜索范圍。

8)獲得跟蹤測試結果

調整處理器配置參數,將BDS某頻點信號的捕獲結果作為跟蹤仿真的輸入,同時推算跟蹤模塊本地碼生成模塊的起始時間,配置相關參數后,以相關值計算完畢為觸發條件,運行Palladium仿真系統,進行跟蹤通道的仿真測試。

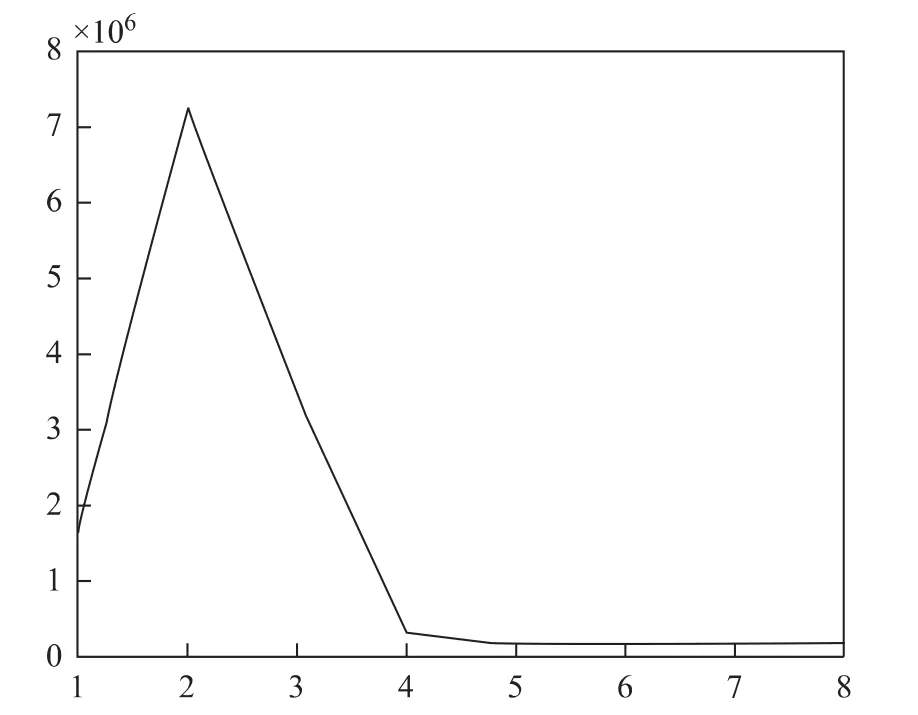

觸發條件滿足后Palladium通過腳本指令將數據上傳至服務器中,并通過Matlab啟動相關值轉換并繪圖,如圖8所示。由圖可知,當前相關值偏移約為2個碼片,這和設置的本地碼起始時間有對應關系。

圖8 第一次跟蹤獲得相關峰

根據相關峰偏移量,將處理器中配置的本地碼起始時間提早2個碼片,再次仿真,獲得正確的跟蹤結果。其相關峰如圖9所示。

圖9 相關峰:起始時間修正后的跟蹤結果

根據用戶需要,還可以將相關峰繪圖配置為準實時模式,自動上傳相關值計算結果并繪圖,類似于接收機監控軟件監視相關峰的工作場景。

接收機對BDS該頻點信號的捕獲和跟蹤完成,仿真試驗結束。

4.3 仿真結果分析

通過以上仿真驗證流程,完成了BDS某頻點接收通道捕獲和跟蹤功能的快速仿真驗證。相比ISim或NC-Sim仿真,Palladium平臺的仿真速度有成倍數的提高,其方便靈活地觸發條件設置功能使得仿真驗證更加方便快捷,實驗結果更加直觀清晰。若仿真驗證發現錯誤,修改代碼后重新編譯仿真也僅僅需要數分鐘的時間,而ISE重新生成bit文件上板調試往往需要數小時甚至一天時間,相比之下其仿真測試的效率有了明顯提高。此外還可通過改變信號模擬器的相關參數,方便地測試接收機在不同多普勒頻移條件下的捕獲性能等。以上實驗的結果證明了采用Palladium仿真驗證平臺設計的可行性以及所驗證的衛星導航接收機基帶芯片捕獲和跟蹤的功能正確性。

5 結論

通過本文介紹以及實例講解,體現了采用Palladium硬件加速器的衛星導航接收機通用驗證平臺設計的實用價值。該平臺的搭建顯著提高了數字接收機仿真驗證效率,大大加快了導航接收機功能驗證的速度。其靈活方便的觸發條件配置和強大的波形查閱能力使得代碼功能測試驗證更加全面,特別是對于數字接收機基帶處理芯片的開發,降低了芯片設計的風險,縮短了IC研發周期,確保了芯片原型設計的成功,加速產品的面世和升級。

[1] 楊津,張盛,林孝康.一款視頻解碼芯片的硬件仿真加速[J].電子器件,2010,33(5):565-567.

[2] 涂日瑋.新體制GNSS信號捕獲算法特性研究[D].哈爾濱:哈爾濱工業大學,2012.

[3] LIU Jing-nan.China’s Regional Compass System:12Satellites in 2012—ICD Next Year?[EB/OL].(2009-12-15)[2014-02-18].http://www.insidegnss.com/node/1697.

[4] 匿名.China Reveals Updated Compass/Beidou-2GNSS Signal Plan.[EB/OL].(2009-12-15)[2014-02-18].http://www.inside-gnss.com/node/1624.

[5] SLEEWAEGEN J M,WILDE W D,MARTIN H R.Galileo AltBOC Receiver[EB/OL].(2009-12-15)[2014-02-18].http://www.septentrio.com/sites/default/files/papers/GallileoAltBOC_paperFinal.pdf.

[6] BENTLEY B.Validating a Modern Microprocessor[J].Computer Aided Verification,2005(3576):2-4.

[7] 匿名.硬件仿真器成大規模IC 設計新寵[EB/OL].(2013-03-08)[2014-02-18].http://www.21ic.com/news/analog/201303/160027.htm.

[8] 江琦.Cadence推出INCISIVE PALLADIUM Ⅲ加速器/仿真器[EB/OL].(2006-12-07)[2014-02-18].http://news.eworks.net.cn/category8/news21727.htm.

[9] Cadence Design Systems,Inc.Cadence Palladium Series with Incisive XE Software:Hardware/Software Co-verification and System-level Verification[EB/OL].[2014-02-18].http://www.cadence.com/rl/resources/datasheets/incisive_enterprise_palladium.pdf.

[10] 徐健,羅天柱.CADENCE硬件仿真器在 Ethernet交換芯片驗證中的應用[J].中國集成電路,2005(76):76-78.