基于SOPC的高分辨率顯示控制器的設計與實現

郭 燾 陶吉懷

(電子科技大學 成都 611731)

0 引言

顯示控制器在嵌入式系統中幾乎必不可少,是實現圖形界面的必要手段。處理器自帶的顯示控制器通常共用系統內存作為顯存[1-2]。在顯示器分辨率較高時,處理器需要管理大量的顯存數據,當處理器主頻較低或是系統內存的訪問速率較低時,難以實現對大分辨率的顯示器的驅動[2]。一種解決的方法配備專用集成芯片設計的顯示控制器[3],但是這種方法一般需要顯示控制器和顯示器配套定制,缺乏靈活性,而且成本較高。

SOPC[4]是一種特殊的片上系統,建立在可編程邏輯技術的基礎上,盡可能將一個大而完整的電子系統實現在一塊FPGA硅片上,具有硬件可裁剪、可擴充、可升級,軟件在系統可編程的特點,使得設計的系統在規模、功能、體積、性能、上市周期、開發成本等方面有著很大的優勢。本文基于SOPC技術提出一種顯示控制器的設計與實現方案,使得在處理器主頻不是很高的情況下即可實現對高分辨率的LCD顯示器的驅動。

1 方案設計

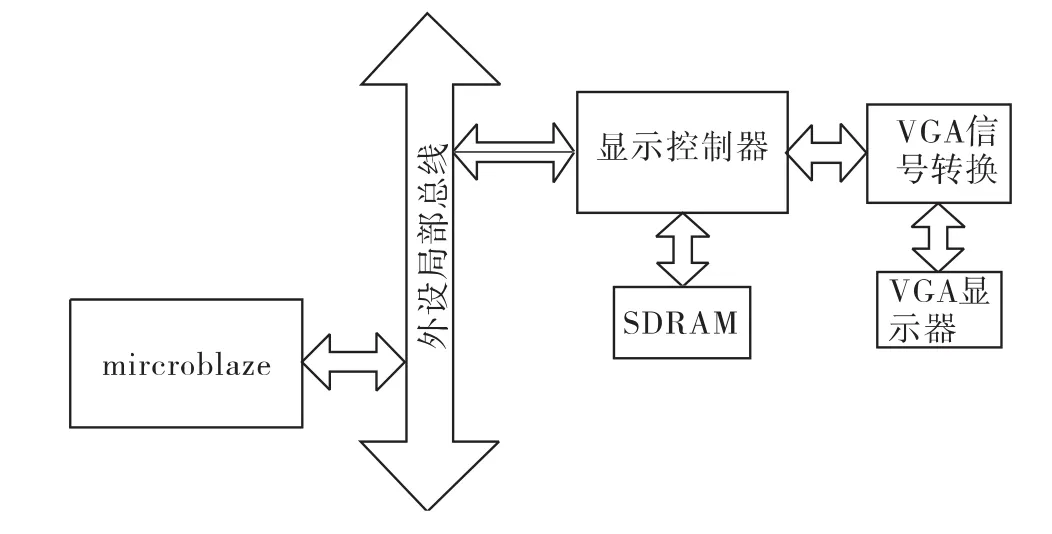

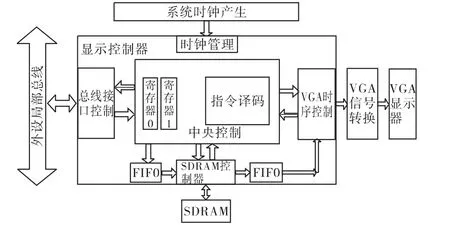

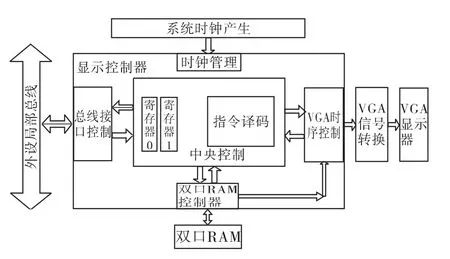

以 xilinx 的 microblaze[5]軟核處理器為例,顯示控制器和處理器的連接如圖1所示。顯示控制器通過處理器外設局部總線接口連接到基于SOPC的處理器上,作為處理器的一個外設。本設計提出兩種顯示控制器架構,第一種架構如圖2所示,第二種架構如圖3所示。通過在顯示控制器內部設置處理器可以讀寫的寄存器,實現處理器對顯示控制器的命令傳達和數據傳輸。顯示控制器內部邏輯全部通過FPGA硬件實現,包括指令獲取和譯碼、顯存數據處理處理、RAM的讀寫操作、VGA時序產生等。RAM控制器根據顯示器上點的坐標位置將顯存數據寫入RAM中相應的位置,并根據VGA時序產生模塊的讀取請求,從相應位置讀出顯存數據。VGA時序控制模塊產生行同步和場同步信號,并根據行同步、場同步的信息,將顯存數據送到VGA接口,實現圖像的顯示。

本設計中,第一種架構使用單口的SDRAM作為圖像數據存儲器,這種架構的缺點是要求SDRAM讀寫數據的速率至少是VGA接口圖像數據速率的兩倍以上,當顯示器的分辨率和刷新頻率較高時,對SDRAM的讀寫速率要求較高。第二種架構采用雙口RAM來存儲顯存數據,這種架構的優點是顯存數據的讀寫可以同時進行,RAM的寫數據速率只要達到VGA接口的圖像數據速率即可,降低了對系統時鐘的要求。

圖1 顯示控制器與處理器的連接

圖2 基于單口RAM顯示控制器架構

1.1 接口設計

顯示控制器對外的接口包括:外設局部總線接口、VGA信號轉換接口、RAM存儲器控制接口以及時鐘輸入接口。

圖3 基于雙口RAM的顯示控制器架構

外設局部總線接口由SOPC的硬件開發平臺提供。以Xilinx的SOPC硬件開發環境XPS(Xilinx Platform Studio)[6]為例,XPS 為用戶提供了 PLB v4.6、Fast Simple Link、AXI4-Lite等 5 種處理器總線接口,用戶可以選擇其中的一種接口作為自己的外設和總線的接口。

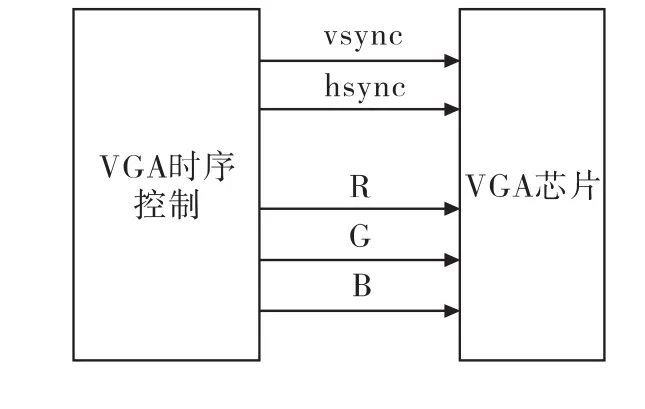

VGA信號轉換接口用于將數字信號轉換為VGA接口所需的模擬信號,該接口的定義如圖4所示,其中,vsync是場同步信號,hsync是行同步信號,R、G、B分別為紅基色分量、綠基色分量和藍基色分量。RGB的總位寬通常有8位、16位、24位和32位幾種,本設計以8位位寬為例進行設計。

圖4 VGA時序控制模塊對外接口

RAM存儲器控制接口由RAM的類型決定,通過該接口對RAM進行顯存數據的讀寫操作。

時鐘輸入接口主要是為了獲取內部硬件邏輯所需要的時鐘,本設計的顯示控制器內部主要有兩種時鐘,一種是和系統處理器總線一致的時鐘,一種是VGA時序產生所需要的時鐘。

顯示控制器內部的接口主要包括:中央控制模塊和總線接口控制模塊間的接口,中央控制模塊和VGA時序控制模塊間的接口,中央控制模塊和RAM控制器的接口。

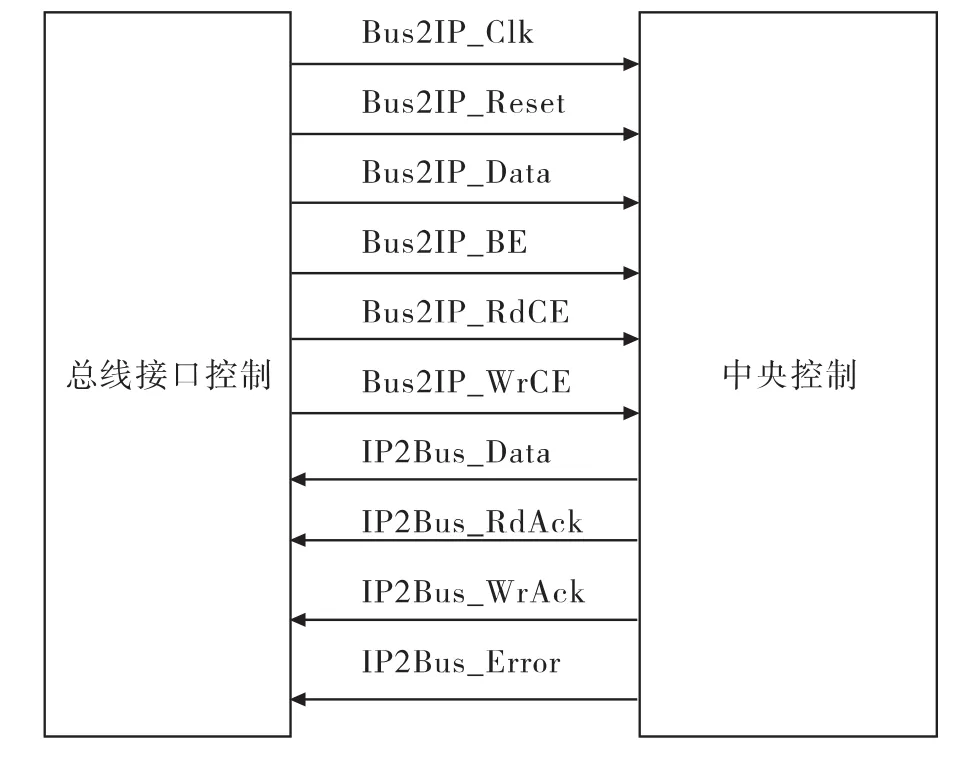

總線接口控制模塊由系統產生,它為用戶提供了一個用戶接口,該接口由用戶邏輯中使用的總線資源決定。當用戶邏輯中使用可以被處理器訪問的寄存器時,接口定義如圖5所示,其中,Bus2IP_Clk為時鐘信號,Bus2IP_Reset為對IP模塊的復位信號,其余的信號線用于讀寫用戶邏輯中可被處理器訪問的寄存器。

圖5 總線接口控制模塊和中央控制模塊間的接口

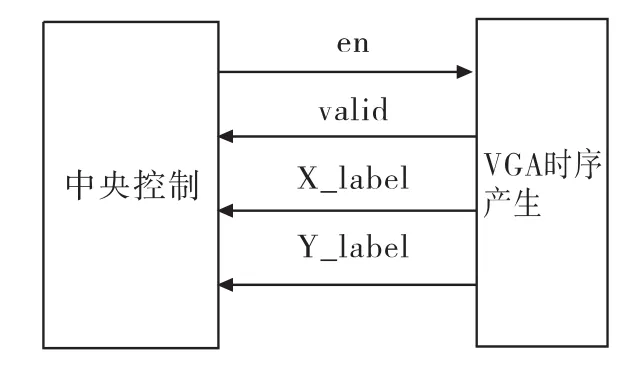

中央控制模塊和VGA時序產生模塊間的接口如圖6所示,其中,en為對VGA時序產生模塊的使能信號,valid信號指示當前VGA時序產生模塊產生的X軸坐標X_label和Y軸坐標Y_label是否有效,X_label和Y_label用于指示VGA時序產生模塊當前請求的是顯示器哪個位置的RGB值。

圖6 中央控制模塊和VGA時序產生模塊間的接口

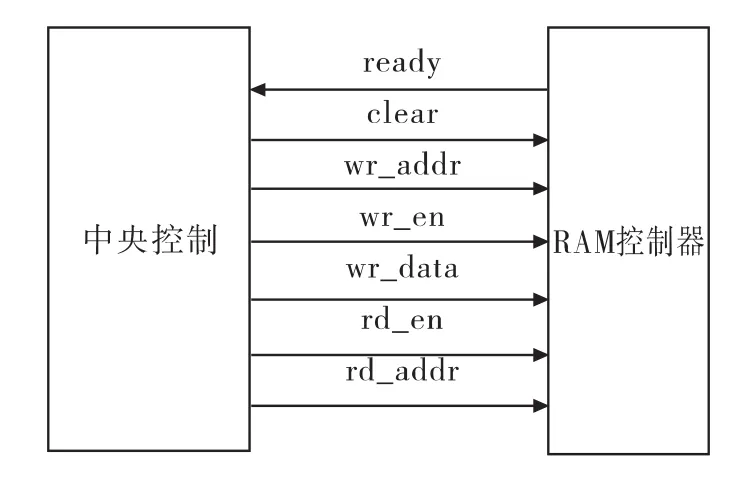

中央控制器和RAM控制器間的接口視RAM的類型而定,當采用單口的SDRAM時,寫入和讀出的顯存數據需要FIFO緩存,當采用雙口RAM時,不需FIFO緩存。以雙口RAM為例,中央控制器和雙口RAM控制器的接口如圖7所示,其中,ready用于指示RAM目前是否處于就緒狀態,clear為清除RAM命令,wr_en為寫 RAM使能,wr_addr為寫RAM的地址,wr_data為寫RAM的數據,rd_en為讀使能,rd_addr為讀RAM的地址。

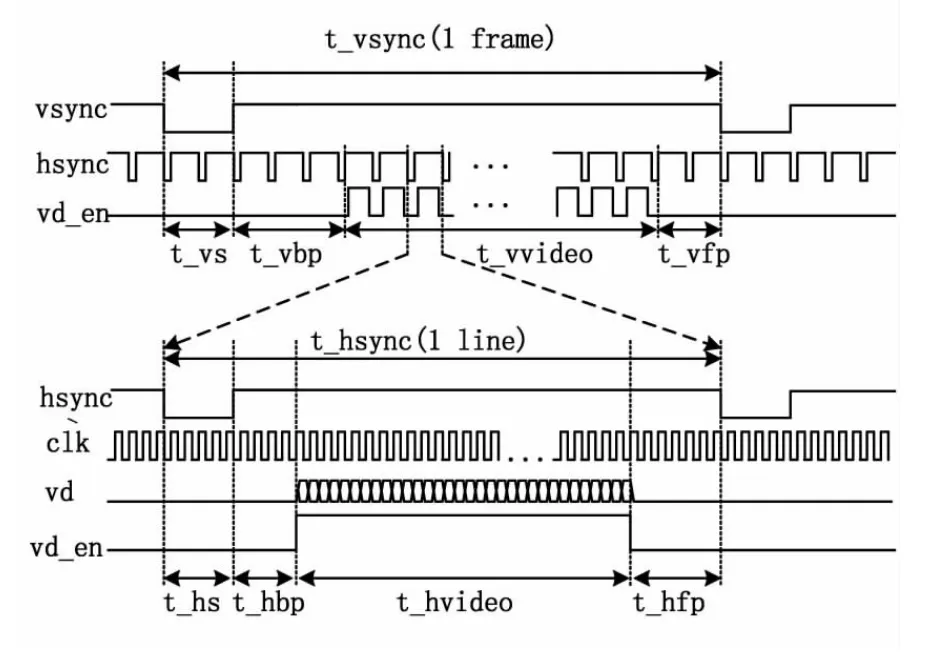

1.2 VGA時序

VGA接口時序[7]如圖8所示(其中vd_en是為了說明視頻信號vd何時有效而添加的信號,它本身不屬于VGA接口的信號)。VGA接口時序中場同步信號決定了每幀圖像的開始和結束,行同步信號和場同步信號共同決定掃描到的點在顯示器上的位置。視頻信號vd由RGB值經過數模轉換得到,決定掃描到的點的彩色值。

圖7 中央控制模塊和RAM控制器間的接口

圖8 VGA時序

以分辨率為1024×768、刷新頻率為70Hz的圖像格式為例,其點時鐘clk為75MHz,行同步頻率為56.4759kHz。

場同步信號 vsync的周期 t_vsync約為14.27ms,每場有806行,其中768行為有效顯示行,38行為場消隱期。場同步信號vsync每場有一個脈沖,該脈沖的低電平寬度t_vs為106.24μs。場消隱期包括場消隱前肩t_vfp(3行)、場同步時間t_vs(6行)和場消隱后肩t_vbp(29行),共38行。

行同步信號 hsync的周期 t_hsync約為17.71μs,每行包括1328點,其中1024點為有效顯示區,304點為行消隱期(非顯示區)。行同步信號hsync每行有一個脈沖,該脈沖的低電平寬度t_hs為1.813μs。行消隱期包括行消隱前肩t_hfp(24個clk)、行同步時間t_hs(136個clk)和行消隱后肩t_hbp(144個clk),共304個點時鐘。

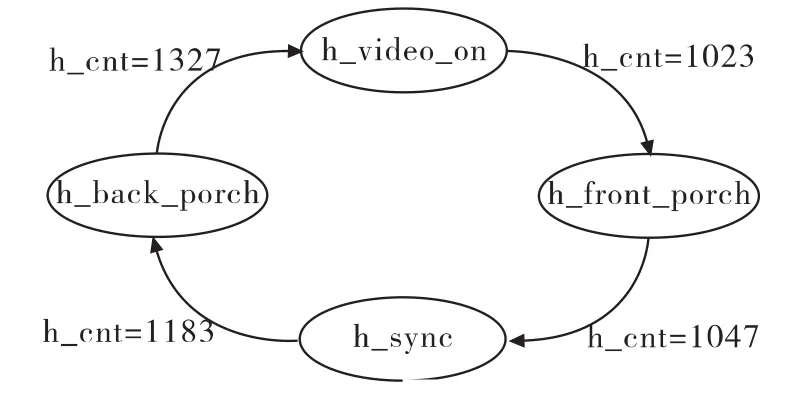

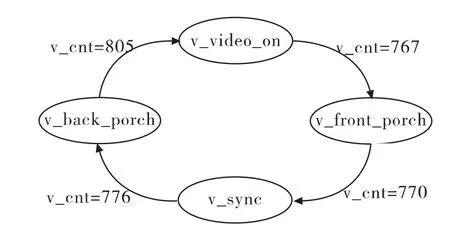

行同步和場同步信號分別通過行同步、場同步狀態機產生。行、場同步狀態機通過行計數器h_cnt和場計數器v_cnt來進行狀態轉換。行同步狀態機如圖9所示,場同步狀態機如圖10所示。行計數器的觸發信號為時鐘clk,每來一個時鐘,行計數h_cnt加1,當達到最大值1327時歸零。場計數的觸發為h_cnt,當 h_cnt=1327 時,場計數 v_cnt加 1,當 v_cnt=805且h_cnt=1327時v_cnt歸零。在行同步計數周期內,當vd_en有效時,在每個時鐘上升沿,將相應點的視頻信號vd送到VGA接口。

圖9 行同步狀態機

圖10 場同步狀態機

1.3 寄存器設置

顯示控制器內部設置了兩個處理器可以訪問的32位的寄存器,一個定義為控制寄存器CTRL[31:0],一個定義為數據寄存器DATA[31:0]。控制寄存器各比特位的定義如下:

CTRL[31]:顯示控制器使能,高電平有效;

CTRL[30]:顯存數據寫使能,高電平有效;

CTRL[29]:顯存數據讀使能,高電平有效;

CTRL[28:21]:設置顯示器分辨率模式;

CTRL[20:17]:設置顯示器刷新頻率模式;

CTRL[16]:清除顯存數據,高電平有效;

CTRL[15]:指示當前數據寄存器值是否有效;

CTRL[14:0]:保留。

數據寄存器各比特位的定義如下:

DATA[31:30]:保留;

DATA[29:19]:對應顯示器上的點的橫坐標;

DATA[18:8]:對應顯示器上的點的縱坐標;

DATA[7:0]:坐標為(DATA[29:19],DATA[18:8])的點的RGB彩色值。

2 方案驗證

利用Xilinx的XPS開發環境搭建microblaze軟核處理器硬件平臺,將本文設計的顯示控制器作為一個設備掛載到microblaze處理器的外設局部總線上[5-6]。利用Xilinx的SDK[6]開發環境為生成硬件平臺的驅動程序,利用此驅動程序,在VGA接口的LCD顯示器上繪制圖像。為了實現動態的圖像效果,實驗中在顯示器上動態地畫圈,畫圈的結果如圖11所示。

圖11 在顯示器上動態畫圓圈

實驗結果表明,在150MHz的處理器頻率下,實現在分辨率為1280×1024、刷新頻率為60Hz的LCD顯示器繪制動態圖像,沒有出現卡殼現象。

3 結論

本設計以 VGA接口為例,通過在 Xilinx的Spartan-6系列的FPGA上實驗,在主頻相對較低的軟核處理器上實現了大屏幕顯示器的驅動,說明了方案的可行性。本文設計的顯示控制器不局限于SOPC,可應用于基于ASIC的系統中,針對不同的處理器,只需稍微修改總線接口控制邏輯即可,設計靈活,具有通用性。

[1] 杜春雷.ARM體系結構與編程[M].-北京:清華大學出版社,2003.

[2]丁鐵夫,陳偉,鄭喜鳳等.多媒體協處理器SM501在全彩LED顯示屏脫機播放系統的應用[J].液晶與顯示,2009,24(6):860-865.

[3]王立風.多媒體協處理器SM501在嵌入式系統中的應用[J].單片機與嵌入式系統應用,2006,(6):42-43.

[4] 江國強.SOPC技術與應用[M].北京:機械工業出版社,2006.

[5]Xilinx Company.MicroBlaze Processor Reference Guide v13.2[EB/OL].[2011-7-6].http://www.xilinx.com.

[6]Xilinx Company.Embedded System Tools Reference Manual v13.2[EB/OL].[2011-7-6].http://www.xilinx.com.

[7] 曹允.基于FPGA的VGA時序彩條信號實現方法及其應用[J].電子工程師,2002 28(7):42-45.