利用單板機+FPGA實現對FPGA的在線配置

李耀南 王 謙

(西安電子工程研究所 西安 710100)

0 引言

雷達總站進行聯調時,某些分系統可能需要經常修改調試FPGA程序,而配置新程序時一般都需要斷電、連接JTAG下載電纜;通電;配置;再斷電;斷開JTAG下載電纜;通電測試等一系列步驟。這樣的步驟很繁瑣,將大部分時間浪費在無意義的拔插JTAG下載電纜上。如果在雷達正常工作時,通過內部設備實時對FPGA在線配置新調試程序,將極大地提高調試的效率。針對以上問題,本文提出了一種利用系統內的單板機通過CPCI總線訪問一片FPGA從而對另一片FPGA進行實時配置的方法。

1 配置模式分類

FPGA配置模式[1]種類很多,依據 FPGA能否主動加載配置數據可分為主模式、從模式和JTAG模式。主模式是指由被配置FPGA內部產生配置所需的時鐘信號(稱為CCLK),且被配置FPGA主動加載片外非易失性存儲器中的配置比特流數據。從模式是通過外部的主智能終端(如處理器或DSP等)建立配置所需的時序[2],將配置數據加載到FPGA中,FPGA在配置過程中是被動的。JTAG模式主要用于調試,可將計算機中的bit文件通過JTAG配置電纜加載到FPGA中,斷電即丟失。

Xilinx FPGA的主配置模式可分為主串行(Master Serial)模式、主并行(Master SelectMAP)模式。在主配置模式中,FPGA的配置數據來自PROM,配置時鐘CCLK由被配置FPGA內部產生。

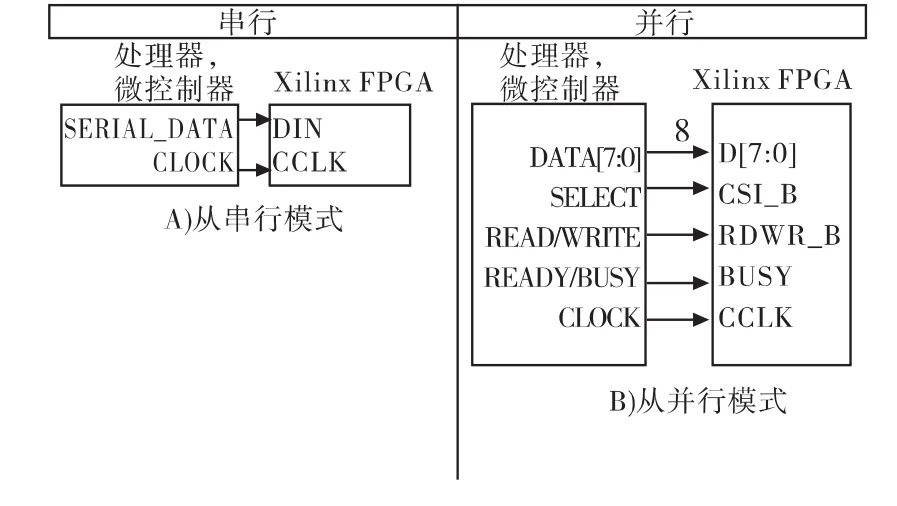

從配置模式下,FPGA配置數據的存儲介質不僅僅是PROM,還可以是FLASH、硬盤、網絡,甚至在處理器的運行代碼中[3],配置時鐘CCLK來自外部設備。從模式依據配置比特流位寬分為從串行(Slave Serial)和從并行(Slave SelectMAP)模式,如圖1所示。

圖1 常用的從配置模式示意圖

由此可見,若要利用單板機和外部FPGA對等待配置的FPGA的進行遠程配置,則只可以使用從模式中的從串行和從并行模式。

FPGA的配置模式可通過FPGA的配置管腳M2、M1、M0的上拉或者下拉來選擇,不同系列的FPGA的配置選擇也不完全相同,下面以XILINX的VIRTEX4系列FPGA的配置為例,來講述FPGA的從串行配置模式和從并行配置模式。

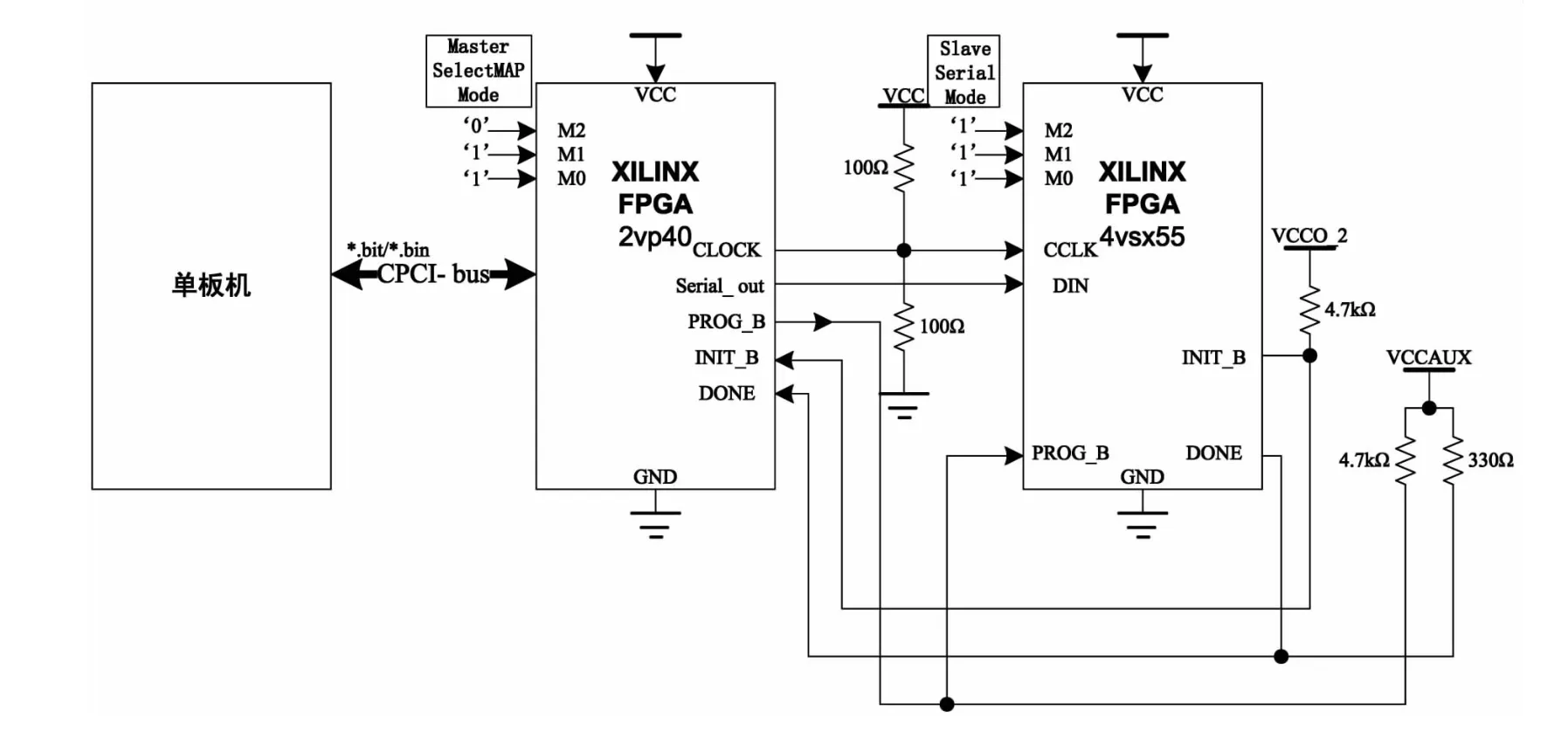

2 從串行配置模式

如圖2所示,等待配置的 FPGA的型號為4vsx55(下面簡稱該FPGA為4vsx55),生成配置邏輯的FPGA型號為2vp40(下面簡稱該FPGA為2vp40)。要對4vsx55進行從串行配置,首先要將其配置管腳 M2、M1、M0 置為‘1’、‘1’、‘1’,硬件上的4vsx55 的 CCLK、DIN、PROG_B、INIT_B、DONE 等信號也要與2vp40的IO管腳連接,另外CCLK、PROG_B、INIT_B、DONE等信號還要進行相應的上下拉。

圖2 FPGA從串行配置模式示意圖

4vsx55的配置文件既可用最常用的.bit文件也可用.bin文件(.bit文件和.bin文件的區別就在于,.bin只包含配置數據,沒有前面的header information),生成.bit或.bin文件時應選擇相應的配置時鐘,該配置時鐘頻率決定了CCLK的頻率。該配置文件存放在單板機上。系統上電后,2vp40已經由PROM完成了主并配置且開始運行。對4vsx55配置前可先將配置文件通過CPCI總線傳至2vp40,2vp40暫時將其存放在外掛的SDRAM中,從而保證了在CCLK時鐘周期到來前4vsx55的DIN輸入管腳的串行配置數據有足夠的建立時間。

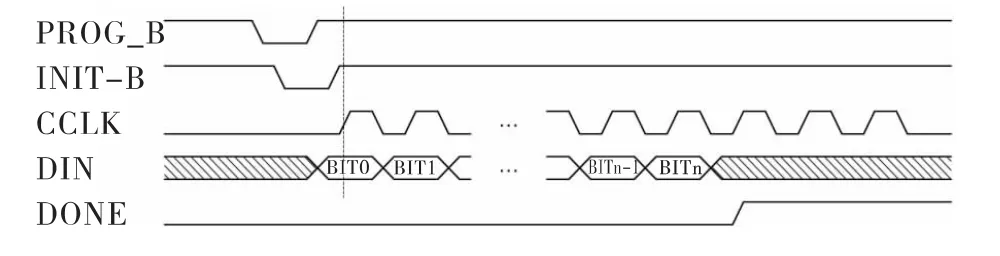

從串行配置時序如圖3所示,2vp40通過給4vsx55的PROG_B一個脈寬大于300ns的負脈沖信號啟動配置,在PROG_B的信號拉低后,INIT_B的信號會隨之變低,當PROG_B的信號拉高后,同時開始檢測INIT_B是否抬高,檢測到INIT_B的上升沿時,表明4vsx55已經做好準備,開始接收向DIN傳送的與CCLK同步的串行配置數據(注意:這里的CCLK在上升沿時刻采樣配置數據)[4]。若數據全部正確接收完成后,DONE信號抬高,這時再多保持3個CCLK的時鐘周期,以保證4vsx55配置完成后開始正常運行;否則INIT_B變低,說明配置出錯才停止。整個配置過程需要比配置文件比特長度更多的時鐘周期,而多余的部分時鐘要用于建立時序,尤其當4vsx55被配置為等待DCM時。

圖3 從串行配置時序

3 從并行配置模式

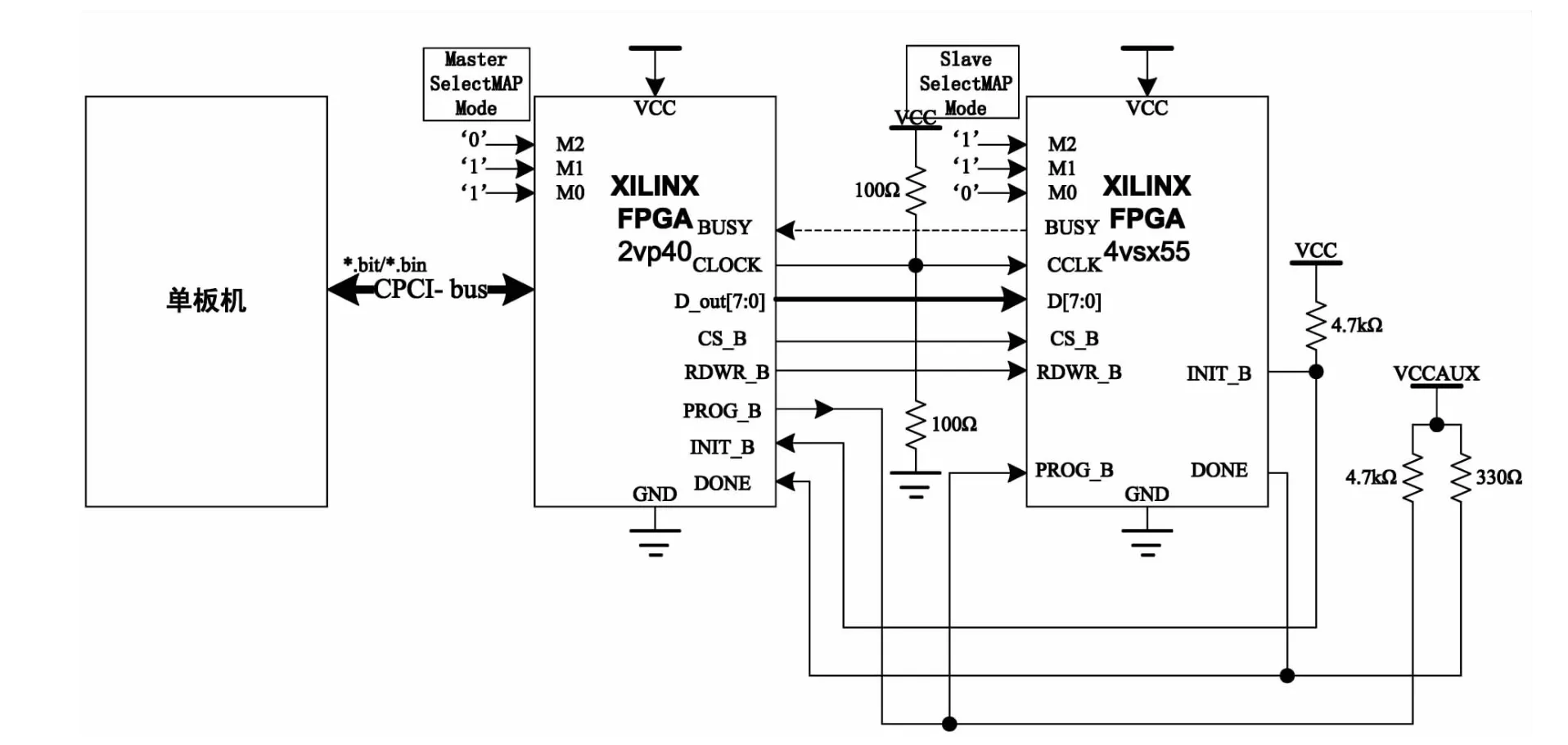

如圖4所示,要對4vsx55進行從并行配置,首先要將其配置管腳 M2、M1、M0 置為‘1’、‘1’、‘0’,硬件上的 4vsx55 的 CCLK、DIN、PROG_B、CS_B、RDWR_B、INIT_B、DONE、BUSY 等信號也要與2vp40的IO管腳連接,另外 CCLK、PROG_B、INIT_B、DONE等信號還要進行相應的上下拉。

圖4 FPGA從并行配置模式示意圖

.bit文件和.bin文件并沒有按字節進行位翻轉,而并行加載要求位翻轉,因此2vp40在向4vsx55送配置數據時應按字節進行位翻轉之后再傳送。

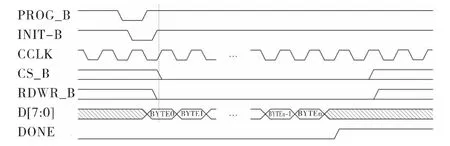

從并行配置時序如圖5所示,2vp40通過給4vsx55的PROG_B一個脈寬大于300ns的負脈沖信號啟動配置,在PROG_B的信號拉低后,INIT_B的信號會隨之變低,當PROG_B的信號拉高后,同時開始檢測INIT_B是否抬高,檢測到INIT_B的上升沿時,表明4vsx55已經做好準備,CS_B相應地置低可使能并行數據總線,(若是不回讀配置回報信息則RDWR_B可始終置為低),這時開始接收向D[7:0]傳送的與CCLK同步的并行配置數據(注意:這里的CCLK在上升沿時刻采樣配置數據,并行的配置數據是配置文件按字節進行位翻轉之后的)。若數據全部正確接收完成后,DONE信號抬高,表明4vsx55配置完成后開始正常運行;否則INIT_B變低,說明配置出錯才停止。整個配置過程可以始終保持CCLK時鐘周期。

值得注意的是,對FPGA的PROM而言,串行模式的DIN和并行模式的D0是同一根線,而對FPGA而言卻不一定,SPARTAN3系列是同一根線,而VIRTEX4系列是兩根獨立的信號線。

很明顯可以看出,從串行模式用的是1根數據線配置,而從并行模式用的是8根數據線,所以從并行模式的配置速度幾乎是從串行模式的八倍之多。

圖5 從并行配置時序

4 結論

本文提供的方法解決了產品運行時實時調試程序的問題,對工程設計有一定的借鑒意義。本方法進一步還可讓FPGA在不同的模式下配置不同的程序,實現FPGA運行時重構[5],可應用于多種模式分時復用FPGA資源的場合,對于節約產品成本有一定幫助。

[1]Virtex-4 Configuration Guide[OL].www.xilinx.com,2008.

[2]劉瑞賢.基于分子計算的并行處理機設計與實現[D].北京:北京郵電大學,2009.

[3]郎永輝.基于多軟核并行處理的數字圖像處理算法的研究 [D].長春:長春工業大學,2010.

[4]張國斌等.FPGA開發全攻略[OL].wenku.baidu.com,2009.

[5]鄭文榮,孫朝江,劉少偉 .復雜系統的多FPGA可重構設計與實現[J].電子測量技術,2012,35(9):96-98.