基于AD9852的地檢設備信號源設計

高琪李明

(西安電子科技大學 西安 710071)

0 引言

隨著微電子技術和數(shù)字集成電路的進步,直接數(shù)字頻率合成(DDS)技術得到了飛速發(fā)展。由于DDS技術具有幅度和相位一致性好、頻率轉換時間短、頻率分辨率高、穩(wěn)定度好、輸出相位連續(xù)可控、頻帶范圍寬、可編程及全數(shù)字化結構等優(yōu)點[1],廣泛應用于現(xiàn)代無線通信系統(tǒng)、雷達和現(xiàn)代化儀器儀表等多個領域。而現(xiàn)場可編程門陣列(FPGA)具有集成度高、通用性好、設計靈活、方便編程等特點,因此可以快速地完成復雜的數(shù)字系統(tǒng)設計。本文采用FPGA和AD9852相結合的方式完成了地檢設備信號源的設計。

1 AD9852簡介

AD9852是AD公司生產(chǎn)的輸出頻率可達120MHz,頻率轉化速度小于1μs的直接頻率合成芯片。參考時鐘可單端或者雙端輸入,AD9852支持最高10MHz的串口或者最高100MHz并口通信(由Pin70 S/P SELECT選擇),可方便的完成控制字傳輸。內(nèi)部包含高速、高性能D/A轉換器和比較器,可以實現(xiàn)可編程、可靈活使用的頻率合成功能,當給AD9852提供精確的頻率時鐘源時,可輸出一個頻譜純凈、頻率和相位都可以編程控制且穩(wěn)定性良好的模擬正弦波[2],輸出的正弦波也可通過其內(nèi)部比較器轉換成占空比可調(diào)的方波輸出。AD9852主要功能特點如下[3]:

a.內(nèi)部時鐘最高可達300MHz;

b.包含1個12位cosine D/A和1個12位control D/A;

c.帶有兩個48位可編程頻率寄存器和兩個14位可編程相位寄存器;

d.具有12位可編程振幅調(diào)制寄存器和開關輸出形鍵控功能;

e.內(nèi)含4×到20×可編程基準時鐘乘法器。可在內(nèi)部產(chǎn)生高頻時鐘信號,避免了對外部高頻振蕩器的需要,減小了由于外頻過高產(chǎn)生的相位噪聲[2];

f.出色的動態(tài)性能:80dB SFDR(100MHz±1MHz);

g.反SINC濾波器,可對數(shù)據(jù)經(jīng)過D/A轉換后產(chǎn)生的SINC包絡形畸變校正;

h.支持5種工作模式:SINGLE-TONE、FSK、RAMPED FSK、CHIRP、BPSK。

AD9852可編程頻率寄存器為48位,可編程相位寄存器14位,若DDS系統(tǒng)時鐘為fc,則DDS輸出頻率、相位分別為:

上式(1)中FTW為頻率控制字,(2)中POW為相位控制字。

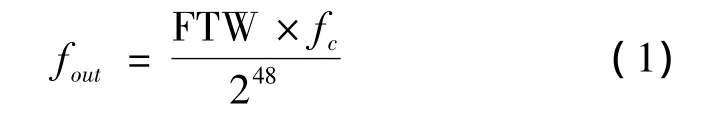

AD9852內(nèi)置的比較器可以實現(xiàn)將DAC輸出的正弦信號轉換成方波,使用方式如圖1所示。為濾除來自交流信號的鏡像頻率分量,由AD9852輸出的正弦信號在輸入比較器之前,需要完成重構濾波,濾波器的作用在于平滑AD9852內(nèi)部輸出的階梯波[4]。當開關接通位置1時,比較器輸入為差分互補的正弦信號,可輸出占空比為50%的方波,當開關接通位置2時,可控DAC可由用戶設置直流門限電壓,實現(xiàn)占空比可調(diào)的方波輸出。

圖1 AD9852方波產(chǎn)生圖

AD9852共有39個可編程寄存器,對AD9852的控制是通過向這些寄存器寫數(shù)據(jù)實現(xiàn)的[5]。為使用戶編程的數(shù)據(jù)從I/O緩沖區(qū)寫入DDS寄存器,必須提供一個更新時鐘。AD9852提供內(nèi)部和外部更新兩種方式:內(nèi)部更新由32位計數(shù)器產(chǎn)生,當計數(shù)器自減為零后會產(chǎn)生一個內(nèi)部更新信號;外部更新通過向Pin20提供一個上升沿時鐘完成。兩種更新模式可通過控制寄存器選擇。

2 系統(tǒng)總體方案設計

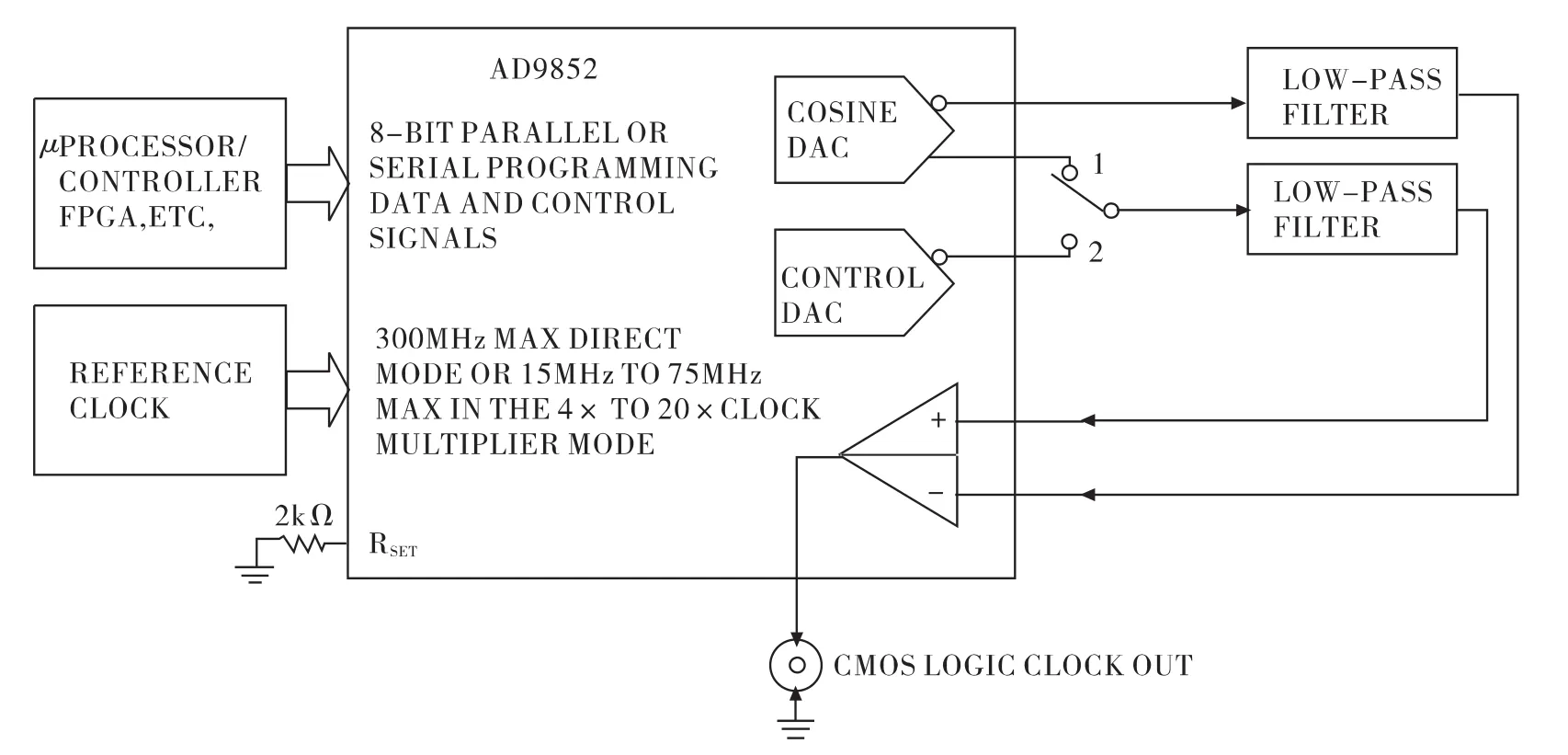

系統(tǒng)結構如圖2所示。外部接收由外參考馴服模塊送出的10MHz信號,經(jīng)過波形轉換送入AD9852,內(nèi)部10倍頻后作為DDS系統(tǒng)時鐘(此時系統(tǒng)頻率分辨率為3.55×10-7Hz)。FPGA可接收上位機發(fā)來的頻率控制信息完成對AD9852的配置,使AD9852輸出10.23MHz正弦信號,經(jīng)過外部低通濾波器濾波,送入MC12040(鑒頻鑒相器)的一個參考輸入端,鑒相器的另外一個輸入端接收本地10.23MHz晶振中10.23MHz信號,外部構成完整的PLL,最終由晶振輸出與10MHz相參的10.23MHz正弦信號。

本設計中由于對FPGA資源要求,速度性能與管腳數(shù)量要求都不是太高,因此從節(jié)約成本的角度考慮,我們選用Altera公司的CycloneⅢ系列FPGA EP3C16E144I7,出于速度上的考慮,AD9852與EP3C16E144I7之間的I/O口通訊采用并口連接。時鐘信號采用雙端差分輸入。FPGA主要包含通信模塊、AD9852接口模塊。

圖2 系統(tǒng)框圖

2.1 FPGA通信模塊

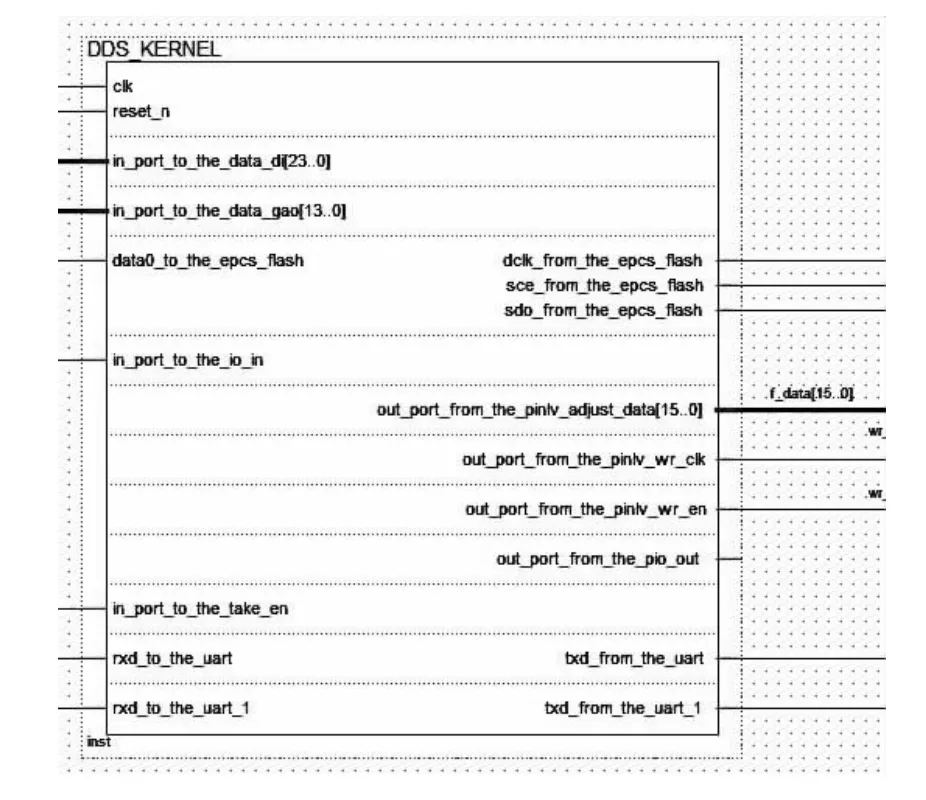

FPGA通信模塊由SOPC工具設計的嵌入式NiosII軟核完成,使用C語言編寫,結構如圖3所示。主要功能為:a.采用中斷的方式接收上位機從串口RS232發(fā)送的頻率和頻率微調(diào)信息,按照規(guī)定協(xié)議解析,通過式(1)、(2)完成頻率及相位控制字的計算,由16位數(shù)據(jù)總線發(fā)送給AD9852接口模塊。b.將AD9852產(chǎn)生的信號與10MHz基準源的頻差信息和鎖定信息由串口RS232發(fā)送給上位機。

圖3 FPGA通信模塊

2.2 AD9852接口模塊

該模塊的結構如圖4所示。AD9852接口模塊主要操作有AD9852復位(m_res)、地址總線(addr[5..0])、數(shù)據(jù)總線(data[7..0])、寫使能(wr)、數(shù)據(jù)更新(io_upd)、頻率選擇(FSK)。AD9852的初始化流程為:

A.上電后需要對 AD9852進行復位,使得AD9852內(nèi)部所有寄存器都被設置為默認值(此時AD9852默認為內(nèi)部信號更新模式)。該復位信號由m_res給出,需至少維持10個系統(tǒng)時鐘周期的高電平。

B.接收通信模塊發(fā)送的頻率與相位控制字。該模塊與通信模塊使用異步FIFO完成控制字接收。

C.使用并行總線設置地址為1D~20的特殊功能寄存器:

a.由于需要使用內(nèi)置比較器產(chǎn)生方波,所以需要打開比較器、I通道 DAC和數(shù)字部分,寄存器0x1D=04h;

b.參考時鐘 10MHz,DDS系統(tǒng)時鐘使用100MHz,所以倍頻系數(shù)為10,設置寄存器 0x1E=0Ah;

c.設置AD9852為外部信號更新,選擇工作模式為單頻模式,設置寄存器0x1F=00h;

d.不使用OSK功能,為降低AD9852功耗不使用逆SINC濾波器,因此設置寄存器0x20=00h;

D.完成特殊功能寄存器設置后,內(nèi)部更新計數(shù)器減到0時,寄存器的內(nèi)容才更新完成。此時由于頻率控制字寄存器為零,因此輸出頻率為零。

E.特殊功能寄存器更新后,AD9852的更新信號被設置為外部更新,使用并行傳輸完成頻率控制字和相位控制字的寫入。

F.頻率與相位寄存器設置完成后,由io_upd發(fā)送一個高電平脈沖完成寄存器更新,AD9852即可按照編程方式產(chǎn)生預期信號。

3 電路測試結果

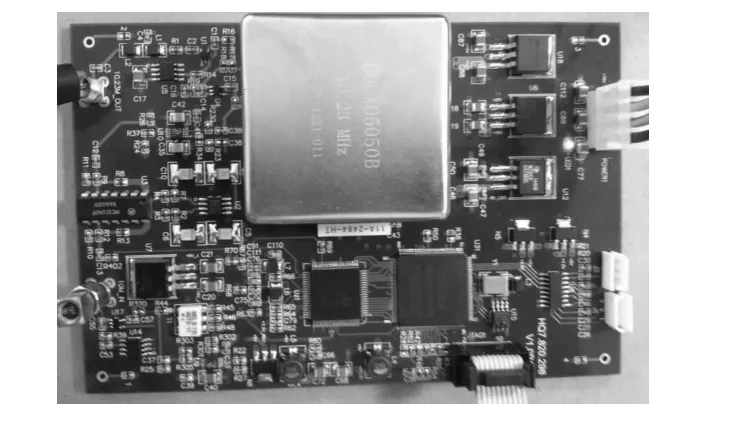

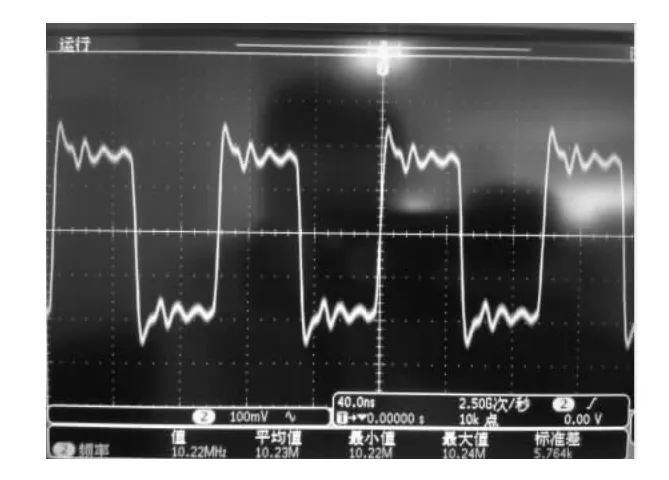

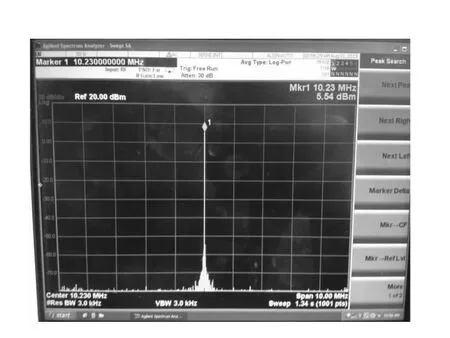

對于數(shù)字信號源來說,對產(chǎn)生信號的測試,既可以確認DDS是否實現(xiàn)了波形可變的功能,又可以分析確定DDS產(chǎn)生的信號是否滿足設計要求。圖5為信號源核心板俯視圖,圖6為AD9852輸出正弦信號的時域圖,圖7為利用AD9852內(nèi)部高速比較器產(chǎn)生的方波信號,圖8、圖9分別為外部高穩(wěn)晶振鎖定后產(chǎn)生的10.23MHz正弦信號的頻譜圖和雜散圖。

圖5 信號源核心板

圖6 正弦信號時域圖

圖7 內(nèi)部比較器輸出方波時域圖

4 結束語

本文根據(jù)AD9852性能特點,提出了一種FPGA+AD9852的信號源方案,具有結構簡便、體積小、頻率分辨率高、頻率轉換速度快、輸出頻譜純凈等特點。信號源的頻率、幅度軍均控,可以實現(xiàn)多種調(diào)制,滿足了設備對信號源的要求。

圖8 高穩(wěn)晶振鎖定輸出正弦信號頻譜

圖9 高穩(wěn)晶振鎖定輸出正弦信號雜散

[1] 郭德淳,費元春.高性能DDS芯片-AD9852的應用研究[J].電訊技術,2001,(4):52-55.

[2]李軍.X波段微波倍頻器的研制與一種頻率源設計[D].成都:電子科技大學,2004.

[3]AD9852 datasheet,Analog Devices Inc.,2002

[4] 葉佳.基于AD9852的多功能直接數(shù)字信號合成源的研制[D].南京:南京航空航天大學,2005.

[5] 蔡磊.多路相位可控信號源[D].哈爾濱:哈爾濱工業(yè)大學,2006.