CMOS工藝X射線圖像傳感器設計

孟麗婭,袁 松,王慶祥

(1.光電技術及系統教育部重點實驗室,重慶 400032;2.重慶大學 光電工程學院,重慶 400032)

X射線在醫學成像、生物分子結構研究、空間應用、工業產品質量檢查和評估等方面具有廣泛、重要的應用。常規的高精度X射線數字化成像技術通常需采用CsI(Tl)閃爍體或Gd2O2S增感屏將X射線轉換為可見綠光或藍光[1],然后通過光纖或透鏡系統,經CCD或CMOS圖像傳感器將該熒光信號變換為電信號從而獲得圖像,而閃爍體或增感屏會降低成像信號的空間分辨率和時間分辨率。若能省略閃爍體或增感屏,直接對X射線進行數字成像,有望進一步提高X射線成像檢測系統的分辨率和探測效率[2]。本文研究一種不需中間光轉換層,直接對X射線進行成像的低成本標準CMOS工藝圖像傳感器,設計該種圖像傳感器的像元結構,對其X射線探測原理進行理論分析,并采用0.5 μm標準CMOS工藝制作含不同光敏元的線陣圖像傳感器,進行X射線探測實驗。

1 像元結構

光敏元采用N阱/P襯底二極管結構,像元內電路為典型的3-T讀出結構[3],像元內晶體管采用N型MOS晶體管以避免影響光敏元對電荷的收集。X射線對N型MOS晶體管器件的影響主要為閾值電壓漂移和漏電流的增加[4],可采用環形柵結構進行輻射加固[5]。X射線入射到硅電路上,將穿透制作在硅表面上的電路結構,沿著射線穿過的軌跡按一定比例損失能量,并在硅材料中引起電離輻射效應,激發出電子/空穴對,激發出的電子一部分在擴散過程中與空穴復合,另一部分到達N阱被收集。在低載流子密度情況下,決定非平衡載流子壽命的主要復合機制是借助于缺陷能級的間接復合[6]。

當X射線持續入射到探測器中,單位時間內在每μm硅襯底中激發的電子/空穴對數目n為:

n=C1ρDX/Eg

(1)

式中:C1為每μm硅襯底所吸收的X射線能量的比率;DX為單位時間內X射線劑量;Eg為硅中電子/空穴對的電離能;ρ為探測器材料的密度。

施加了正偏壓的N阱將不斷吸引被激發出來的電子,N阱深度越大,吸引的電子數目越多。若電荷載流子的產生壽命為τ′,則持續的X射線入射不斷地產生電子/空穴對,所生成的額外載流子的密度N(t)為:

N(t)=nτ′(1-et/τ′)=C1ρDXτ′(1-et/τ′)/Eg

(2)

(3)

電子速度ve為:

(4)

式中:E為電場強度;Ec=vs/μ,vs為電子漂移飽和速度。

在300 K時,μ=1 450 cm2/(V·s),β=1.30,Ec=7 240 V/cm,則單位時間內收集的電荷總數為:

Q=N(t)s=C1ρDXτ′(1-et/τ′)·

(5)

電荷形成的電壓VX=Q/CT,二極管勢壘電容CT為:

(6)

式中:ε為相對介電常數;ε0為真空介電常數;NA為P區摻雜濃度;q為電子電荷;V為外加電壓;Vbi為硅的內建電勢。

則有:

(7)

由式(7)可知,光敏元面積越小、襯底的摻雜濃度越低、襯底缺陷越少、施加的偏壓越大,VX越大。另外,在同一像元中有多個光敏元有利于更好地收集X射線在襯底上激發的電子,但隨光敏元個數的增加,其寄生電容和漏電流也將增大。本文設計了4種像元:單個像元內含1、2、3及4個光敏元,每個光敏元面積均為5 μm×5 μm,像元內的光敏元的水平中心距為25 μm,垂直中心距為30 μm,相對位置如圖1所示。

X射線對光敏元的影響主要體現為漏電流的增大[7],光敏元漏電流增大的原因是對光敏元進行隔離的場氧具有較柵氧更多的缺陷,更易捕獲電荷從而導致電荷的堆積,因此在光敏元邊緣處利用多晶硅層在N阱的邊緣處形成較薄的柵氧,減少捕獲電荷[8],但在柵氧和場氧的交界處會形成寄生的邊緣N型場效應晶體管,該寄生場效應晶體管同樣具有閾值電壓漂移特性,這樣在寄生晶體管的柵極電壓為0 V時可能會有源漏電流,因此,采用P+保護環以避免該源漏電流的產生。

圖1 4種光敏元結構

2 X射線實驗

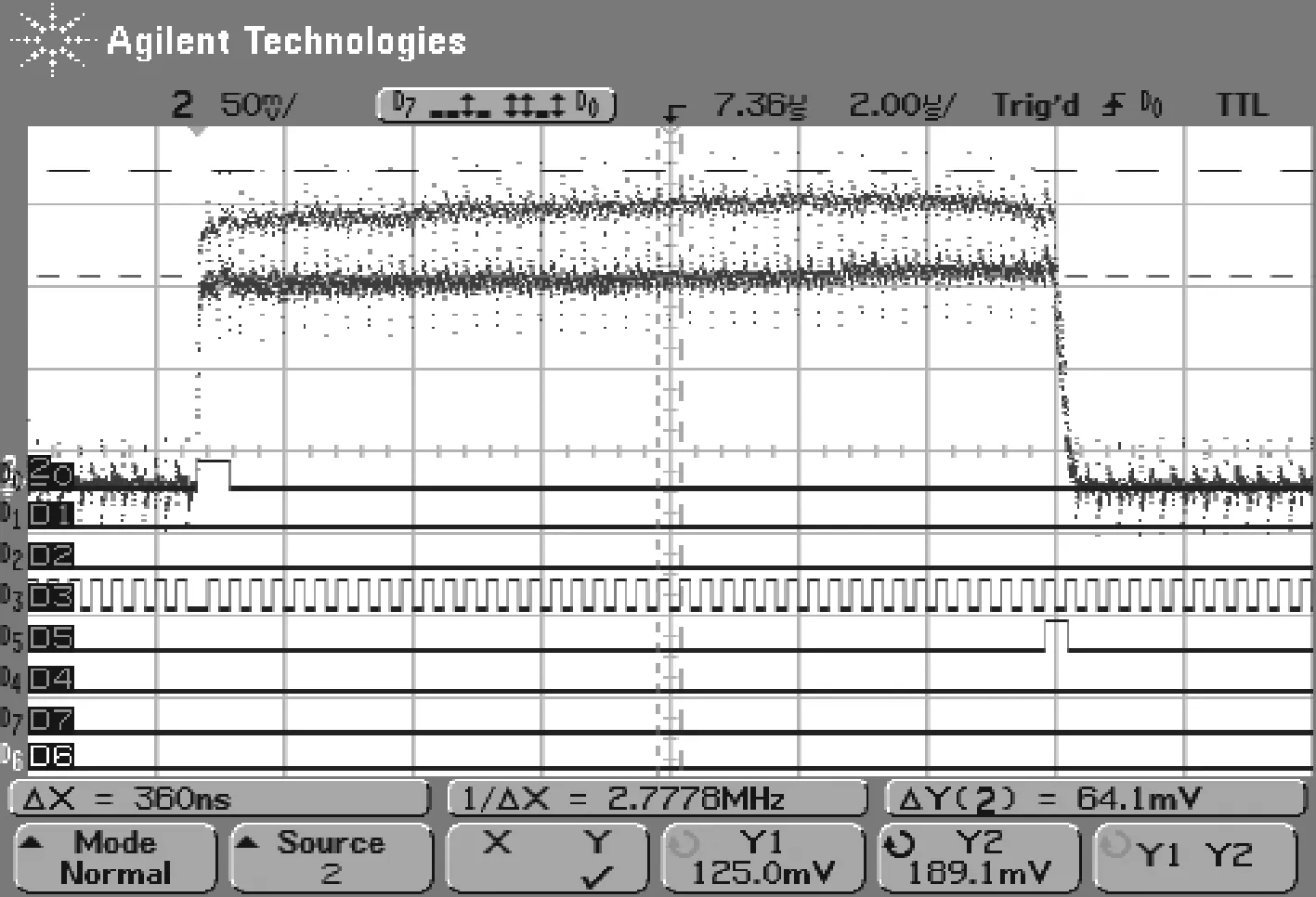

本文采用0.5 μm DPTM CMOS工藝制作了40位線陣,比較不同結構像元的電荷收集效果。流片封裝后的40位線陣由40位光敏元、源隨器、相關雙采樣電路和輸出緩沖器及移位寄存器[9]組成。該線陣中像元結構依次為1、2、3和4個光敏元結構,每種類型設計了10位像元,中心距100 μm。圖2為示波器記錄的對牙科射線儀的輸出響應,由于牙科射線儀為整流輸出,并不是恒定直流射線源,而線陣的積分時間很短,因此示波器上出現高低不同的多條曲線。

圖2 線陣在牙科射線儀照射下的輸出

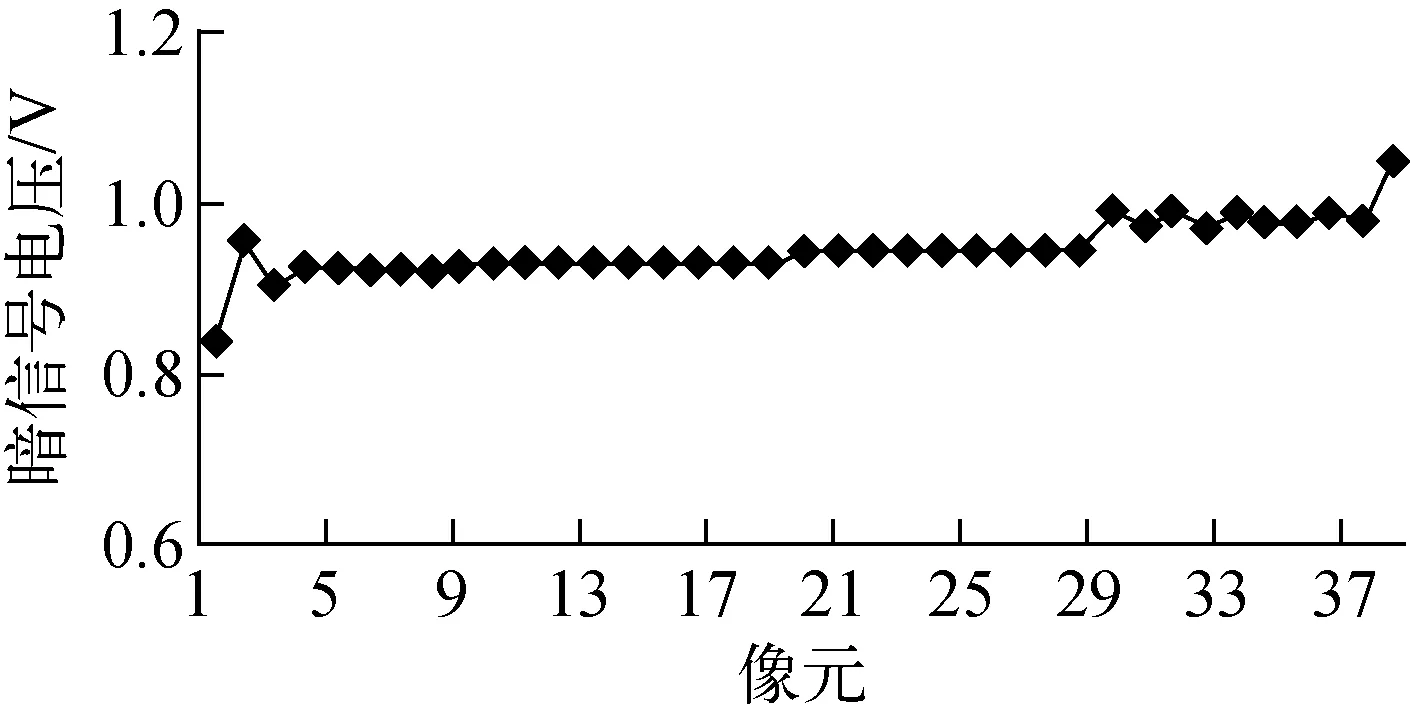

利用NI數據采集卡PCI 6115和LabView虛擬儀器程序及SB-80-250直流X射線源對該線陣進行測試,采用厚0.12 mm的鋁片將實驗用線陣的窗口進行高頻壓焊密封。SB-80-250直流X射線源的管電流范圍為10~250 μA,管電壓范圍為35~80 kV。本文分別測試3片線陣樣管在無入射光時的暗信號電壓及在不同射線源輸出下的電壓響應曲線(積分時間tint=18.7 ms),結果示于圖3~5。圖3~5中所有數據均為測試100次的均值(圖中未顯示第1位像元的輸出)。圖3為無X射線照射時測得的線陣暗信號電壓Vod,含1個光敏元的像元暗信號電壓均值為0.914 V,含2個光敏元的像元暗信號電壓均值為0.929 V,含3個光敏元的像元暗信號電壓均值為0.945 V,含4個光敏元的像元暗信號電壓均值為0.990 V。暗信號電壓隨像元中光敏元個數的增加而增大,總的漏電流隨光敏元個數的增加而增大。

圖3 線陣輸出暗信號電壓

圖4為將X射線源的管電流固定為250 μA,改變其管電壓時線陣的有效輸出電壓Voe(Voe為線陣各像元的輸出電壓減去相應的暗信號電壓)。可看出,當X射線源管電壓為75 kV以上時,線陣輸出已基本飽和,飽和有效輸出電壓約為1.4 V。

圖4 線陣在不同管電壓X射線源下的有效輸出電壓

圖5為將X射線源管電壓固定為80 kV,改變其管電流時線陣的有效輸出電壓。可看出,當X射線源管電流為200 μA時陣列輸出未飽和,而增大X射線源管電流至250 μA時陣列輸出飽和。

圖5 線陣在不同管電流X射線源下的有效輸出電壓

由圖4和5可見,對于含1個光敏元、2個光敏元和3個光敏元的像元結構,隨著光敏元個數的增加有效輸出電壓增大;但對于含4個光敏元的像元結構,有效輸出電壓低于2個光敏元和3個光敏元的像元結構,這是因為像元的總寄生電容和漏電流隨光敏元個數增加的結果。

3 結論

本文設計了用于X射線直接成像的圖像傳感器線陣,分析了其電荷收集的原理,設計了含多個光敏元的輻射加固像元結構。采用虛擬儀器技術對該線陣進行了測試,該線陣的暗信號電壓約為1 V,飽和輸出電壓約為2.4 V。在單個像元內設計多個光敏元有利于電荷的收集,但隨著光敏元個數的增加寄生電容和漏電流增加,針對本文所設計的光敏元結構及所采用的工藝,單個像元內含3個光敏元的結構得到的有效輸出電壓最大。

參考文獻:

[1] XIAO Bowen, SUN Chengwei, CHEN Hengyin, et al. A digital radiography readout system for low dose and high resolution amplified pixel sensor[C]. Taipei: IEEE, 2012.

[3] DULINSKI W, BERST J D, BESSON A, et al. CMOS monolithic active pixel sensors for minimum ionizing particle tracking using non-epitaxial silicon substrate[J]. IEEE Transactions on Nuclear Science, 2004, 51(4): 1 613-1 617.

[4] 李冬梅,皇甫麗英,王志華,等. 不同設計參數MOS器件的γ射線總劑量效應[J]. 原子能科學技術,2007,41(5):522-526.

LI Dongmei, HUANGFU Liying, WANG Zhihua, et al. γ-radiation total dose effects of different sized MOS devices[J]. Atomic Energy Science and Technology, 2007, 41(5): 522-526(in Chinese).

[5] 范雪,李威,李平,等. 基于環形柵和半環形柵N溝道金屬氧化物半導體晶體管的總劑量輻射效應研究[J]. 物理學報,2012,61(1):016106.

FAN Xue, LI Wei, LI Ping, et al. Total ionizing dose effects on N-channel metal oxide semiconductor transistors with annular-gate and ring-gate layouts[J]. Acta Phys Sin, 2012, 61(1): 016106(in Chinese).

[6] 曹建忠. 半導體材料的輻射效應[M]. 北京:科學出版社,1993:69-80.

[7] SAYED I E, TONY Y C, ERIC R F, et al. Design of radiation hard CMOS APS image sensors in a 0.35-μm standard process[J]. SPIE Proceedings, 2001, 4306: 50-59.

[8] LEO H C B, SUZANA D, MILTON F R, Jr, et al. Layout techniques for radiation hardening of standard CMOS active pixel sensors[J]. Analog Integrated Circuits and Signal Processing, 2008, 57(1-2): 129-139.

[9] 孟麗婭,劉澤東,胡大江,等. CMOS APS用移位寄存器抗SEU加固方法[J]. 原子能科學技術,2012,46(增刊):577-581.

MENG Liya, LIU Zedong, HU Dajiang, et al. SEU-hardened design for shift register in CMOS APS[J]. Atomic Energy Science and Technology, 2012, 46(Suppl.): 577-581(in Chinese).