基于SIXS-ASIC的半導體傳感器信號讀出電子學系統的研制

徐英姿,余慶龍,梁金寶,荊 濤,孫 瑩

(1.中國科學院 國家空間科學中心,北京 100190;2.中國科學院研究生院 北京 100049)

基于SIXS-ASIC的半導體傳感器信號讀出電子學系統的研制

徐英姿1,2,余慶龍1,梁金寶1,荊 濤1,孫 瑩1

(1.中國科學院 國家空間科學中心,北京 100190;2.中國科學院研究生院 北京 100049)

介紹了一種用于半導體傳感器信號讀出的專用集成電路(ASIC,Application -Specific Integrated Circuit)的基本結構和工作原理,分析其測試需求,設計并實現了基于該ASIC芯片的探測器讀出電子學系統。描述了測試系統的主要硬件電路設計以及對該芯片的控制流程,上位機通過USB與該電子學系統進行雙向通訊,并利用FPGA對該ASIC芯片進行時序控制以及數據采集。最后,對測試系統進行功能測試,采用信號發生器給系統注入模擬不同沉積能量的半導體傳感器信號,得到能譜圖及相應的線性響應曲線。最后,分別用放射源90Sr/90Y和207Bi對該電子學系統進行性能測試,得出各自的能譜圖。

ASIC芯片;測試系統;FPGA;信號讀出

隨著半導體技術的迅速發展,很多新型的半導體探測器,如硅條探測器、二維像素探測器、SDD等,得到了快速發展[1],并逐步應用到空間輻射環境監測中,為衛星運行提供了安全保障。這些新型探測器大部分都具有讀出密度高、通道數多等特點,傳統的基于分離元件組成的電子學系統已經很難滿足這些要求,因此具有功耗小、集成度高的ASIC芯片正慢慢取代傳統電子學系統,被廣泛應用于半導體傳感器信號讀出電子學中[2-3]。

SIXS-ASIC是RAL為歐空局的SIXS[4](SIXS,The Solar Intensity X-ray and particle Spectrometer)項目研發的一款傳感器信號讀出ASIC芯片。本文基于該ASIC芯片,研制了一套半導體傳感器信號讀出電子學系統,并對該系統進行了詳細測試。

1 SIXS-ASIC芯片概述

SIXS-ASIC采用0.35μm CMOS工藝,如圖1所示,其內部集成了8個互相獨立的傳感器信號處理通道,其中6個Si半導體傳感器信號處理通道,2個碘化銫(CsI)閃爍探測器信號處理通道。每個通道包含電荷靈敏前置放大器,CR-RC濾波成形電路,峰值保持電路,閾值設置及閾值比較電路。8個通道通過多路選通器,共用一個ADC進行信號峰值采集。SIXS-ASIC還設計了一個串行配置接口,可方便設置內部各工作點的偏置電壓、電流,比較閾值,以及ADC等相應參數。SIXS-ASIC的相關參數如表1所示。

圖1 SIXS-ASIC結構框圖Fig.1 Block diagram of SIXS-ASIC

表1 SIXS-ASIC主要性能參數Tab.1 The main performance parameters of SIXS-ASIC

整個ASIC內部的地被嚴格的分為數字地和模擬地,從而降低了系統的噪聲。而且,其內部的數字邏輯都采用了三模冗余邏輯觸發器,這樣可以有效避免單粒子翻轉(SEU,Single Event Upset)事件的發生。以上這個優勢使得這款ASIC可以很好的適應于SEU高發的空間粒子探測領域。

2 測試系統的研制

測試系統的主要目的是通過FPGA給SIXS-ASIC芯片提供控制信息并且進行適當的配置,再接收ASIC芯片發出的科學數據,并對接收到的數據進行處理,最后上傳至上位機。本節主要介紹了測試系統的整體電路設計、主要模塊的實現方法及SIXS-ASIC芯片的工作流程。

2.1 測試系統的整體電路設計

2.1.1 電路整體框架

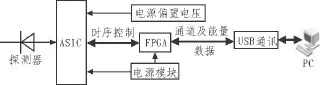

基于該芯片的信號電子學讀出性能測試系統有4個主要模塊:電源模塊(高壓和供電),FPGA模塊,ASIC模塊,USB通訊模塊。如圖2所示。

圖2 SIXS-ASIC測試系統結構框圖Fig.2 Block diagram of SIXS-ASIC test system

其中,電源模塊主要用于給傳感器提供高壓和給整個系統供電。USB通訊模塊實現了上位機和FPGA之間的雙向通訊,可以簡單通過PC端對整個系統進行實時控制,也可以接收到系統輸出的科學數據。

2.1.2 系統運作流程

ASIC芯片接收探測器輸出的模擬信號,該信號在ASIC內部經過相應的信號處理(見圖1),最終由片內的ADC將模擬信號轉成數字信號傳送到FPGA控制單元。FPGA接收和處理由ASIC芯片發送出來的科學數據,將接收到的能量的數據以及通道的數據進行整合,簡單處理后存入FPGA內部的RAM中。最后由PC端發送出控制信息,利用FPGA將采集的數據通過串口轉USB接口發送給PC端的界面程序進行處理并實時顯示,得到能譜圖和科學數據[5]。同時也可以將PC端的控制數據通過USB通訊模塊傳到FPGA,通過FPGA實現對ASIC的實時控制。

2.1.3 系統數據RAM存儲

在FPGA對科學數據進行存儲的過程中,由于測試系統對信息實時存儲的要求較高,因此采取乒乓存儲數據的方法來存儲數據,原理如圖3所示。乒乓存儲的處理流程[6]為:輸入數據流通過輸入數據選擇單元將數據流等時分配到兩個數據緩沖區,數據緩沖模塊選擇雙口RAM。第一個周期,將輸入的數據流緩存到數據存儲單元A;第二個周期,通過輸入數據選擇單元切換,將輸入的數據流緩存到數據存儲單元B,同時將數據存儲單元A的緩存的第一個周期數據通過輸出數據選擇單元的選擇,輸送到數據處理單元即上位機讀取,再進行處理,如此循環。

圖3 乒乓存儲Fig.3 Ping-pong storage

實際運用中,采用FPGA內部中的IP核——RAM核,選擇2塊雙端口RAM。其中一塊存儲單元讀取數據的時候,另外一塊存儲單元進行寫入數據的操作。這樣系統可以同時進行讀寫操作,效率更高,使用方便。而且還可以避免板級間的干擾,既節省印制板空間又節約成本。

2.2 測試系統的數據采集和PC端顯示

PC端對系統數據的獲取直接通過USB模塊實現,圖4是在Lab View 8.6平臺下開發的數據獲取軟件界面,這是整個系統人機交換的界面。其可實現以下4項基本功能:在界面直接更改ASIC的96位配置數據流,修改ASIC的工作參數來達到對ASIC做初始化配置或根據要求做重配置的目的;更改從FPGA內部RAM中接收科學數據的頻率;接收FPGA發送過來的數據并解包,得出每個通道對應的科學數據,顯示于圖4中并進行實時存儲;將數據進行簡單的處理,畫出其能譜圖。

3 測試結果及分析

3.1 ASIC芯片測試系統的線性度測量

3.1.1 線性度測量原理

對測試系統進行功能測試,使用信號發生器產生下降沿跳變脈沖信號,該脈沖信號經電容微分后可用來模擬物理實驗探測器的輸出信號。測試脈沖經過0.6 pF的輸入電容交流耦合到ASIC的輸入端,由此來測試該傳感器信號讀出電子系統的線性度,其等效電路圖如圖5所示。

圖4 PC端控制軟件界面Fig.4 The control software interface of PC

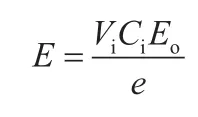

可以得出,信號發生器的輸入幅值與其等效能量E的關系,表達式為:

圖5 信號發生器連接信號電子學等效電路圖Fig.5 Equivalent circuit schematic of signal generator connected to signal electronics

其中,Vi為信號發生器的輸入信號電壓,Ci為耦合電容,E0為硅半導體傳感器平均電離能,E0=3.6 eV,e為電荷常量,e=1.6×10-19C。

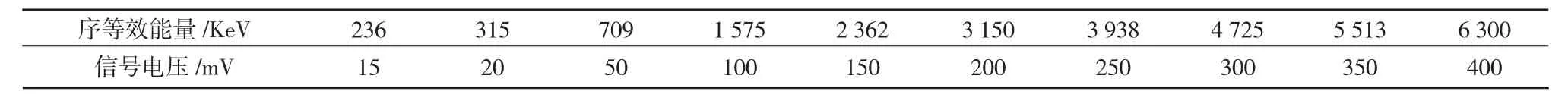

由上面公式,可以得出信號發生器輸入信號幅值與半導體傳感器粒子沉積能量的近似等效關系,表2列出了部分輸入信號幅值及其對應的等效能量。

表2 輸入信號電壓與對應等效能量Tab.2 Voltage of input signal and equivalent energy

3.1.2 線性度測量結果

將信號發生器產生的信號的頻率調為固定值1 kHz,幅值為15~460 mV,步進長度為5 mV。利用這種方式對ASIC的8個通道依次進行測試,得出每個通道對應幅值的科學數據。

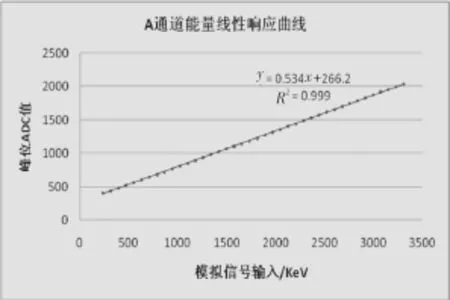

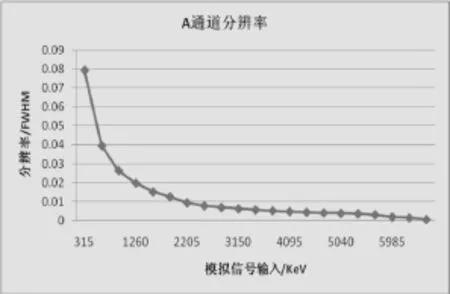

圖6是A通道輸出幅值與模擬信號輸入的線性擬合曲線,圖7是該通道分辨率與模擬信號輸入的擬合曲線。從圖6的曲線圖可以看出,ASIC能量響應線性擬合值R2≥0.99,說明輸入信號從15~460 mV(即能量值為236~7 000 KeV)間,系統都有很理想的線性度。從圖7中可以得出,ASIC采集到的能譜分辨率均好于7.9%。而且,由測試結果可知,ASIC的8個通道都很獨立,沒有串擾。

圖6 A通道輸出幅值與模擬信號輸入的線性擬合曲線Fig.6 Linear regression curve of A channel output amplitude and analog signal input

3.2 放射源下的能譜測量

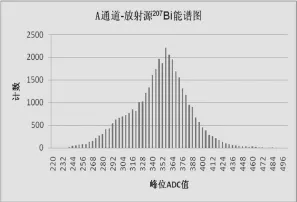

將完整的測試系統接上50 V的高壓電源,并將其中一個輸入端與探測器相連,分別使用放射源90Sr/90Y和207Bi對該信號讀出測試系統進行放射源實驗,由此得到能譜圖。從圖8中可以看出,對放射源207Bi,能得到很漂亮的全能峰能譜圖,分辨率等于13.48%@168.16KeV。而對于放射源90Sr/90Y下的射線,測試系統得不到其全能峰能譜圖。

圖7 A通道的分辨率與輸入信號的擬合曲線Fig.7 Fitting curve of the resolution and the input signal of A channel

圖8 放射源207Bi下A通道獲得的能譜Fig.8 The spectrum under radioactive sources 207Bi of A channel

4 結 論

由上述結論可知,基于SXIS-ASIC所研制的半導體傳感器讀出電子學系統,對在236 KeV到7 000 KeV間的能量值,都有非常理想的線性響應度。經測試,在放射源207Bi下,其能得到很漂亮的全能峰能譜圖,分辨率約等于13.48%@168.16 KeV。而且,該測試系統能很方便的對SIXS-ASIC進行配置,極大的方便了操作。

[1] 孟祥承.新型半導體探測器發展和應用[J].核電子學與探測技術,2004,24(1):87-96.

MENG Xiang-cheng,Development and application of new semiconducting detector[J].Nuclear Electronics & Detection Technology,2004,24(1):87-96.

[2] 千奕.硅條傳感器信號ASIC 芯片測試系統電路設計[J].核技術,2008,31(3):229-232.

QIAN Yi.A testing system circuit for front-end ASIC of silicon strip detector[J].Nuclear Techniques,2008,31(3):229 - 232.

[3] 程澤浩.基于ASIC的Si- PIN 探測器讀出系統[J].核電子學與探測技術.2009,29(1):186-189.

CHENG Ze-hao.A Si-PIN readout system based on ASIC[J].Nuclear Electronics&Detection Technology,2009,29(1):186-189.

[4] Huovelin J.Solar Intensity X-ray and particle Spectrometer(SIXS)[J].Planetary and Space Science,2010(58):96-107.

[5] 余慶龍.HXMT高能電子學測試系統的研制[J].核電子學與探測技術,2010,30(8):1003-1007.

YU Qing-long.Development of the test system for ES /HE of HXMT[J].Nuclear Instruments and Methods in Physics Research,2010,30(8):1003-1007.

[6] 錢黃生.基于FPGA雙RAM乒乓操作的數據存儲系統的研究[J].科技信息,2010(21):93-96.

QIAN Huang-sheng.Research of data storage system based on dual RAM Ping-pong operation of FPGA [J].Science & Technology Information,2010(21):93-96.

Design of the system of semi-conductor detector readout electronic based on SIXS-ASIC

XU Ying-zi1,2,YU Qing-long1,LIANG Jin-bao1,JING Tao1,SUN Ying1

(1.National Space Science Center,China Academy of Sciences,Beijing 100190,China;2.Graduate School of the Chinese Academy of Sciences,Beijing 100049,China)

This article introduced the basic structure and principal of an ASIC chip for front-end readout of semiconductor detector and analyzed its test requirements,and a testing system for the detector readout electronics based on the ASIC chip was designed and implemented. The main circuit,the control flow of the ASIC chip,the realization of timing control for the chip and data acquisition based on FPGA,and the implementation of communication of the ASIC chip and PC by using the USB were introduced.The semiconductor sensor signal which was simulated in different depositional energy was injected into the system by using signal generator,and the energy spectrum and then the linear response curve was achieved.In the end,the testing results of the system under90Sr/90Y and207Bi radioactive source were given.

ASIC chip;test system;FPGA;front-end readout

TN4

A

1674-6236(2014)11-0054-03

2014-03-01 稿件編號:201403003

國家自然科學基金資助項目(Y32113BA9S)

徐英姿(1988—),女,湖南邵陽人,碩士。研究方向:空間環境中高能粒子探測。