基于SOPC的UART IP核設計與驅動開發及系統移植

崔旭晶,李天雷

(1.沈陽理工大學 信息科學與工程學院,遼寧 沈陽 110015;2.中航工業沈陽發動機設計研究所 遼寧 沈陽 110015)

基于SOPC的UART IP核設計與驅動開發及系統移植

崔旭晶1,李天雷2

(1.沈陽理工大學 信息科學與工程學院,遼寧 沈陽 110015;2.中航工業沈陽發動機設計研究所 遼寧 沈陽 110015)

設計基于SOPC嵌入式系統的UART IP核,依據UART協議,采用Verilog HDL進行各模塊設計,使用ModelSim、Quartus II作仿真驗證及綜合,結果表明該UART IP核功能正確,穩定可靠。根據Avalon總線接口協議實現UART在系統總線上的掛載,建立SOPC嵌入式硬件系統,進行UART IP核驅動開發。利用超級終端實現嵌入式系統與上位機之間的通信,并成功移植uClinux操作系統,實現對嵌入式系統的高級控制。

SOPC;UART;Avalon總線;IP核;uClinux.

計算機通信主要通過串口、并口和網絡,UART是計算機串行數據通信的重要部分,而對嵌入式系統的訪問主要通過UART通信,UART IP核在FPGA開發中應用廣泛,可移植到專用ASIC設計中。SOPC嵌入式技術是一項軟硬件協同的設計技術,它融合了MCU、ASIC、DSP等器件的優點,具有可編程的靈活性和豐富的IP核支持,為控制系統設計提供了一種更為靈活高效的解決方案[1]。uClinux操作系統是針對沒有MMU(內存管理器)的CPU,它被使用在具有超前網絡功能的嵌入式領域,如ARM7/9、MIPS、SH、ColdFire and BlackFin等,uClinux操作系統很好地完成了把內核、C庫、應用開發融合在一起的任務,并且占用很少的資源。

1 UART IP核設計

根據UART協議,UART IP核包含4個模塊,分別為寄存器模塊、波特率模塊、發送模塊、接收模塊[2]。

1.1 寄存器模塊設計

由UART協議可知,數據在傳輸之前必須保證兩端設置一致才能使數據正確地傳輸。寄存器模塊主要完成對設計的配置,包括:波特率選擇、數據位選擇、停止位選擇、中斷使能、各種情況下的狀態位。寄存器模塊內部設有4個寄存器:status、rxdata、txdata、control。

1)status寄存器

狀態寄存器由指示UART內部狀態的多個獨立狀態位組成,每個狀態位與控制寄存器中的中斷允許位一一對應。軟件可以隨時讀取狀態寄存器而不會改變其內容。

2)rxdata寄存器

rxdata寄存器用來保存rxd輸入端接收到的數據。當一個新的字符通過rxd輸入端接收完畢時,它被傳送到rxdata寄存器,且狀態寄存器的rflag位被置1;當rxdata寄存器中數據被讀取時,rflag位被清0。在新數據到來之前rxdata寄存器中數據要被讀取,無論數據是否被讀取新的數據都會覆蓋舊的數據。

3)txdata寄存器

主設備將要發送的字符寫到txdata寄存器,發送模塊沒有準備好之前,不應該寫字符到txdata寄存器。狀態寄存器中tflag位表示txdata寄存器狀態,當有一個數據要被發送時tflag位被置1;當數據被裝載到移位寄存器時tflag位清0。在新數據被寫入之前舊數據要被發送出去,否則新數據將會覆蓋舊數據。

4)control寄存器

control寄存器由多個控制位構成,每一位又可分別控制UART核的相應內部操作,軟件可隨時讀取其中的值。control寄存器可以對設計中數據位的位數、停止位的位數、波特率選擇進行配置。control寄存器中的每一位允許status寄存器中相應位irq,當某一個狀態位和它的中斷允許位均為1時,UART核產生一個中斷irq。

1.2 波特率模塊設計

UART傳輸數據是通過數據兩端設備來配置相同波特率以確定數據傳輸速率。波特率模塊的功能是根據不同波特率而產生相應的傳輸時鐘頻率,設計中使用115200、9600兩個波特率,則時鐘分頻數=系統時鐘頻率/波特率。系統時鐘為50 MHz,當波特率為115200時對系統時鐘433分頻,當波特率為9600時對系統時鐘5219分頻。分頻主要通過計數器來完成。

發送模塊時鐘頻率和接受模塊時鐘頻率不一樣,接收時鐘要在發送時鐘的基礎上進行16分頻。

1.3 發送模塊設計

發送模塊的功能是將數據正確地發送出去。就是把從Avalon總線寫入rxdata寄存器的數據,根據UART協議要求的數據格式發送出去,其中包括:串并轉換、數據寄存器轉換、數據移位、開始位和停止位添加。

發送模塊將接收到的數據進行并串轉換后傳送到移位寄存器,移位寄存器向外移數據時在字首加入起始位,在字尾加入停止位。數據傳輸過程通過狀態機實現,數據傳輸分4個狀態,即idle空閑狀態、start起始狀態、shift轉移狀態、stop停止狀態,每個狀態實現不同功能,在信號激勵后進行狀態轉移,4個狀態全部轉換一遍完成一次數據發送。

1.4 接收模塊設計

接收模塊的功能是檢測接收數據。將接收數據去掉起始位,停止位,把數據位串并轉換后傳送到rxdata寄存器,等待系統讀取數據。

對于UART核來說接收模塊比發送模塊復雜,接收模塊要對接收數據進行采樣來檢測其數據的正確性。具體采樣過程是將接收數據采16個樣值,當其中大于8位數為1時說明采樣數據為1;當其中大于8位數為0時說明采樣數據為0。數據傳輸過程依然采用狀態機實現,分為3個狀態,即idle空閑狀態、shift移位狀態、stop停止狀態。接收模塊比發送模塊少了一個start起始狀態,是因為接收模塊中并沒有發送起始位[3]。

1.5 UART IP核仿真驗證

1.5.1 ModelSim仿真

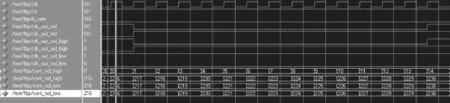

1)波特率模塊

波特率模塊仿真主要看內部計數器是否計數,在相應的計數值是否產生時鐘。波特率模塊仿真波形圖如圖1所示。

圖1 波特率模塊仿真波形圖Fig.1 Baud module simulation waveforms

在cont_rxd_high為13時clk_out_txd變 為1,在cont_ txd_high為216時clk_out_txd變為1,波特率模塊驗證正確。

2)發送模塊

發送模塊仿真主要查看輸入數據是否能夠正確輸出。發送模塊仿真波形圖如圖2所示。

圖2 發送模塊仿真波形圖Fig.2 Send module simulation waveforms

準備發送的數據為11100101,當txstart為1時數據開始發送,先發送起位0,數據位再一位一位地移送出去,發送模塊驗證正確。

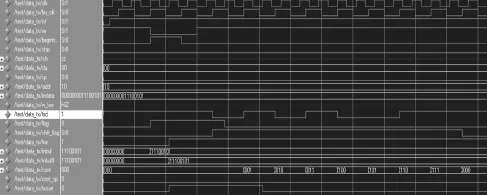

3)接受模塊

接受模塊仿真是查看數據是否正確地接收。接受模塊仿真波形圖如圖3所示。

接受到的起始位為0,數據位10100110被一位一位地傳送到移位寄存器中,接受模塊驗證正確。

圖3 接受模塊仿真波形圖Fig.3 Accepted module simulation waveforms

1.5.2 Quartus II綜合和布局布線

使用Quartus II軟件將SOPC生成的HDL代碼進行綜合和布局布線,最終生成的文件下載到FPGA開發板上。綜合后出現器件列表,其中包含器件型號,使用寄存器數量,使用邏輯單元數量,使用管腳數量,使用PLL數量等。

2 硬件系統搭建

2.1 最小系統搭建

該系統用于對UART IP核測試,系統比較簡單只需幾個組件。使用SOPC Builder硬件平臺工具,配置最小系統組件包括:Nios II/s、On-Chip Merory、JTAG_UART、UART。其中:Nios II/s處理器使用標準型級別就可滿足功能需求,不需要選中MMU(內存管理器)。On-Chip Merory有兩個片上存儲器RAM和ROM,RAM存儲數據,由于設計將會使用Printf函數,RAM必須選擇64KB以上;ROM存取程序,由于程序不大選擇8KB即可。UART用于測試自定義UART IP核。首先將UART IP核加到SOPC組件中,同時系統會生成tcl文件,該文件描述了自定義IP的所有系統,可以修改此文件對自定義IP的所有信息進行修改。JTAG_UART用于對程序下載調試[4]。最小系統的SOPC組件列表如圖4所示。

圖4 最小系統的SOPC組件列表Fig.4 SOPC component list of the minimum system

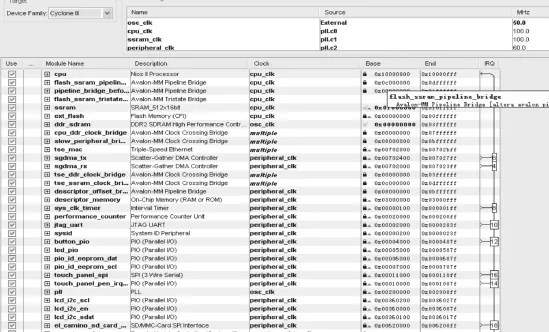

2.2 嵌入式系統搭建

該系統用于完成uClinux系統移植,系統比較復雜需要大量組件。主要組件有:Nios II/f、Pipeline Bridge、Tristate Bridge、SRAM、Flash、DDR SDRAM、Clock Crossing Bridge、DMA、PIO、Triple-Speed Ethernet、PS2、PLL、Pixel Conventer、Video Sync Gengrator等[6]。其中:Nios II/f處理器是CPU的最高配置,由于系統比較復雜,需要快速型級別才能滿足系統需求。DDR SDRAM控制器,由于SDRAM的讀取速度比Flash快很多,通常用來運行軟件程序。Clock Crossing Bridge時鐘橋,用于不同時鐘頻率下的數據傳輸,內部主要由異步FIFO組成。PLL鎖相環,當系統需要多個時鐘驅動時,僅靠一個外部晶振不可能滿足要求,必須加入PLL提供不同時鐘,這里60MHZ用于低速外部接口控制器,100MHZ給CPU供時,133MHZ給SDRAM供時。Pixel Conventer用于RGB數據傳輸。Video Sync Gengrator用于控制LCD[6]。嵌入式系統的SOPC組件列表如圖5所示。

在實際搭建嵌入式系統時,許多器件配置不僅要考慮外圍芯片的時序要求,還要考慮內部系統總線的時序要求。每個組件都必須有自己的時鐘、基地址,為每個組件正確地分配地址是比較復雜的。由于CPU的尋址空間為4GB,通常把0x00000000到0x1FFFFFFF作為寄存器地址空間。可以把同一個時鐘頻率的組件劃為一個地址空間區。組件的實際地址等于基地址加地址偏移量。

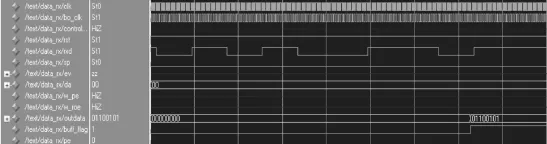

3 UART 驅動開發

UART驅動開發是利用超級終端實現SOPC嵌入式開發板(Altera公司的EP3C40 FPGA開發套件V6工作平臺)與上位機之間的正常通信,即PC機向開發板發送數據,同時開發板把接收的數據再發送給PC機,在超級終端上回顯。

Nios II IDE集成開發環境用于完成基于Nios II系統的軟件開發和調試,Nios II IDE提供了HAL系統庫里的兩個重要文件,一個為system.h系統描述文件,提供Nios II系統硬件的軟件描述;另一個為io.h文件,io接口操作文件提供了3種對io口操作的函數,即對8、16、32位數據操作函數,由于UART IP核采用32位靜態地址對齊方式,故軟件 使用對32位數據操作函數IORD、IOWR,這兩個函數的功能是將數據寫/讀到基地址+偏移量*數據總線位數/8。

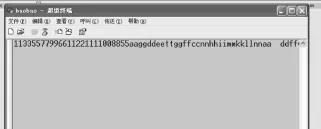

UART的測試軟件流程為:首先對control寄存器初始化(寫入0x0000),然后系統不斷查詢status寄存器的rflag位,當rflag位為1時說明rxdata寄存器接收了一個新數據;當tflag位為0時說明txdata寄存器為空可以寫入數據,將接收到的數據寫到txdata寄存器中,發送給PC機,最終在超級終端上能夠顯示發送和接受的數據。

圖5 嵌入式系統的SOPC組件列表Fig.5 SOPC component list of the embedded system

在使用超級終端測試之前必須對超級終端進行設置,在超級終端屬性欄的“ASCII碼設置”里,把“ASCII碼接收”、“ASCII碼發送”全部選中,只有這樣才能在超級終端上查看發送的數據。經測試,每發送一個數據都能在超級終端正確回顯,如圖6所示。

圖6 在超級終端上的數據回顯Fig.6 Data on the HyperTerminal echo

4 uClinux系統移植

4.1 建立有關文件系統

向SOPC嵌入式系統開發板移植uClinux操作系統主要是為了更自主地開發,實現系統更高級功能。uClinux操作系統是針對沒有內存管理器的微處理器的操作系統。這里移植的nios2-linux-20100621,需要從Altera官方網站下載系統源代碼,由于該系統使用git進行管理,在移植系統之前必須具備EPEL安裝包,其為遠程軟件倉庫管理軟件。nios2-linux-20100621軟件包里面幾乎沒有什么軟件包,必須安裝git、make、gcc等相關軟件。要在PC機上編譯Nios II程序,需要安裝交叉編譯器nios2gcc-20080203.tar.bz2。

4.2 移植系統

系統移植需要兩個很重要的文件nios.h和config.c。開發包通過nios.h文件來管理SOPC組件與uClinux內核驅動設備的地址映射;config.c文件包含了大部分設備驅動支持,各個設備要通過讀取該文件來獲得設備驅動支持。

在移植前必須將兩個文件里的內容對比一下,檢查兩個文件的宏定義是否相同。進入uClinux-dist目錄輸入make menuconfig配置內核,如果第一次配置內核必須選擇默認選項,再生成鏡像文件,保存退出后系統會顯現有錯誤,因為沒有指定PTF文件(PTF文件是SOPC生成的系統文件,里面定義了所有關于SOPC組件的信息),把系統生成的PTF文件復制到/opt目錄下,定義為nios.ptf。在uClinux-dist目錄下執行配置硬件信息文件命令make vendor_hwselect SYSPTF=/opt/nios.ptf之后,系統提示選擇CPU以及運行程序的存儲器,選擇后就可以配置內核了。

Nios2-linux-20100621通過git來管理,輸入git-branch-l查看分支列表,轉到test-nios2 branch目錄下。執行make menuconfig后,進入系統自定義配置列表,可以根據自己需要配置內核,比如開發板類型選擇。控制臺選擇UART,保存退出系統會進入應用程序配置,可以在這里配置文件系統GUI、Busybox等,保存退出后,輸入make命令來制作系統映像文件,映像文件生成在image文件里的zImage,到此uClinux移植完畢[7]。

啟動nios2 command shell,將生成的zImage燒寫到開發板的SDRAM中,同時打開超級終端,超級終端顯示的系統加載如圖7所示。

在超級終端中輸入ls命令,到此系統移植成功,超級終端顯示的系統文件如圖8所示。

5 結束語

使用Altera公司的Cyclone III為FPGA開發芯片,經過基于Avalon總線的UART IP核設計及其驅動過程,在SOPC嵌入式硬件系統[8]中加以實體性驗證,表明自定義設計的UART IP核各項功能均達到預期要求,實現了UART的通信功能和uClinux操作系統移植。這種設計方法大大縮短了嵌入式系統的軟硬件開發時間,增加了系統的靈活性、擴展性和實用性,有效地提高了系統的開發效率,是當今科技含量較高的設計思路及實現方法,具有廣闊的應用領域和前景。

圖7 超級終端顯示系統加載Fig.7 HyperTerminal display system load

圖8 超級終端顯示系統文件Fig.8 HyperTerminal display system files

[1] 周立功.SOPC嵌入式系統基礎教程[M].北京:北京航空航天大學出版社,2006:16-21.

[2] 李秋菊,楊銀堂,高海霞.基于Verilog HDL的UART IP的設計[J].半導體技術,2007,32(6):520-523.

LI Qiu-ju,YANG Yin-tang,GAO Hai-xia.Design of UART Based on Verilog HDL[J].Semiconductor Technology,2007,32(6):520-523.

[3] 鄧偉,徐揚婧.基于SOPC技術的異步串行通信IP核的設計與實現[J].電子設計工程,2012,20(3):185-188.

DENG Wei,XU Yang-jing.A UART IP Implementation Based on SoPC[J].Electronic Design Engineering,2012,20(3):185-188.

[4] 王剛,張瀲.基于FPGA的SOPC嵌入式系統設計與典型實例[M].北京:電子工業出版社,2009:250-282.

[5] Altera Corporation.SOPCBuilderUserGuideVersion1.0[EB/OL].[2010-12-01].http//:www.altera.com.cn/literature/ug/ug_sopc_ builder.pdf.

[6] Altera Corporation.Embedded Peripherals IP User Guide[EB/OI].[2010-12-01].http//:www.altera.com.cn/literature/ug/ug_ embedded_ip.pdf.

[7] 巨政權,原亮,滿夢華,等.SOPC系統建立及uClinux移植實現[J].微計算機信息,2009,25(11):43-45.

JU Zheng-quan,YUAN Liang,MAN Meng-hua,et al.Establishment of SOPC System with Implementation of uClinux[J].Microcomputer Information,2009,25(11):43-45.

[8] 薛慧敏,武傳華,路后兵.基于SoPC的分布式干擾系統嵌入式網關設計[J].現代電子技術,2011(6):121-123,127.

XUE Hui-min,WU Chuan-hua,LU Hou-bing.Design of distributed jamming system embedded gateway based on SoPC [J].Modern Electronics Technique,2011(6):121-123,127.

UART IP core design and driver development and system transplanted based on SOPC

CUI Xu-jing,LI Tian-lei

(1.School of Information Science and Engineering,Shenyang Ligong University,Shenyang 110015,China;2.AVIC Shenyang Engine Design and Research Institute,Shenyang 110015,China )

UART IP core Design of embedded systems based on SOPC,according to UART protocol,using Verilog HDL conducted each module design,using ModelSim,Quartus II for simulation and synthesis results show that the UART IP core functions properly,stable and reliable.According to the Avalon bus interface protocol UART mounted on the system bus,achieved the establishment of SOPC embedded hardware system for UART IP core driver development.Use HyperTerminal for communication between the host computer and embedded systems,and successfully transplanted uClinux operating system,advanced control for embedded systems.

SOPC;UART;Avalon bus;IP core;uClinux.

TN332

A

1674-6236(2014)11-0121-05

2014-02-19 稿件編號:201402098

遼寧省教育廳高校科研計劃項目(L2010482)

崔旭晶(1964—),女,天津人,碩士,副教授。研究方向:嵌入式技術、集成電路設計。