寬帶數字陣列數字時延技術研究及硬件實現

吳 衛,章文星

(中國船舶重工集團公司第七二四研究所,南京 211153)

寬帶數字陣列數字時延技術研究及硬件實現

吳 衛,章文星

(中國船舶重工集團公司第七二四研究所,南京 211153)

研究了基于數字延時技術的波束合成方法,通過理論推導、仿真證明了其正確性,并給出了硬件實現方法和資源評估,表明了其硬件可行性。

寬帶相控陣;波束合成;數字延遲

0 引 言

在現代戰爭中,為了提高雷達對目標的分辨、識別能力并解決對目標成像問題,新體制相控陣雷達通常采用大瞬時帶寬信號進行收發。由于傳統相控陣雷達是通過控制信號的相位來延遲信號的,在寬帶信號情況下存在波束指向偏移和掃描不準的現象。這種由于孔徑渡越時間帶來的波束 “色散效應”使得雷達工作瞬時帶寬大大受限。本文以某寬帶數字陣列雷達課題為背景,分析了寬帶數字波束形成和窄帶數字波束形成的異同,采用基于分數時延濾波器方法實現了數字寬帶波束合成,并提出了基于分數時延濾波器的數字波束形成的硬件實現方法及資源評估。

1 傳統移相方式進行DBF的弊端及解決方法

數字波束形成(Digital Beam Forming,DBF)是空域濾波的主要形式。假設有N個天線陣元,θ為目標方向,θBK為第k個波束指向,d為相鄰陣元間距,λ為信號波長,信號為s(t)。數字多波束形成器將數字的幅度和相位的權值在所有通道信號求和之前加到每一個輸入信號中。它保留了天線陣列單元信號的全部信息,并可以構成空間受控的一個或多個定向波束從而獲得優良的波束性能。

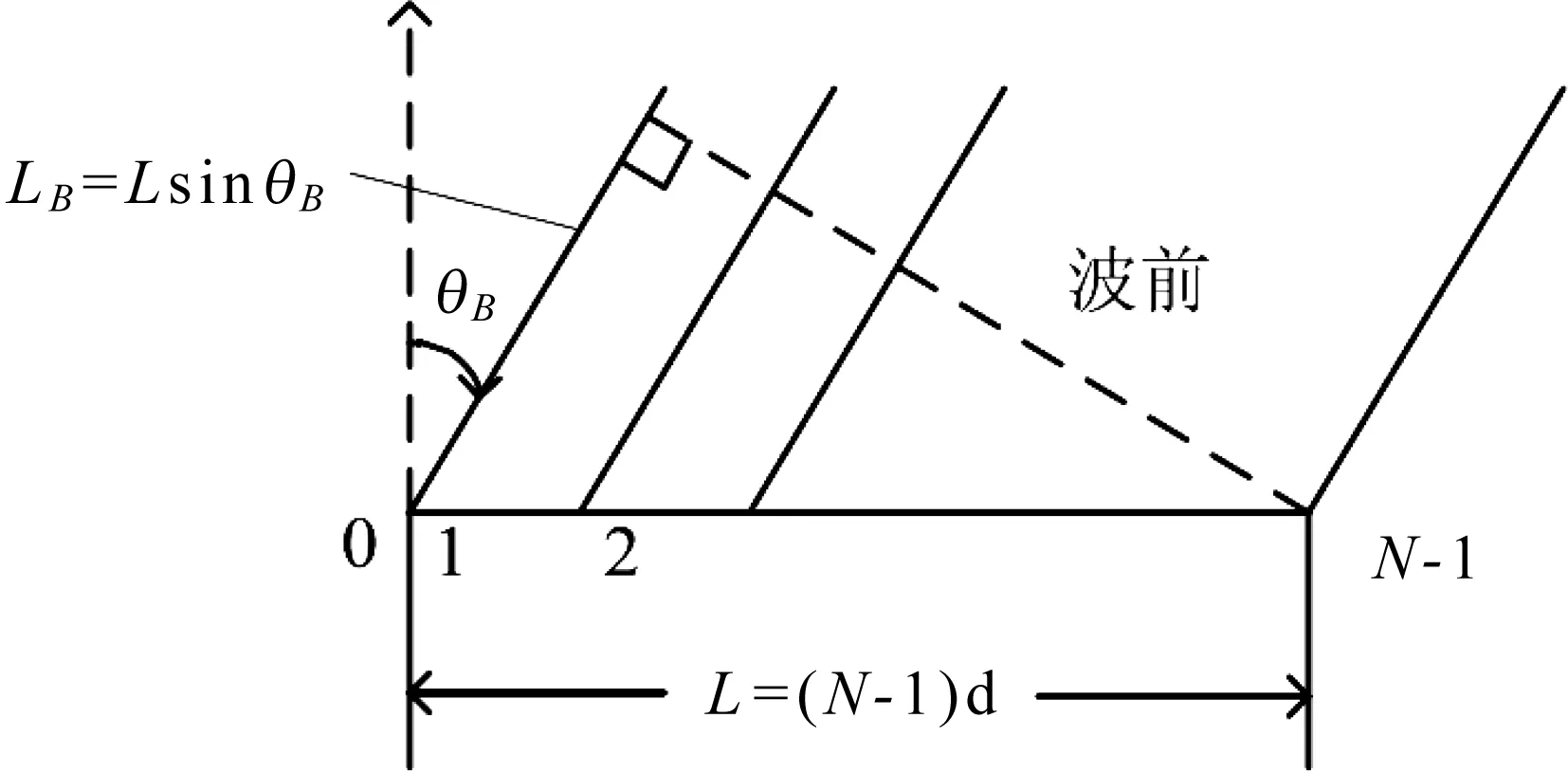

以下以圖1的線陣為例來說明基于移相方式的DBF合成方法。

圖1 線陣 DBF時間延遲示意圖

圖1中,若僅采用移相方式來實現天線波束掃描,天線波束最大值指向θB,則要求相鄰單元之間相移為△φ=(2π/λ)dsinθB,從而應提供的天線兩端移相的相位差φB為

或

或

φB=2πfTAsinθB

其中,L為天線孔徑長度,TA=L/c為天線孔徑長度對應的電波傳播時間,可稱孔徑時間。

(1)

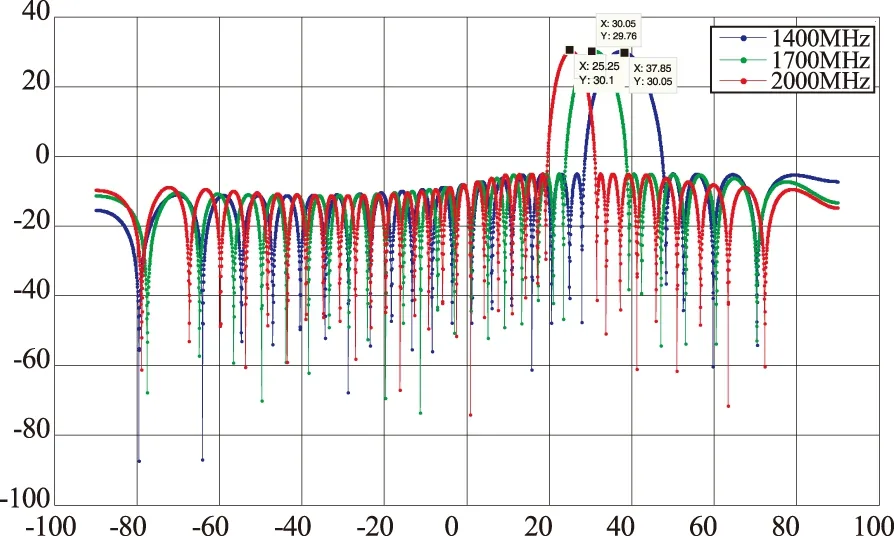

在移相值△φ保持不變的條件下,改變信號頻率f,天線波束指向改變。這種由于f改變導致波束指向變化稱為“色散效應”。由于課題中所處理的瞬時帶寬最大為700 MHz,且寬帶相控陣的孔徑效應導致相控陣雷達波束的指向隨頻率的變化而偏移,如圖2所示,中心頻點在1.7 GHz,波束指向30°,而1.4 GHz和2.0 GHz則指向在37°和25°。

圖2 基于移相方式得到的DBF方向圖

而如果采用直接時間延時,即

△τ=LsinθB/c

(2)

那么

(3)

在式(3)中,因沒有信號頻率,故與信號頻率無關,可保證波束指向θB保持不變。

2 分數延時數字濾波器的原理

常規寬帶脈沖信號,其數學表達式可以表述為

其中,f0為信號的載波頻率,T0為脈沖持續寬度,s(t)表示的是調制信號,而

為了能夠進行數字信號處理,通常下變頻至零中頻,得到基帶I/Q數據,再進行信號分析與處理后的基帶寬帶雷達信號可表示為

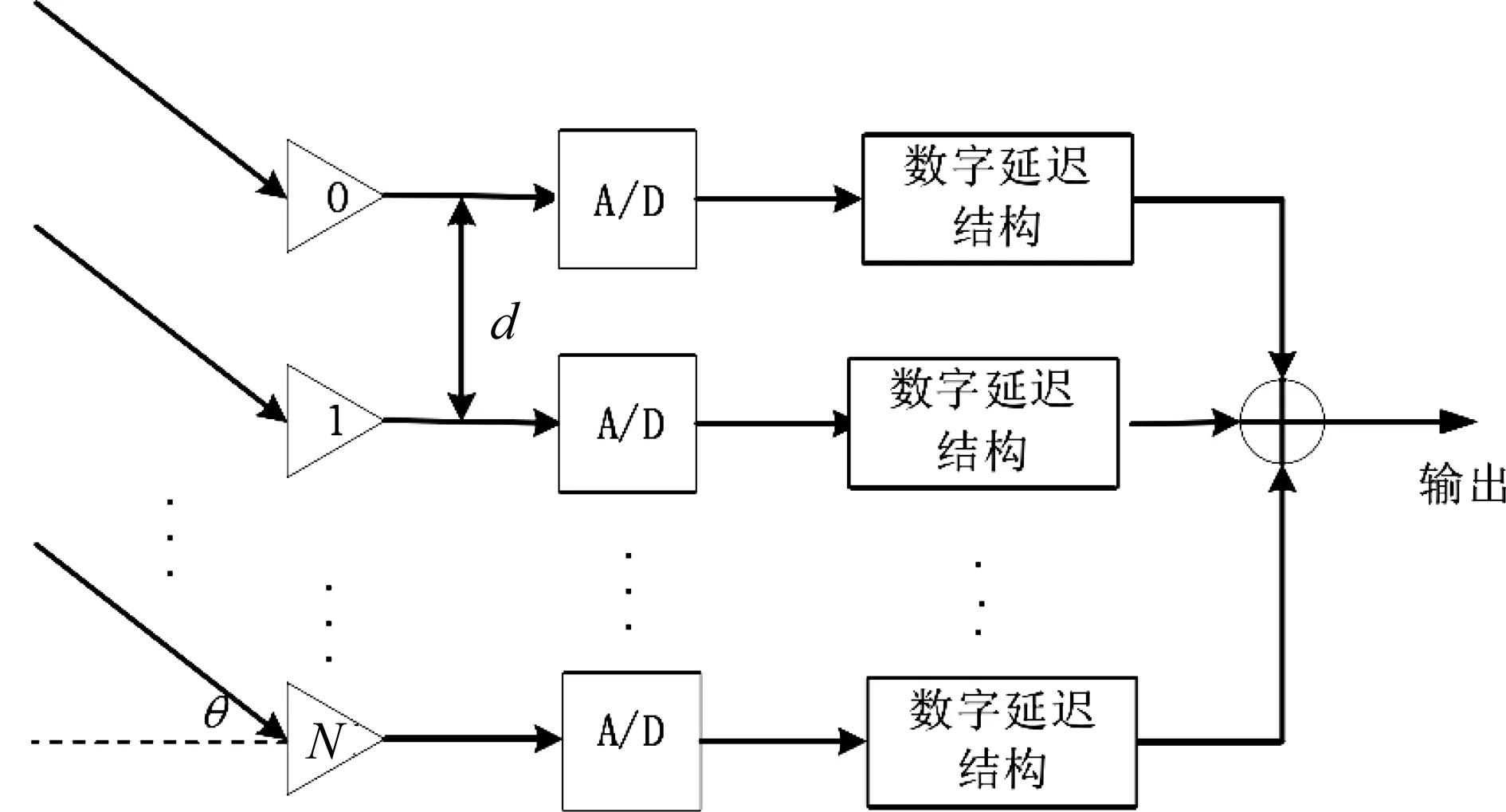

圖3 基于數字延遲的寬帶數字陣雷達接收機結構圖

圖3是基于數字延遲的寬帶數字陣雷達接收機結構。在其所示的均勻線陣中,假設回波信號到達方向為偏離法線θ時,則陣列中相鄰陣元接收到信號的時間差為

△τ=dsinθ/c

其中,d為陣元間距,c是光的傳播速率。如果選擇圖 3 中線陣第0號陣元接收到的回波信號作為參考信號,則第k號陣元的接收到的回波信號形式為

把上式寫成基帶形式并展開可得

(4)

線陣各個陣元收到回波信號后,對式(4)的第2項進行數字移相補償,對其第3項進行時延補償,就可以使各個陣元接收到的信號同相疊加,進而使接收波束指向在預期方向上。圖3 中第k號陣元相對參考陣元回波時延為

τk=k△τ

即

τk=kdsinθ/c

采樣周期為T時,第k號陣元需要補償的時延可表示為

τk/T=L+△

其中L表示整數倍采樣周期時延:

L=round(kdsinθ/cT)

其中,round為四舍五入取整函數,△表示分數倍采樣周期時延, 且有-0.5<△≤0.5:

(5)

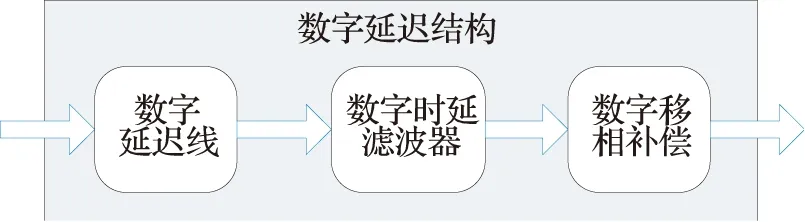

對回波信號進行離散化后,可以設計具有時延D=L+△的分數時延濾波器來補償回波信號的時延。因此,數字延遲結構可以由圖4進行表示。

圖4 數字延遲結構示意圖

寬帶數字陣波束形成實現結構的每一個通道可變數字延遲電路由數字移相器、數字延遲線和分數時延濾波器組成,其中用數字延遲線補償整數倍采樣間隔的時間延遲,用分數時延濾波器補償分數倍采樣間隔的時間延遲,而數字移相器補償的是載波引起的空間相位差。通過改變數字移相器的值、數字延遲線的系數和分數時延濾波器的系數就可實現對各陣元的傳輸時間延遲進行精確的補償。

3 分數延時數字濾波器的設計方法及仿真

在硬件設計上數字延遲線和數字移相補償都比較容易實現。數字延遲線可以利用FPGA中的移位寄存器實現。數字移相補償只是簡單的乘加運算,也比較易于在FPGA中的實現。下面主要介紹分數時延濾波器的實現方法。分數時延濾波器主要是由基于Farrow結構的濾波器實現的,其實現框圖如圖5。

圖5 基于Farrow結構的濾波器實現框圖

由圖5可知,Farrow 結構有M組N階FIR濾波器構成,其中虛線框圖中畫出了第M組N階 FIR 濾波器的CM-1內部結構,其余M-1組N階FIR 濾波器的實現方式與CM相同。它的優點是當時延變化時僅改變時延參數D,就可以獲得不同的分數時延,不用重新加載系數,節省了存儲空間,降低了硬件實現的復雜度。

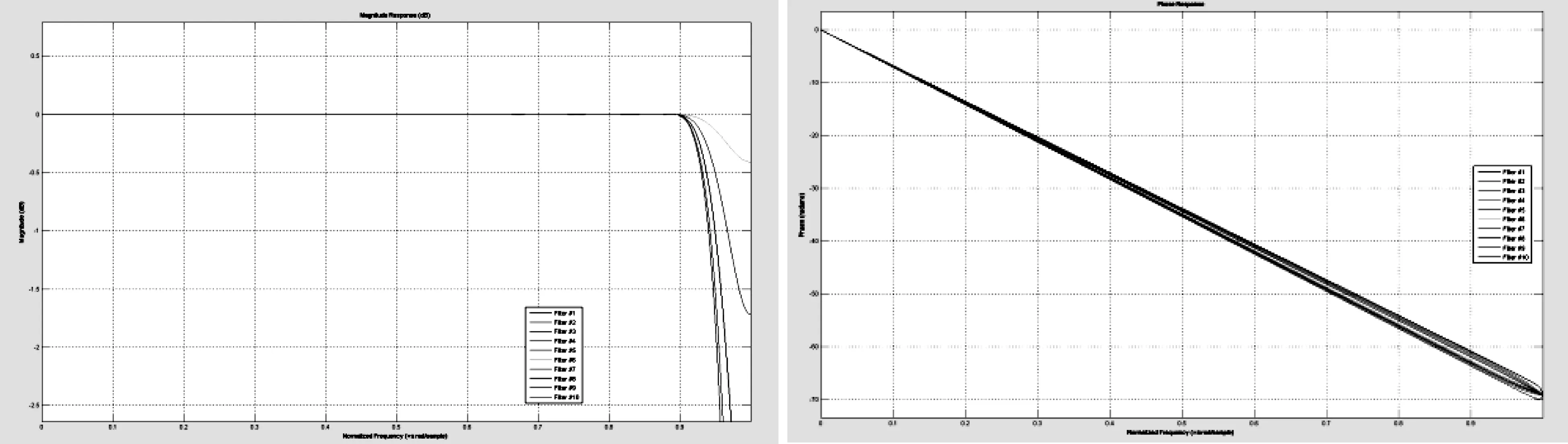

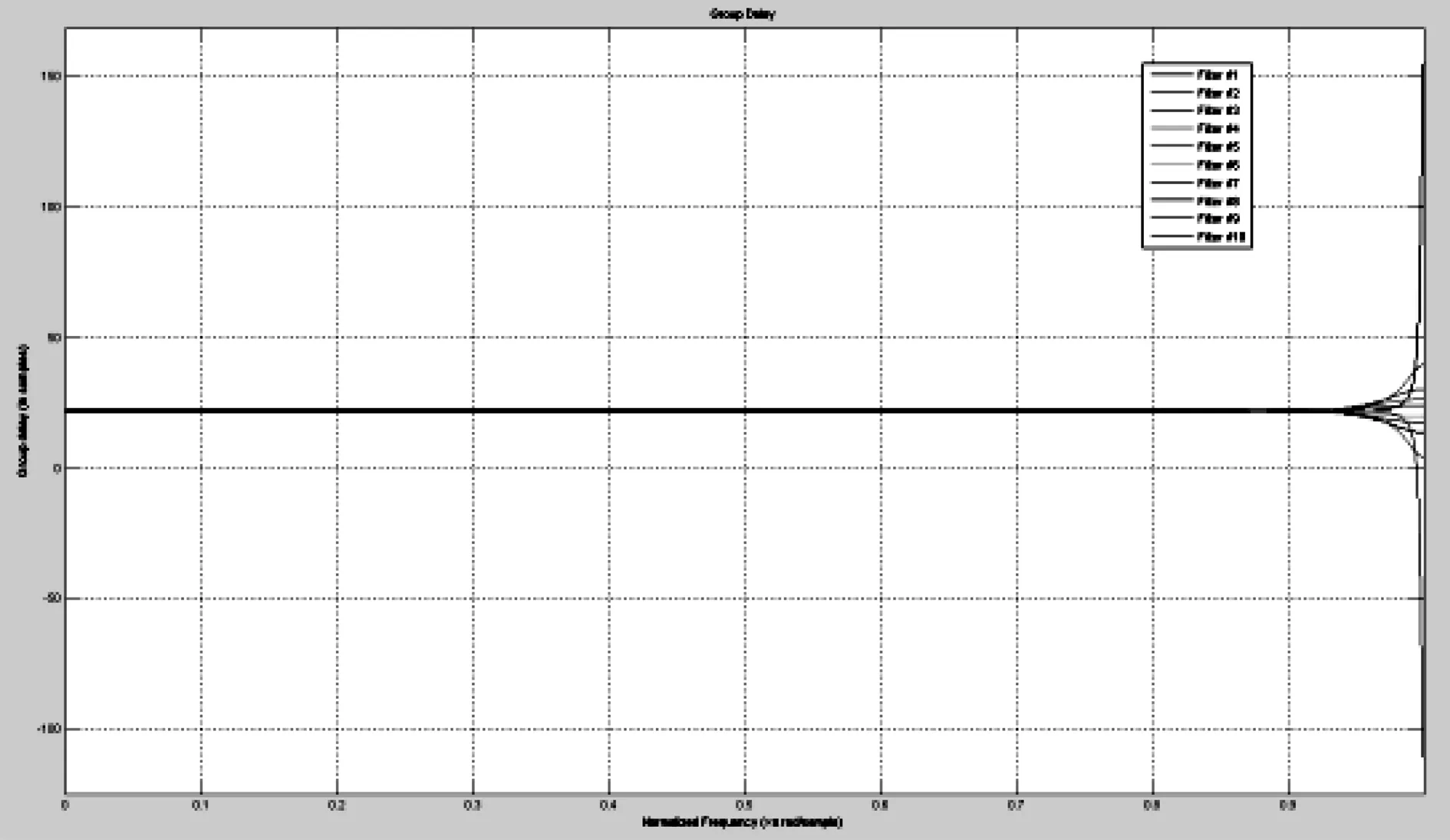

時延參數取[-0.5:0.1:0.5]時獲得的分數延時濾波器的幅相頻率響應及群延遲特性見圖6和圖7。

在實際使用中,可以采用8組不同加權系數的29階FIRCore實現CM-1,CM-2,…,C0模塊,再將8路FIRCore輸出結果和時延參數D的相應階數進行乘加運算就能得到最終的結果。其中,8組FIRCore權值為預先生成而不需要改變的值,而時延參數D隨著掃描方位的變化而實時改變。

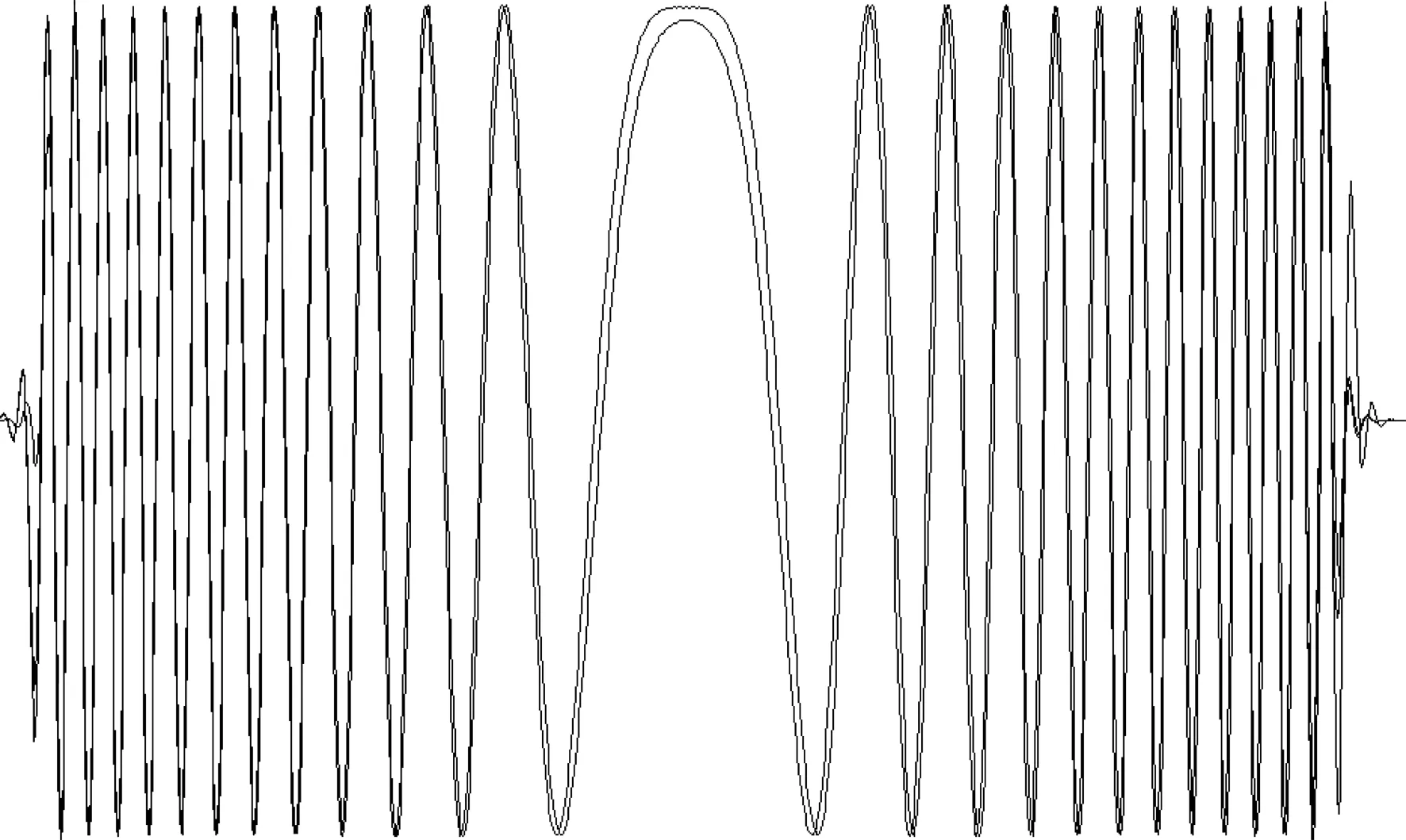

下面仿真了一組信號,驗證延時濾波器的實現。信號的帶寬B為10 MHz,中頻f0為10 MHz,采樣率fs為100 MHz,采樣間隔ts為0.01 μs,脈寬τ為10 μs。

首先將原始信號經過數字下變頻得到I/Q數據,同時將原始信號進行理論延時進行同樣的數字下變頻得到I/Q數據,最后將原始信號的I/Q數據經過時延濾波器,并和理論延時信號的I/Q進行比較,觀察兩者重合程度。

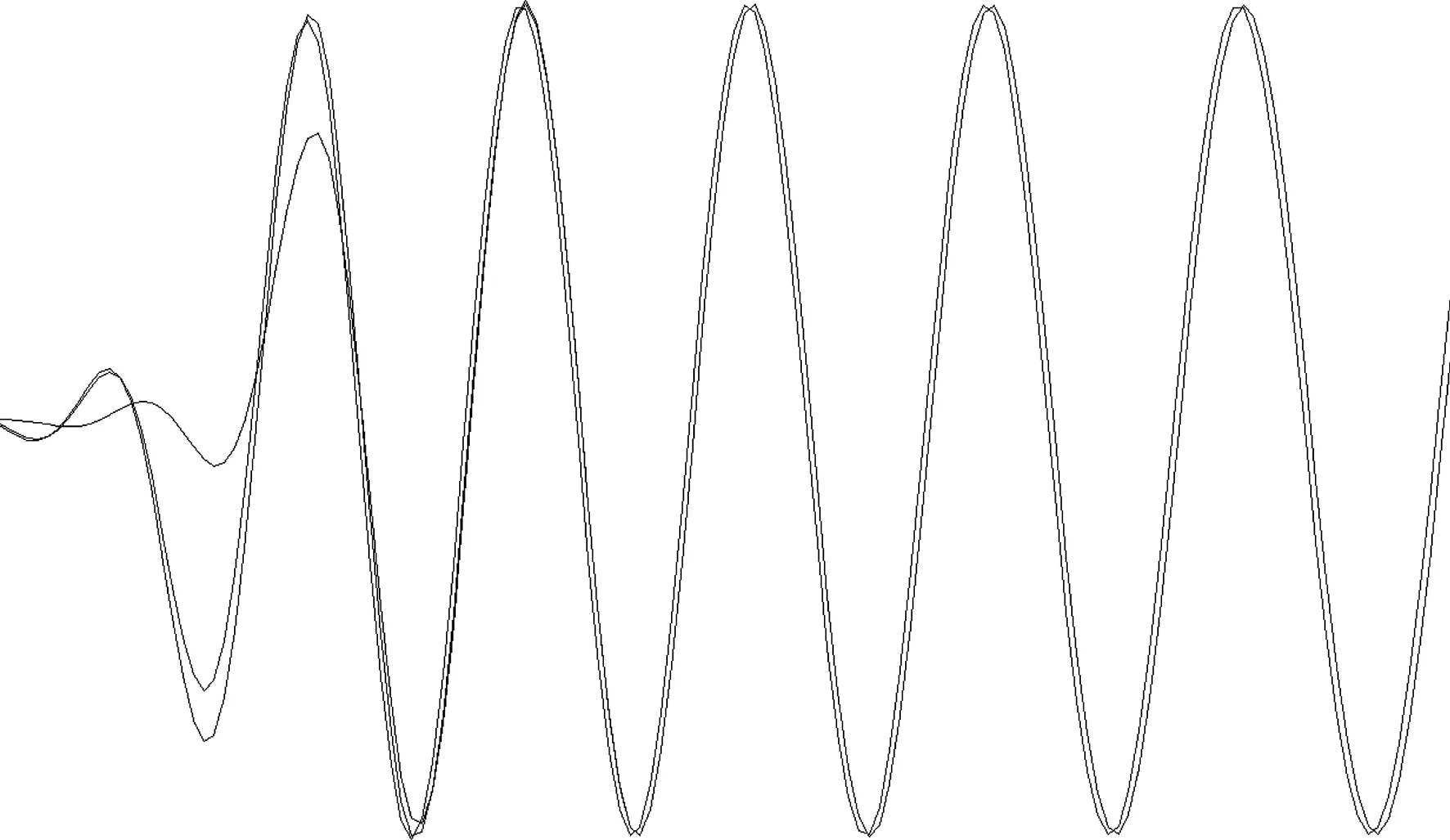

圖8和圖9為將原始信號進行0.104 μs延時(即10.4個ts)得到的結果通過時延參數為10.4的時延濾波器后得到的結果。圖中,藍色表示原始信號理論延時結果的實部,紅色表示原始信號通過時延濾波器后的延時結果的實部,綠色表示原始信號的實部。

(a)幅頻響應 (b)相頻響應

圖6 分數延時濾波器的幅頻響應

圖7 分數延時濾波器的群延遲特性

圖8 時延濾波后得到的結果

圖9 時延濾波后得到的結果放大圖

通過圖8和圖9可以看出,在Farrow濾波器在脈沖信號的起始與結束兩端的輸出結果和理論延遲的結果重合度有誤差,分析這是由于濾波器的瞬態響應導致,而在其他時刻(即濾波器穩態響應后)都能正確重合。

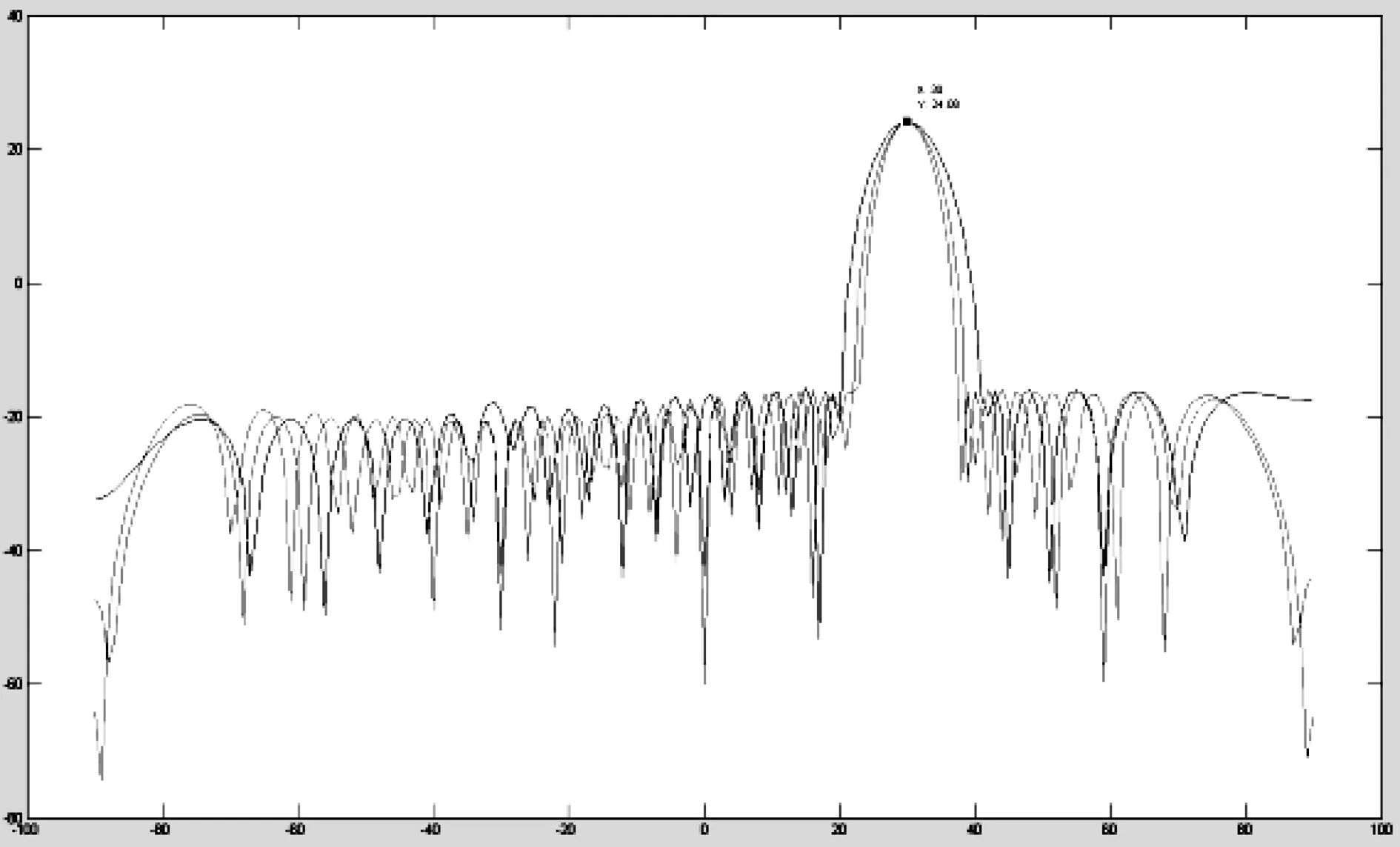

下面分別仿真了采用傳統相位加權和Farrow結構實現分數時間延時得到的寬帶數字陣列雷達的方向圖。

仿真中使用的參數如下:均勻線陣陣元數32,選擇線性調頻信號作寬帶雷達信號,載波頻率為f0=1.750 GHz,時寬Tp=10 μs,輸入三組頻率分別為2 GHz、1.751 GHz和1.410 GHz的單頻信號,采樣率為1.4 GHz,陣元間距為最大頻率對應波長的一半,Farrow結構取298,波束設計指向30°,通過計算機仿真并對結果做Taylor加權,可得天線方向圖如圖10和圖11。

圖10 傳統相位加權得到的DBF方向圖

圖11 分數時間延時得到的DBF的方向圖

可以很明顯看出,使用相位加權法得到的方向圖出現了 “色散”,而使用Farrow結構實現分數時間延時方法得到的方向圖則沒有“色散”。

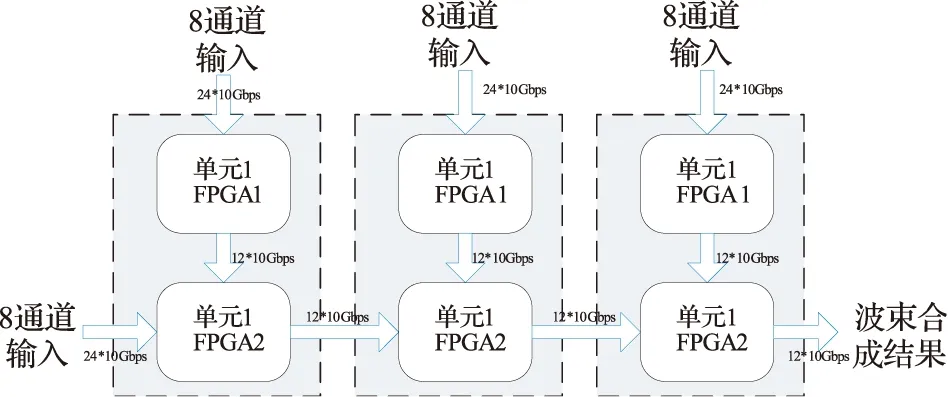

4 硬件實現及資源評估

考慮到信號傳輸能力和FPGA處理能力,寬帶數字DBF硬件將采用多板級聯的方法來實現,最終實現同時二波束的處理。其實現框圖如圖12所示。

圖12 寬帶數字DBF硬件實現框圖

由于本課題對寬帶信號的采樣率高達1.4 GHz,無法利用FPGA進行直接處理,在實際硬件實施時,采用將單路高速數據流分成多路低速數據流的方法,即Demux技術,以多個乘法器并行運算的方式來實現。

設計將每通道分成8路低速數據流。而分數濾波器需要生成8組29階的FIRCORE,由于29階系數是對稱的,因此使用FIRCore的對稱特性可以節省一半資源。所以,I/Q兩路需要8×8×29×2/2=1856個DSP48E;時延參數D取0到7的階數值,需要8個DSP48E(復數乘法器);相位補償需要8個DSP48E(復數乘法器)。XC7V485T內部含DSP48E資源為2800個,完全可以滿足要求。

5 結束語

基于Farrow結構的分數時延濾波器使得通道間信號延遲連續調整成為可能,從而為寬帶數字相控陣的波束形成與掃描技術提供了基礎。本文在對Farrow結構濾波器研究的基礎上,進行了FPGA邏輯仿真和硬件實現資源評估,從而證明了其工程可行性。隨著寬帶相控陣雷達技術的日益發展,基于分數時延技術的陣列天線波束形成方法由于其能明顯改善寬帶大孔徑陣列天線波束指向的“色散效應”這一優越特性,必將會得到越來越廣泛的工程應用。

[1] 張光義.相控陣雷達原理[M].北京:國防工業出版社,2009.

[2] 王德純.寬帶相控陣雷達[M]. 北京:國防工業出版社,2010.

[3] T B Deng. Symmetry based low-complexity variable fractional-delay FIR filters//IEEE International Symposium on Communications and Information Technologies, 2004:194-199.

[4] 范占春.寬帶數字陣數字時延及移相技術研究[D].電子科技大學,2008.

Digital time-delay technology of broadband digit array and its hardware implementation

WU Wei,ZHANG Wen-xing

(No.724 Research Institute of CSIC, Nanjing 211153)

The digital beam forming (DBF) method is studied based on the digital time-delay technology, and verified to be correct through the theoretical deduction and the simulation. The hardware implementation and the resource evaluation indicate the feasibility of the hardware.

broadband phased array; beam forming; digital delay

2014-04-12;

2014-05-15

吳衛(1977-),男,工程師,碩士,研究方向:雷達信號處理技術研究;章文星(1969-),男,高級工程師,研究方向:雷達結構設計。

TN958.92

A

1009-0401(2014)02-0030-05