RISC指令集眾核處理器功能驗證與實現

朱博元,劉高輝,李政運,安述倩

1.西安理工大學自動化與信息工程學院,西安 710048

2.中國科學院計算技術研究所計算機體系結構國家重點實驗室,北京 100190

RISC指令集眾核處理器功能驗證與實現

朱博元1,劉高輝1,李政運2,安述倩2

1.西安理工大學自動化與信息工程學院,西安 710048

2.中國科學院計算技術研究所計算機體系結構國家重點實驗室,北京 100190

眾核技術已成為當前處理器體系結構發展的必然趨勢,如何對眾核處理器設計進行有效而充分的驗證,成為當今IC設計驗證領域的研究熱點之一,也是眾核處理器芯片能否成功流片的關鍵因素之一。目前工業界采用基于仿真的驗證作為主要的驗證方式,重點介紹了以覆蓋率為導向的RISC眾核處理器的功能驗證環境的整體設計,提出了“被動式”的驗證思想,并采用“軟硬件協同驗證”的策略,最終達到每條指令都比對通過的驗證目標,輔以后期階段所引入的時序驗證策略和功耗評估策略,完整地提出了一套芯片驗證平臺搭建和驗證功能實現的方法流程。

眾核處理器;功能驗證;覆蓋率;時序驗證;功耗評估

1 引言

隨著集成電路制造工藝的進步和處理器設計水平的不斷提高,眾核技術已成為當前處理器體系結構發展的必然趨勢。處理器的復雜度呈指數幅度上升,使故障的查找和修復變得越來越困難,如何對眾核處理器進行有效而充分的驗證,成為當今IC設計驗證領域的研究熱點之一,也是其能否最終流片成功的決定性因素。傳統的功能驗證方法主要采用監測并控制其地址與數據總線的方法,這對于高度集成化的眾核芯片,其追蹤系統總線的策略往往不能定位內部故障所在,從而不能進行下一步的分析和修改故障。

基于軟件和硬件分別進行獨立的仿真驗證仍然是目前IC驗證主要應用的功能驗證方式,在此基礎上,本文重點介紹了以覆蓋率為功能驗證導向的RISC眾核處理器的驗證環境的整體搭建,提出了“被動式”的測試驗證思路,并采用“軟硬件協同驗證”的策略,最終達到了處理器運行的每條指令都對比通過的驗證目標。再輔以相應基于成熟EDA工具的功耗和時序分析驗證方式,完整地提出了一套芯片驗證平臺搭建和驗證功能實現的方法流程。

2 眾核處理器驗證環境的搭建

2.1 軟硬件協同驗證的發展現狀

軟硬件協同驗證與傳統的數字系統仿真驗證方法不同,它是針對軟件和硬件系統模塊進行的混合模擬仿真。傳統的系統驗證方法通常是將軟件部分和硬件部分的設計驗證分開獨立進行,二者在確定了設計目標之后就很少再相互考慮。這樣的設計驗證方法在系統設計后期才會發現比如軟硬件接口或在設計初期沒有考慮到的系統功能方面的問題,導致設計資源的浪費與設計周期的延長和開發成本的不斷增加。

軟硬件協同驗證技術的出現很好地改善了這一現狀,它分為外圍硬件模型驗證和處理器核心驗證兩個部分。軟硬件協同驗證通常使用硬件模擬器作為驗證工具,通過執行RTL級設計描述模擬設計的物理實現,其仿真結果取決于設計描述是否正確反映了設計的物理實現,驗證時需要通過測試平臺產生激勵和開發人員檢查響應的有效性[1]。

2.2 RISC眾核處理器概述

本文選取一款名為“Godson-T”的RISC架構處理器芯片為研究對象和載體。該款芯片是由中國科學院計算技術研究所系統結構國家重點實驗室設計的一款片上眾核處理器芯片,主要面向電信應用、服務器、金融管理、醫療和大型數據庫系統等領域的高性能計算。該款眾核處理器目前已經順利通過各項驗證和測試,并成功Tape-out。

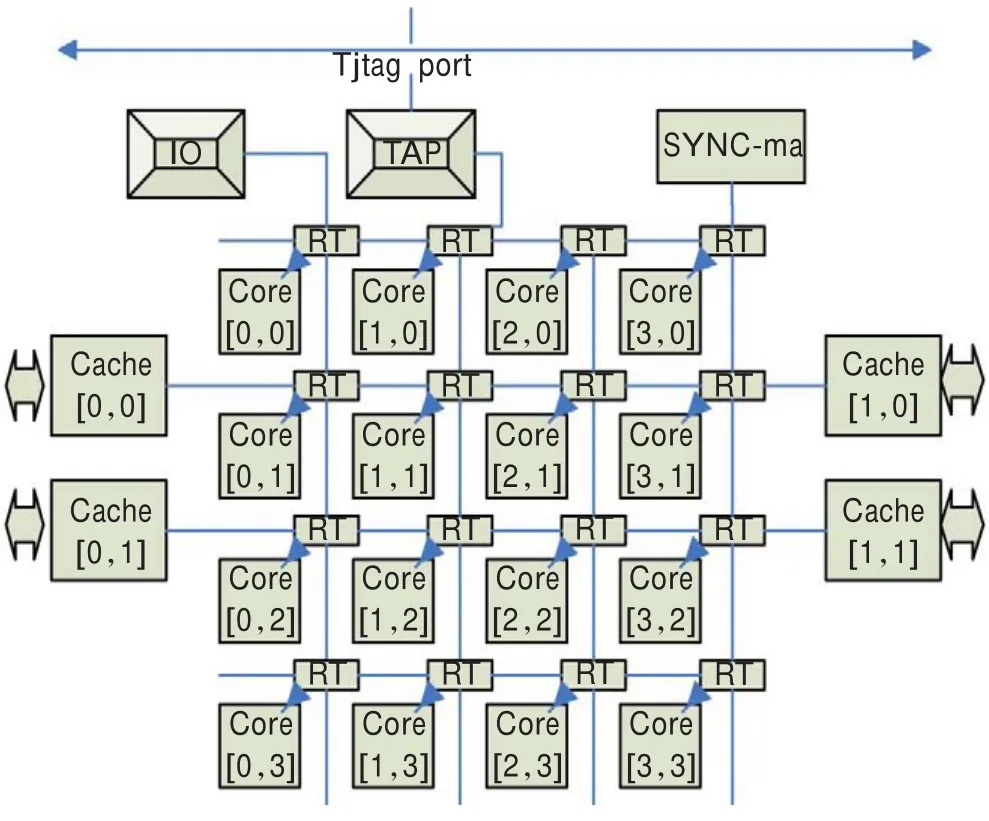

該款眾核處理器的結構如圖1所示,中間部分為四縱四橫的十六單元陣列,每個單元由一個處理器小核和一個RT組成,兩邊各有兩個L2-Cache,為二級數據緩存,為十六個獨立小核共享。在示意圖的上方,SYNC-ma模塊(同步管理器)負責同步管理各獨立小核間的互聯與協調[2-3]。TAP端口負責與JTAG調試相關的接口進行通信的模塊,IO模塊負責向片外發送相關配置信息。

2.3 驗證語言System Verilog概述

SystemVerilog簡稱為SV驗證語言,是IEEE 1364 Verilog-2001標準的擴展增強,兼容Verilog HDL 2001,并已經成為硬件設計下一代驗證仿真的主流編輯語言。SV語言結合了來自Verilog HDL、C語言、面向對象設計語言的部分概念,另外包含了Assertion語言和平臺語言,完美結合了驗證過程中使用頻繁的高層驗證性語言(HVL)和開發過程中使用較多的硬件描述性語言(HDL),對于進行當今高度愈加復雜的設計驗證工作無疑是提供了一種有效的解決思路。它具有接口(interface)、斷言(Assertion)、多線程(multiple threads)和函數和任務(Function and Task)等多種新的驗證平臺建模技術[4-6]。

圖1 Godson-T眾核處理器的結構示意圖

2.4 驗證環境的整體設計

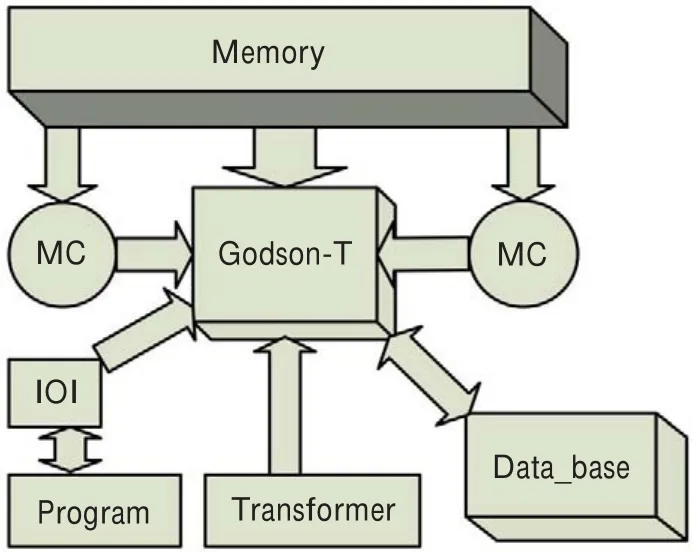

Godson-T整體驗證環境設計主要由六部分組成。包含處理器小核在內的其頂層實現模塊作為待測硬件部分,參考驗證模型模擬器Transformer作為測試軟件部分,這兩部分具體體現軟硬件協同驗證的策略;內存空間Memory由一段C代碼負責維護和執行相關操作,容量為4 GB。輸入輸出接口模塊(IOI)負責進行接口配置;兩個同構的Memory Controller模塊(MC)分置兩側,用來針對和控制訪存操作;一個存放著在驗證過程中可能出現故障信息的數據庫Data_base和若干具有分選功能的選擇器等共同組成驗證環境中的附屬模塊。其結構示意圖如圖2所示。

圖2 Godson-T驗證環境結構示意圖

在Godson-T被動式驗證的指導思想下,驗證環境必須做到主動去適應和滿足測試小核的對每個測試程序的執行操作和處理動作,而讓待測小核能夠在不受平臺外部條件任何干擾和容錯性相關的影響下自主完成自身設計功能體現。

驗證環境中由C代碼負責維護的內存空間只識別可執行文件,故在初始化時,程序列表中等待測試的程序需首先進行編譯,再進行加載。向內存中加載可執行文件是通過調用加載函數實現的,該加載函數的功能是從程序列表中按照一定次序依次讀取測試程序,直到所有測試程序都加載完畢。

編號為core[0,0]作為測試程序的主核,既是需要測試的小核之一,也是測試環境中負責向其余小核客戶傳遞消息的起點。所有測試程序依次輪訓每個小核首先需要將消息發送至core[0,0],待測目標小核收到與之相匹配的調試編號開始進行取指、訪存等操作,這樣目標小核在調試狀態下就進入了運行過程。如果是同時測試多個小核對與多線程程序運行的情況,主核會根據需求創建出多個線程,并通過片上網絡進行資源調用和分配,使各個小核相繼運行自身的線程任務,這樣就實現了眾核處理器測試環境地初步搭建。完成了驗證環境搭建的首要工作[7]。具體的驗證策略細節會在下一章進行詳細的介紹

3 眾核處理器驗證策略及實現

本章主要講述Godson-T眾核處理器的驗證策略和實現。對于該款眾核處理器的驗證工作,采用讓處理器核主動地執行程序驗證平臺被動地調試適應處理器核的“被動式”思想,通過讓小核與模擬器協同一起執行同樣的測試程序的“軟硬件協同驗證”策略,最終達到所有測試程序的每條指令都比對通過的驗證結果。

3.1 普通指令的驗證策略

該款眾核處理器的處理器小核采用順序雙發射方案設計,指令為亂序執行但順序提交,在驗證工程中,大部分執行后直接進行提交的指令都是可以采用普通指令的驗證策略進行對比,即在提交階段將小核運行情況與模擬器所執行的結果進行對比。

當待測小核core[x,y]的兩條提交總線中任意有一條有效時,此時平臺需要通過調用test_xy_step(x[i],y[i])函數讓模擬器對應的小核core[x,y]也執行同樣的一條指令,由于模擬器可以在瞬間執行完該指令,并將執行結果輸出比較或寫入固定專用的寄存器中等待比較。測試平臺通過調用test_xy_read_pc(x[i],y[i])函數來獲得執行指令的PC值,并以此來判斷二者執行的是否為同一指令,PC值相同則執行為同一指令,可以繼續驗證二者執行結果是否一致。FPR、GPR、FCC、FCR為執行結果對比寄存器,對于普通指令的驗證,驗證平臺只需根據不同情況調用以下6個函數[7]就可以調出小核具體的執行結果,再通過上述信息和關聯函數進行對比即可。平臺中對于普通指令比對過程中用到的六個主要函數包括:

通過實驗和具體實現過程發現,這樣的對比策略能夠覆蓋Godson-T眾核處理器指令集中的大部分指令,精度很高,能及時發現在設計初期大部分的設計缺陷,從芯片的整體過程來看節約了開發周期,通用性強,不失為一種良好的眾核處理器普通指令測試比對策略。

3.2 特殊指令的驗證策略

除了上述包括簡單運算指令在內的大部分普通指令,一些比如Load/Store等指令的執行結果在提交階段需要通過片上網絡或由于系統流水的原因不能馬上提交,此時不能再運用普通指令的對比策略進行驗證。針對這一現象和問題,驗證環境中必須增加應對特殊指令的驗證策略,這樣才能最終實現每條指令都對比通過的驗證目標[1]。

實際上,由于處理器小核對于指令是完全意義上的并行執行,而Transformer在運行過程中是以串行來模擬并行,特殊指令流水執行到提交階段并沒有錯,只是執行結果已經被刷掉或已無法同Transformer的執行實現同步進行比較。小核與小核之間的互聯需要消耗一定的時間,使得對于每個小核個體來說的順序提交變成了整體全部小核的亂序提交,原本順序的指令流從整體的角度來看不再是順序的,所以此時如果仍按照普通指令的的比對策略,就會產生比對不通過,但這并不是小核本身產生的邏輯錯誤而造成的,所以對這些特殊指令進行特殊處理,增加特殊比對機制。

通過例子可以直觀地說明特殊比對機制的實現過程,舉例如下:

現在假設對兩個處理器小核core[0,0]和core[0,1]進行一些包含特殊指令的操作。第一步,core[0,1]向本地一級數據緩存寫入一個數據3,此時模擬器也調用相關store函數完成寫入數據3操作,此時平臺檢測到目標地址空間都為3,比對通過;第二步主核core[0,0]向core[0,1]發出一個讀請求,請求將數值3讀走。讀操作為特殊指令操作,讀取的數據從core[0,1]到core[0,0]需要經過片上網絡的延遲才會返回提交。在這一延遲過程中如若主核core[0,0]的該Cache-line又完成了一次沒有延遲的提交過程,比如core[2,0]向其中寫入了數據4,那么此時提交后模擬器對應core[0,0]相應Cache-line中的值就會變為4。此時再比對由core[0,1]的讀請求操作就會由于模擬器中的值已經被刷走而比對不通過。普通指令的對比策略就不再適用。

仔細地分析上述的對比過程不難發現,對于這類特殊指令,并不能在提交階段再進行驗證比對,而應在數據3從core[0,1]中被取走時就啟動平臺進行比對,此時方能比對成功且不影響后續訪存操作的比對。即在core[0,0]從core[0,1]將數值3取走之后立即啟動模擬器執行一條相應的Load指令,比對就會順利通過,這就是針對特殊指令而在普通指令驗證基礎上進一步優化的比對策略。

3.3 覆蓋率導向的驗證策略

伴隨著現代大規模集成的電路制造工藝的快速發展,設計工程是必須直面芯片制造過程中可能產生的物理缺陷,現今的可測試性設計DFT(Design for Test)應運而生,而覆蓋率測試又是其最重要的指標[2,8]。

Synopsys公司的VCS工具能夠通過監控和評估仿真過程中HDL代碼的執行軌跡來分析出該設計的哪些部分還未被測試到,同時也可能會發現測試平臺的不足以及測試向量需要從哪些方面進行改進,從而可以有導向地將驗證重點放在這些方面,有利于達到覆蓋率百分之百的驗證目標,這為芯片能夠最終成功流片打下了堅實的基礎[7,9-11]。

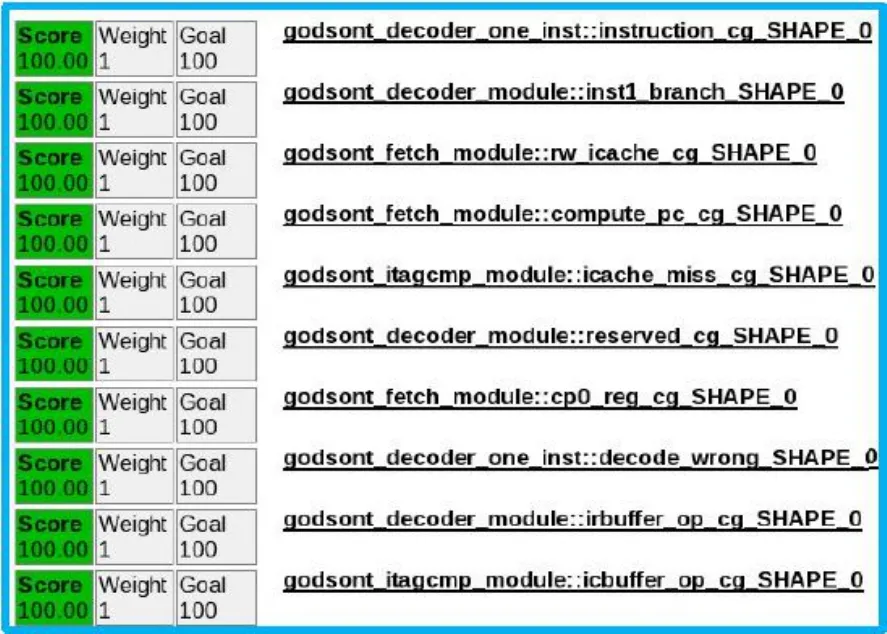

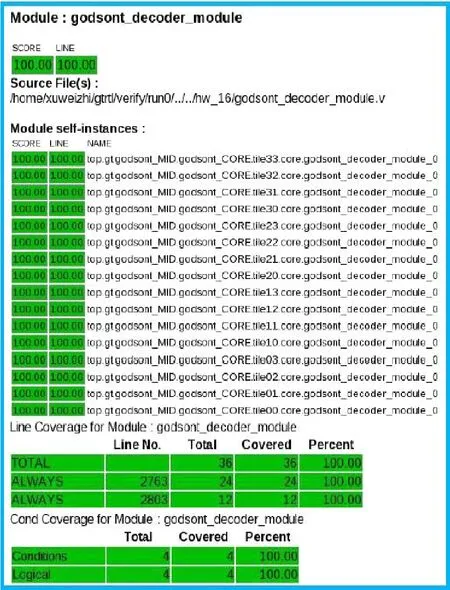

在對該款眾核處理器的設計和驗證過程中,各部分設計人員都需要首先對各自所設計的模塊進行功能點的抽取,然后用System Verilog語言對功能點進行功能覆蓋率建模,開發人員需要在每個硬件模塊中顯示地寫出所有功能覆蓋點,以及需要覆蓋的點和ignore的點。用到的關鍵詞包括:covergroup、coverpoint、ignore bins和cross等[12-13]。圖3是Godson-T眾核處理器前端流水線主要功能模塊覆蓋率報告。圖4是譯碼模塊的功能覆蓋率報告。

圖3 前端流水線主要功能模塊覆蓋率報告

3.4 時序驗證策略

時序分析驗證是除功能驗證之外次重要的驗證重點,其所包含的STA和DTA兩種方式各有所長,可協調彌補,靈活使用[5]。

圖4 譯碼模塊的代碼覆蓋率報告

STA即套用特定的時序模型窮盡覆蓋。通過提取設計電路中的所有顯性和隱性的時序路徑,分別計算每個信號在這些路徑上的延遲,分析其是否違反設計者給定的時序限并找出違背約束的緣由。Synopsys公司的Prime Time工具為STA提供了一個成熟的平臺,該款眾核處理器的靜態時序分析同樣基于這樣一個平臺。具體驗證流程可概括為確定設計數據庫(Specify data libraries)、確定互相聯系(Specify interconnect)、建立時序約束(Specify timing constraint)和時序檢查與分析(Timing check)等[14]。

DTA就是通常的后仿真。在設計的網表信息生成之后,通過相關工具將網表中包含的延遲信息和對應物理參數等提取出來,然后再進行仿真,檢查電路在后期設計中是否滿足設計期望。

DTA相比于STA來說不足之處在于產生的測試向量不夠完整和詳盡覆蓋到每一條路徑,因此DTA無法做到精確顯示一些潛在問題路徑上的時序失真。它相對于靜態時序驗證來說比較精確,但分析速度很慢,同時對多個線程或多個測試程序進行DTA的速度會是其一大瓶頸。

該款處理器的DTA工作主要測試了功能模式、通路模式和JTAG模式下進行的slow、fast以及typical三個庫文件的動態時序分析,都順利通過。同樣測試通過的還有芯片與外圍硬件模塊之間通信消息的模擬驗證[7,13]。

3.5 功耗評估策略

功耗評估是衡量一個處理器性能重要的參考指標,隨著市場對于處理器性能和成本考慮需求的不斷增多,基于低功耗目標而設計開發的處理器受到越來越多用戶的青睞。對于眾核處理器來說,功耗大小優劣直接決定了其性能和未來發展趨勢。因此,在芯片功能和時序的驗證通過之后,努力降低設計的功耗比就是下一階段的測試與繼續驗證的首要目標[12,14]。

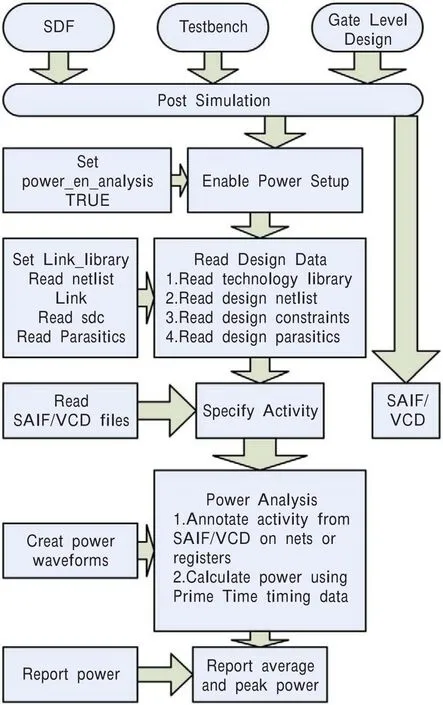

Synopsys公司的Power Compiler和Prime Time都是成熟的可用于系統功耗檢測和優化的驗證工具,在Godson-T處理器功耗評估的初期,同樣可以采用這兩種工具和測試方式作為待測芯片功耗評估的有效手段。Power Compiler能夠報出平均功耗的優勢可以被用來評估每個小核的設計是否具有差異,以及系統整體功耗的橫向對比;而Prime Time工具可以針對待測設計的部分給出更為詳盡的功耗分析,可具體到每一個模塊的某個寄存器,提供更為詳實的改進和優化導向[15]。

Power Compiler多用于初期對于系統功耗的整體把握,可以通過整體評估報告確定需要把設計的功耗降到怎樣一個標準。Prime Time在后期的評估過程中使用較多,利用設計網表、標準庫器件功耗列表、內部行為轉換文件(SAIF)和值轉換文件(VCD)可以細化和對每一個單元或模塊進行功耗比優化。這些網標或文件都可以通過在功耗仿真過程中添加相應的系統文件和庫文件得到[5-6,9]。圖5給出了Prime Time功耗評估的流程示意圖。

圖5 Prime Time的功耗評估流程圖

4 結束語

隨著集成電路制造工藝水平的迅猛提高和計算機體系結構設計技術的發展和創新,微處理器已步入了多核并行的時代。在整個芯片的設計過程中,仿真和驗證是最耗時而又非常重要的一個環節。隨著眾核處理器設計規模的不斷擴大,基于EDA工具的純軟件仿真和基于FPGA的原型驗證都遇到了各自發展道路上的瓶頸。

本文的工作主要是基于EDA工具的驗證,以中國科學院計算技術研究所設計開發的Godson-T眾核處理器芯片為依托,在“被動式驗證”的思想下,采用“軟硬件協同驗證”的策略,最終達到“單條指令對比通過”的驗證目標。再輔以覆蓋率驗證、時序驗證和功耗評估策略,完整地提出了一套芯片驗證平臺搭建和驗證功能實現的方法流程,為最終的流片提供完備的驗證方案。

[1]林明煌.多核處理器原型驗證平臺的研究與實現[D].北京:北方交通大學,2008.

[2]宋風龍.眾核體系結構中高性能片上存儲系統研究[D].北京:中國科學院計算技術研究所,2008.

[3]胡偉武,陳云霽,肖俊華,等.計算機體系結構[M].北京:清華大學出版社,2011.

[4]ASIC.The user guide[EB/OL].[2008-10-14].http://www.asicworld.com.

[5]解詠梅.基于覆蓋率的功能驗證方法[J].計算機應用研究,2005(1).

[6]李海忠.設計文檔[Z].北京:中國科學院計算技術研究所先進微系統組,2010.

[7]林瞬婷.面向多處理器核SOC軟硬件協同驗證平臺[D].杭州:浙江大學,2010.

[8]王立華.基于FPGA的系統芯片(SoC)原型驗證研究與實現[D].濟南:山東大學,2006.

[9]Fine S,Ziv A.Coverage directed test generation for functional verification using Bayesian networks[C]//Proceedings of the 40th Conference on Design Automation,2003.

[10]Synopsys.Coverage technology user guide[EB/OL]. [2011-04-02].http://solvent.synopsys.com.

[11]夏宇聞,陳先勇.Syetem Verilog驗證方法學[M].北京:北京航空航天大學出版社,2011.

[12]Emnett F,Biegel M.Power reduction through RTL clock gating[M].[S.l.]:Automotive Integrated Electronics Corporation,1999.

[13]閆沫.基于System Verilog的驗證平臺建模技術[J].現代電子技術,2009(18).

[14]Synopsys.Prime time guide[EB/OL].[2011-01-10].http://solvent.synopsys.com.

[15]Synopsys.The user guide[EB/OL].[2008-12-21].http://solvent.synopsys.com.

ZHU Boyuan1,LIU Gaohui1,LI Zhengyun2,AN Shuqian2

1.School of Automation&Information Engineering,Xi’an University of Technology,Xi’an 710048,China

2.State Key Laboratory of Computer System Structure,Institute of Computing Technology,Chinese Academy of Sciences, Beijing 100190,China

Multi-core technology has become the inevitable trend of current processor architecture.It is an efficient and sufficient functional verification of the multi-core design that has become one of the hot points in IC design and verification fields,and also one of the key factors to the success final tape-out.Different from the common verification pattern based on emulation,this paper pays more attention in highlighting the overall functional verification environment design driven with the coverage functional verification strategy to verify RISC multi-core processor,and putting forward the idea of“passive authentication”with hardware and software co-verification strategy,ultimately achieves the goal of“single instruction comparison”.Timing verification and power evaluation strategies are also introduced in the later validation stage,providing a complete verification solution for the RISC multi-core processor.

multi-core processor;functional verification;coverage;timing verification;power evaluation

A

TP302.7

10.3778/j.issn.1002-8331.1211-0021

ZHU Boyuan,LIU Gaohui,LI Zhengyun,et al.Functional verification and implementation of RISC multi-core processor.Computer Engineering and Applications,2014,50(21):54-58.

國家自然科學基金(No.61173007);國家自然科學基金青年基金項目(No.61100015)。

朱博元(1986—),男,碩士研究生,主要研究方向:IC前端設計、計算機體系結構;劉高輝(1968—),男,副教授,碩士生導師,主要研究方向:數字移動通信、集成電路設計;李政運(1986—),男,碩士,主要研究方向:CPU小核設計、片上多核系統設計;安述倩(1986—),女,碩士研究生,主要研究方向:計算機體系結構。E-mail:liugh68@xaut.edu.cn

2012-11-01

2013-03-19

1002-8331(2014)21-0054-05

CNKI出版日期:2013-04-10,http://www.cnki.net/kcms/detail/11.2127.TP.20130410.1554.009.html