FT1500處理器中仿真驅(qū)動(dòng)的DDR3封裝設(shè)計(jì)*

黎鐵軍,孫 巖,鄒 京,張秀峰

(國(guó)防科學(xué)技術(shù)大學(xué)計(jì)算機(jī)學(xué)院,湖南 長(zhǎng)沙 410073)

1 引言

隨著集成電路技術(shù)的發(fā)展,多核多線程持續(xù)為通用微處理器帶來更高性能,但訪存帶寬和延遲性能提高緩慢,這導(dǎo)致了存儲(chǔ)墻問題。DDR3作為典型并行總線結(jié)構(gòu)被廣泛應(yīng)用于內(nèi)存總線設(shè)計(jì)中,以提高訪存帶寬和降低訪存延遲,但并行總線的電源完整性和信號(hào)完整性問題突出[1,2],而且隨著傳輸速率的不斷提高,這些問題成為限制傳輸速率進(jìn)一步提高的瓶頸。

FT1500是一款面向高性能計(jì)算的通用微處理器,該處理器采用16核64線程結(jié)構(gòu),設(shè)計(jì)主頻1.5GHz,峰值性能120GFlops,通過四個(gè)72位DDR3存儲(chǔ)控制器訪問片外存儲(chǔ)器,DDR3設(shè)計(jì)速率1 333Mbps。本文重點(diǎn)研究FT1500芯片高速DDR3封裝設(shè)計(jì),解決高頻情況下的電源完整性和信號(hào)完整性問題。

針對(duì)DDR3的封裝設(shè)計(jì)問題,本文提出了仿真驅(qū)動(dòng)的封裝設(shè)計(jì)方法,在設(shè)計(jì)之初通過前仿真制定準(zhǔn)確的設(shè)計(jì)規(guī)則和目標(biāo),在設(shè)計(jì)過程中通過仿真驅(qū)動(dòng)設(shè)計(jì)優(yōu)化,在設(shè)計(jì)完成后用后仿真驗(yàn)證設(shè)計(jì)。實(shí)測(cè)結(jié)果表明,F(xiàn)T1500芯片的DDR3接口可以穩(wěn)定工作在1 400Mbps,達(dá)到了設(shè)計(jì)目標(biāo)。

2 仿真驅(qū)動(dòng)的封裝設(shè)計(jì)

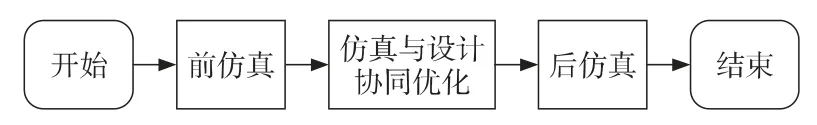

本文提出的仿真驅(qū)動(dòng)的封裝設(shè)計(jì)流程如圖1所示。

仿真驅(qū)動(dòng)的封裝設(shè)計(jì)流程包含三個(gè)主要步驟:

前仿真:確定I/O及關(guān)鍵電源網(wǎng)絡(luò)的目標(biāo)電感與目標(biāo)電阻,確定高速信號(hào)的走線寬度與線間距,驗(yàn)證仿真模型的準(zhǔn)確性。

Figure 1 Full flow of package and PCB simulation圖1 完整的封裝與PCB仿真流程

設(shè)計(jì)與仿真協(xié)調(diào)優(yōu)化:在封裝與PCB設(shè)計(jì)中并行地進(jìn)行PI仿真,提前找出設(shè)計(jì)存在的問題,指導(dǎo)設(shè)計(jì)者進(jìn)行優(yōu)化,PI與封裝設(shè)計(jì)聯(lián)合仿真包含數(shù)次迭代設(shè)計(jì)與仿真,直到達(dá)到設(shè)計(jì)目標(biāo)。

后仿真:在設(shè)計(jì)投出生產(chǎn)前的一次完整的SI/PI仿真,確保設(shè)計(jì)能達(dá)到最終的目標(biāo)。

3 封裝的前仿真

3.1 DDR3信號(hào)目標(biāo)阻抗確認(rèn)

首先通過仿真對(duì)走線阻抗進(jìn)行求解。求解時(shí)要根據(jù)走線的具體情況選擇正確的傳輸線模型,對(duì)于表層走線還需要考慮表層綠油的影響。對(duì)于DDR3數(shù)據(jù)地址等單線阻抗要求為42.5Ω,由仿真求得對(duì)應(yīng)內(nèi)層走線的寬度應(yīng)當(dāng)為30μm,而表層走線寬度應(yīng)當(dāng)為60μm。表層比內(nèi)層缺少一層參考平面,同等線寬下表層單線阻抗過高,為了方便阻抗控制,應(yīng)當(dāng)盡量避免在表層走高速信號(hào)線。

3.2 DDR3I/O仿真模型驗(yàn)證

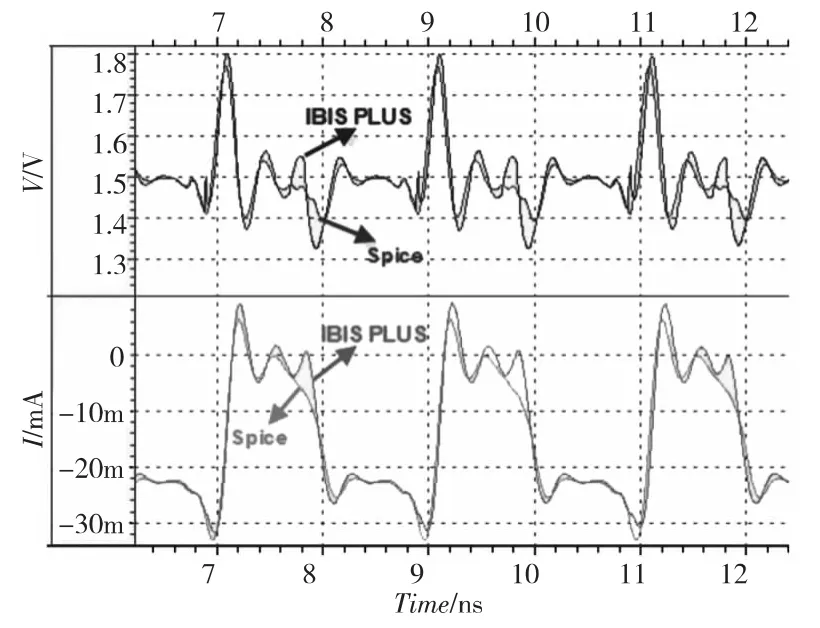

由于SPICE模型的仿真速度慢,需要將DDR I/O的SPICE網(wǎng)表轉(zhuǎn)換成IBIS Plus模型[3]。在使用IBIS Plus模型進(jìn)行仿真之前需要綜合評(píng)估一下該模型的仿真精度。

首先驗(yàn)證IBIS Plus模型電源建模的準(zhǔn)確性,將DDR3I/O的SPICE模型和IBIS Plus模型加入到SPICE測(cè)試網(wǎng)表中,I/O的輸出阻抗設(shè)為40Ω,在I/O的電源上增加一個(gè)RLC子電路作為I/O電源的寄生參數(shù),I/O的輸出接一個(gè)40Ω的電阻。為兩種模型加入相同的激勵(lì),仿真得到兩種模型電源管腳的電壓和電流波形如圖2所示。由圖2可以看出,IBIS Plus模型的電壓電流波形與SPICE模型基本吻合,說明IBIS Plus模型電源建模比較精確。

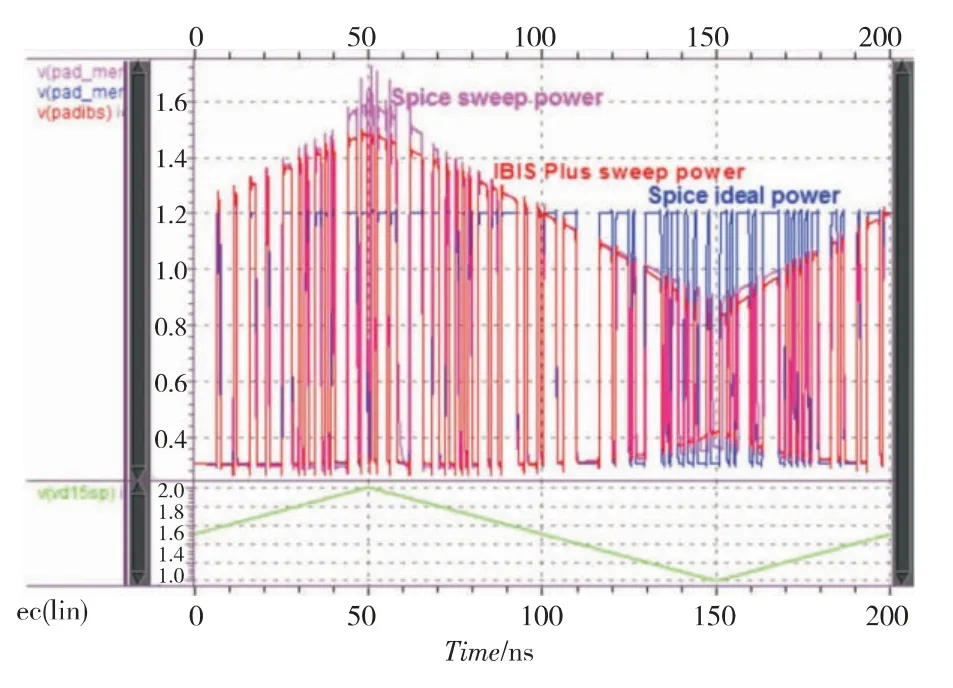

實(shí)際I/O電源電壓可能會(huì)受SSN的影響不停波動(dòng),需要分析兩種模型在不同電源電壓下的輸出情況。同理還是編寫一個(gè)SPICE測(cè)試網(wǎng)表將兩種模型I/O加入,兩種I/O的電源都從1.0V線性變化到2.0V,為了方便對(duì)比,另加入一個(gè)正常供電的SPICE模型的I/O,三個(gè)I/O都加入相同的激勵(lì),仿真結(jié)果如圖3所示。

Figure 2 Simulation results of IBIS plus power modeling圖2 IBIS Plus電源建模仿真結(jié)果

由圖3可以看出,在I/O正常工作電壓1.5V附近,IBIS Plus模型的輸出與SPICE模型輸出幅度相位基本一致。當(dāng)電源電壓高于1.8V或者低于1.2V時(shí),IBIS Plus模型輸出與SPICE模型的輸出誤差較大。假設(shè)DDR3工作在1.5V左右,因此本文仿真均使用IBIS Plus模型。

Figure 3 Simulation results of IBIS plus output圖3 IBIS Plus輸出仿真結(jié)果

3.3 DDR3I/O電源目標(biāo)電感確認(rèn)

由圖3可知,當(dāng)I/O Buffer的電源電壓大于1.8V或者小于1.2V時(shí),I/O Buffer的輸出延時(shí)會(huì)發(fā)生較大的變化,延時(shí)的變化會(huì)對(duì)信號(hào)的時(shí)序造成嚴(yán)重的影響。為了保證I/O Buffer正常工作,必須保證I/O Buffer的電源電壓在正常范圍1.2V~1.8V內(nèi)波動(dòng),本文利用這一條件確定DDR3I/O的目標(biāo)電感[4]。

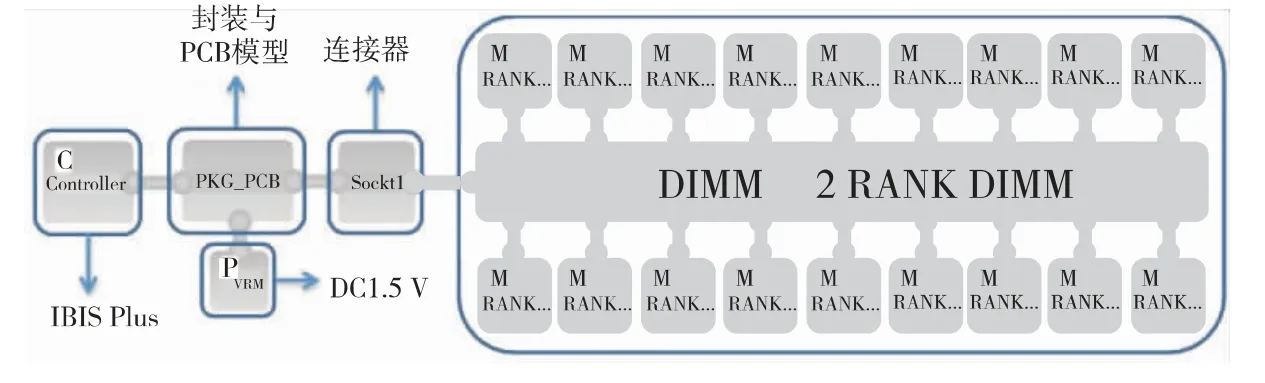

圖4是目標(biāo)電感的仿真拓?fù)洌篊ontroller為兩個(gè)通道的I/O Buffer,PCB為等效的PDN與信號(hào)網(wǎng)絡(luò),PDN網(wǎng)絡(luò)采用一個(gè)集總電感LPDN代替,Memory為內(nèi)存顆粒的I/O模型,VRM提供1.5 V的理想直流電源。

Figure 4 Simulation topology of target inductance圖4 目標(biāo)電感仿真拓?fù)?/p>

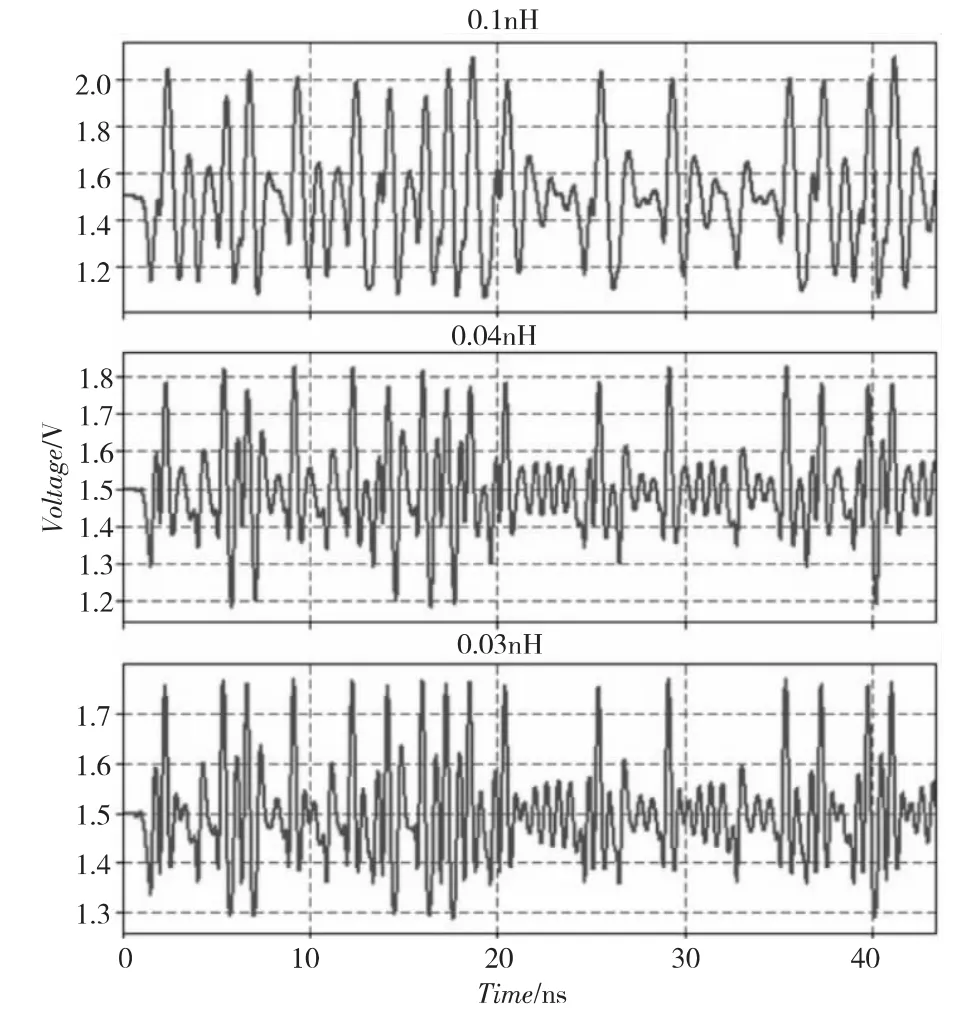

所有的I/O Buffer采用相同的激勵(lì)同時(shí)翻轉(zhuǎn),改變LPDN的大小,仿真得到I/O Buffer電源的紋波如圖5所示。從圖5中可以看出,LPDN的值越大,SSN造成的電源紋波也越大。當(dāng)I/O Buffer的電源在1.2V~1.8V內(nèi)波動(dòng)時(shí),對(duì)應(yīng)的LPDN值即可作為DDR3I/O電源的目標(biāo)電感的最大值。

Figure 5 Simulation results of target inductance圖5 目標(biāo)電感仿真結(jié)果

3.4 DDR3I/O電源目標(biāo)阻抗確認(rèn)

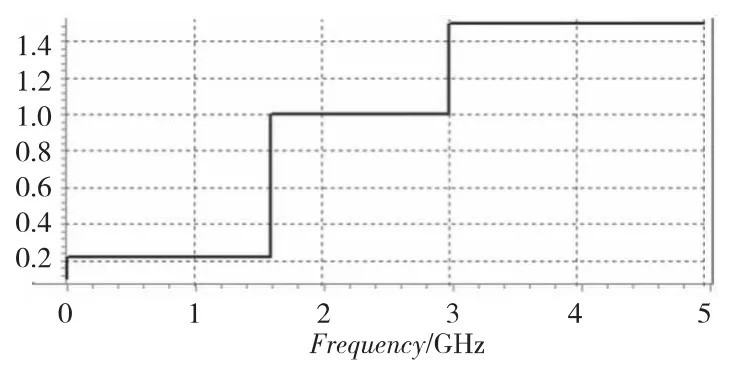

DDR3I/O Buffer的工作電流在直流至很高頻率上都有分布,電流在各個(gè)頻段上也不是均勻分布的,在確定I/O電源的目標(biāo)阻抗時(shí)需要根據(jù)各個(gè)頻段電流的大小計(jì)算不同頻段的目標(biāo)阻抗[5]。

本文通過仿真得到的電流波形進(jìn)行傅里葉變換,得到電流的頻譜圖。該頻譜圖按峰值的一致性劃分為三個(gè)頻段:0Hz~1.6GHz,1.6GHz~3GHz和3GHz~5GHz。根據(jù)目標(biāo)阻抗的計(jì)算公式得出的目標(biāo)阻抗如圖6所示。

4 設(shè)計(jì)與仿真協(xié)同優(yōu)化

4.1 電源直流仿真

封裝基板電源的直流仿真內(nèi)容包括:

Figure 6 Target impedance of DDR3I/O power圖6 DDR3I/O電源目標(biāo)阻抗

(1)電流密度:確保電源地平面的面積和布局合理,電流密度不會(huì)太大而燒毀基板;

(2)過孔電流:確保電源地平面的過孔數(shù)量足夠,過孔電流不會(huì)太大;

(3)直流壓降:評(píng)估PDN的壓降是否滿足要求。

直流仿真與封裝設(shè)計(jì)是一個(gè)不斷迭代優(yōu)化的過程,首先封裝設(shè)計(jì)需要完成一個(gè)初步的包含電源地平面過孔的版本進(jìn)行直流仿真,如果直流仿真達(dá)到要求則進(jìn)行下一步的工作,反之則更改設(shè)計(jì)再次進(jìn)行仿真,直到達(dá)到要求。

4.2 電源電感仿真

SSN與PDN電感成正比,為了減小電源噪聲,必須減小PDN網(wǎng)絡(luò)的寄生電感,將電源地的電感仿真與封裝設(shè)計(jì)聯(lián)合進(jìn)行仿真優(yōu)化。

在封裝基板電源電感仿真中的主要仿真內(nèi)容包括:芯片引腳的自電感、芯片引腳的總電感和PDN的總電感。

(1)芯片引腳的自電感:是忽略其它芯片引腳的影響、仿真單獨(dú)一個(gè)芯片引腳的電感,自電感可以用于評(píng)估單個(gè)芯片引腳的連接是否合理;

(2)芯片引腳的總電感:包含芯片引腳的自電感及與其它芯片引腳之間的互感;

(3)PDN總電感:是所有PDN芯片引腳上總電感的集總值。

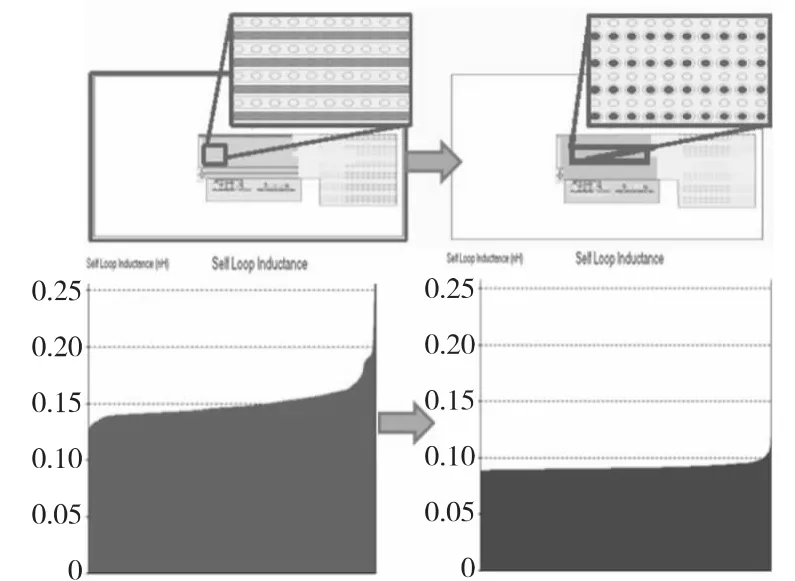

如圖7所示是一次電源電感仿真與封裝設(shè)計(jì)聯(lián)合優(yōu)化過程。設(shè)計(jì)的初始版本,芯片引腳間距過小,所有的芯片引腳只能采用走線連接起來,經(jīng)過仿真縫隙發(fā)現(xiàn)芯片引腳的自回路電感較大。根據(jù)仿真結(jié)果建議增大芯片引腳間距,將所有的地芯片引腳采用平面接連,再次仿真發(fā)現(xiàn)芯片引腳的自回路電感有了明顯的減小。

5 封裝的后仿真

5.1 電容優(yōu)化

Figure 7 Inductance simulation of package substrate圖7 封裝基板電感仿真

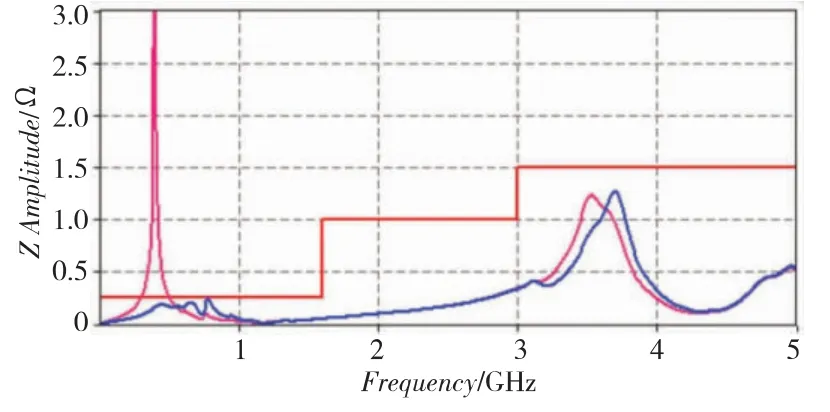

電容優(yōu)化的目的就是選擇合適的去耦電容,盡量減小PDN的阻抗。傳統(tǒng)的電容優(yōu)化方法一般有兩種:一種利用EDA工具自動(dòng)進(jìn)行電容優(yōu)化[6],這種方法簡(jiǎn)單易操作,但是不夠靈活,不能針對(duì)諧振點(diǎn)進(jìn)行優(yōu)先優(yōu)化;另一種方法是在參數(shù)提取工具中為每個(gè)電容賦上模型,然后提取電源的阻抗,這種方法靈活但是操作復(fù)雜,優(yōu)化一次需要幾個(gè)小時(shí),非常耗費(fèi)時(shí)間。

本文提出了一種全新的電容優(yōu)化方法:首先提取PDN網(wǎng)絡(luò)的S參數(shù),提取時(shí)在芯片引腳和電容管腳上都加上端口,電容開路;然后將提取的PDN的S參數(shù)賦給封裝與PCB,再將電容連接到相應(yīng)的電容端口上,為電容選擇合適的模型;最后從芯片端提取PDN的阻抗。

這種方法優(yōu)化一次僅需要幾秒鐘時(shí)間,而且相當(dāng)靈活,最終優(yōu)化的結(jié)果如圖8所示。從圖8可以看出,優(yōu)化之后DDR I/O的PDN阻抗諧振點(diǎn)有了明顯的降低,并且到了目標(biāo)阻抗之下。

Figure 8 Capacitance optimization results圖8 電容優(yōu)化結(jié)果

Figure 9 Simulation topology of DDR3圖9 DDR3仿真拓?fù)?/p>

5.2 時(shí)序仿真

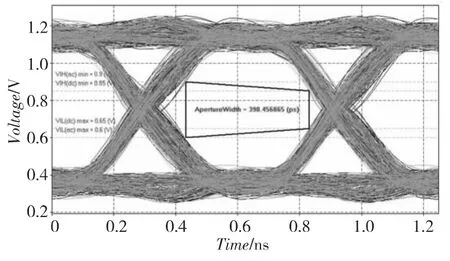

DDR3信號(hào)的仿真拓?fù)淙鐖D9所示。

仿真時(shí)采用一個(gè)DDR3通道帶一根雙Rank內(nèi)存條的結(jié)構(gòu),仿真速率為1 600Mbps,最終的仿真眼圖結(jié)果如圖10所示。由圖10可以看出,DDR3的信號(hào)質(zhì)量較好,經(jīng)過計(jì)算各方面時(shí)序滿足要求。

Figure 10 Eyediagram of DDR3signal simulation圖10 DDR3信號(hào)仿真眼圖

6 實(shí)驗(yàn)驗(yàn)證

FT1500封裝設(shè)計(jì)采用的塑封材料為GX-13,封裝厚度為1.35mm,使用10層基板,4-2-4的疊層結(jié)構(gòu)。該芯片內(nèi)核頻率1.8GHz,DDR3數(shù)據(jù)傳輸率1 400Mbps,運(yùn)行Stream測(cè)試程序,能夠穩(wěn)定運(yùn)行24小時(shí)。

Figure 11 FT1500package implementation圖11 FT1500封裝實(shí)現(xiàn)

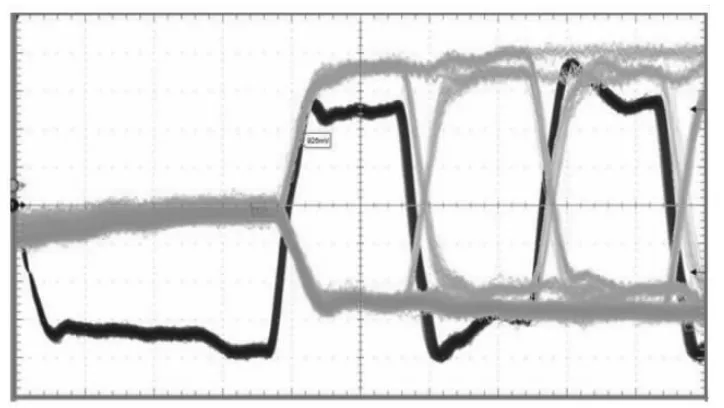

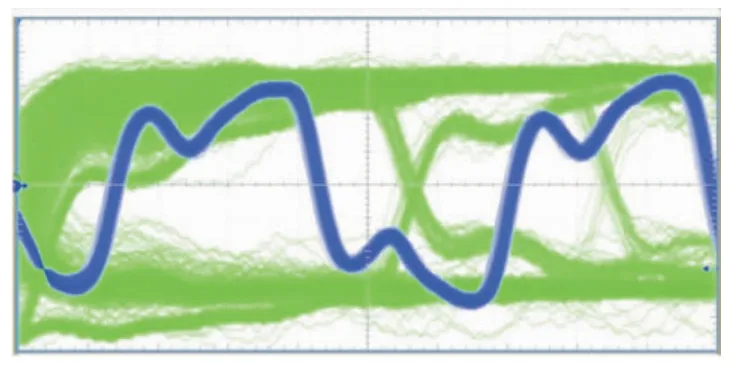

我們采用Tektronix公司的DSA72004示波器對(duì)FT1500芯片DDR3的數(shù)據(jù)信號(hào)以及命令控制信號(hào)進(jìn)行幅值信號(hào)完整性的測(cè)試。該示波器四個(gè)通道高達(dá)20GHz的模擬帶寬,示波器內(nèi)采樣信號(hào)的上升時(shí)間達(dá)到9ps,能夠滿足DDR3信號(hào)采樣頻率要求。

圖12和圖13分別給出了FT1500芯片1 400Mbps DDR3信號(hào)的寫信號(hào)眼圖和讀信號(hào)測(cè)試眼圖:寫測(cè)試點(diǎn)選取PCB中CPU的底層信號(hào)線過孔處;讀測(cè)試點(diǎn)選取內(nèi)存條的SDRAM端信號(hào)線過孔處。測(cè)試信號(hào)選擇同組內(nèi)的DQS信號(hào)和DQ信號(hào),其中DQS采用差分探頭,DQ采用單端探頭。從測(cè)試眼圖可以看出,DQS信號(hào)和DQ信號(hào)的時(shí)序關(guān)系滿足DDR3規(guī)范[7]的要求。

Figure 12 Eyediagram of DDR3write operation test圖12 DDR3寫操作測(cè)試眼圖

Figure 13 Eye-diagram of DDR3read operation test圖13 DDR3讀操作測(cè)試眼圖

7 結(jié)束語

本文面向核高基重大專項(xiàng)高性能微處理器FT1500的DDR3封裝設(shè)計(jì),提出了仿真驅(qū)動(dòng)的封裝設(shè)計(jì)方法,通過仿真方法建立設(shè)計(jì)規(guī)范、指導(dǎo)設(shè)計(jì)優(yōu)化、驗(yàn)證設(shè)計(jì)結(jié)果,完成了四通道72bits DDR3接口的封裝設(shè)計(jì)。對(duì)FT1500芯片的實(shí)測(cè)表明,DDR3接口可以穩(wěn)定工作在1 400Mbps,信號(hào)的電源性和信號(hào)完整性滿足DDR3規(guī)范要求。

[1] Eric B.Signal and power integrity—simplified[M].2nd Edition.NJ:Prentice Hall,2009.

[2] Burns D,Westerhoff T,Boyd J.Counting the piconseconds:Integrating timing,signal and power integrity analysis[C]∥Proc of DesignCon’08,2008:1.

[3] Choi M J,Pandit V.SI/PI co-analysis and linearity indicator[C]∥Proc of IBIS Summit Meeting,2010:1.

[4] Memory made easy DDR2/3analysis[Z].Pennsylvania: Ansoft Corporation,2010.

[5] Swaminuthan M,Engin A E.Power integrity modeling and design for semiconductors and systems[M].Li Yu-shan,Zhang Mu-shui,translation.Beijing:Publishing House of Electronics Industry,2009.(in Chinese)

[6] Herrick C.Acurate and efficient SSN modeling[Z].Pennsylvania:Ansoft Corporation,2008.

[7] JEDEC Standards.DDR3SDRAM specification:USA,JESD79-3E[P].2010-07-01.

附中文參考文獻(xiàn):

[5] Swaminuthan M,Engin A E.芯片及系統(tǒng)的電源完整性建模與設(shè)計(jì)[M].李玉山,張木水,等譯.北京:電子工業(yè)出版社,2009.