DSP圖像處理系統與PC機高速通信電路設計

王 勇,孫向文,楊 雷

(河南科技大學a.電氣工程學院;b.信息工程學院,河南洛陽471023)

某圖像信息處理板(簡稱圖像板),主要用于圖像數據的轉換與輸出,并根據圖像格式提取目標的個數、大小、坐標、邊界、運行軌跡等信息,進而將這些信息上傳給PC機進行記錄和分析。圖像板以DSP為核心進行設計,每隔1 ms處理一次信息并生成大小為200個字(16 bit)的一組數據。要將上述處理結果上傳給PC機,并考慮數據間隙,通信比特率必須大于3.2 Mbit/s。

PC機常用的高速通信接口有網口和USB口,采用這兩種方式與DSP通信時,硬件上需要額外的接口電路,軟件上需要編寫接口電路的固件程序、驅動程序,上位PC機識別端口時需要調用相應的Windows API函數,對開發人員技術能力要求較高,開發周期相對較長[1]。而高性能的雙口RAM無論是在并行處理網絡中的數據共享,還是在流水線方式的高速數據傳輸方面,均能發揮重要作用。以雙口RAM為核心設計接口電路,并與高速數據采集卡配合,構成高速數據傳輸介質,可以實現DSP圖像處理系統與上位PC機之間的高速通信,且方法通用易行,可靠性高[2-3]。

1 系統組成及工作原理

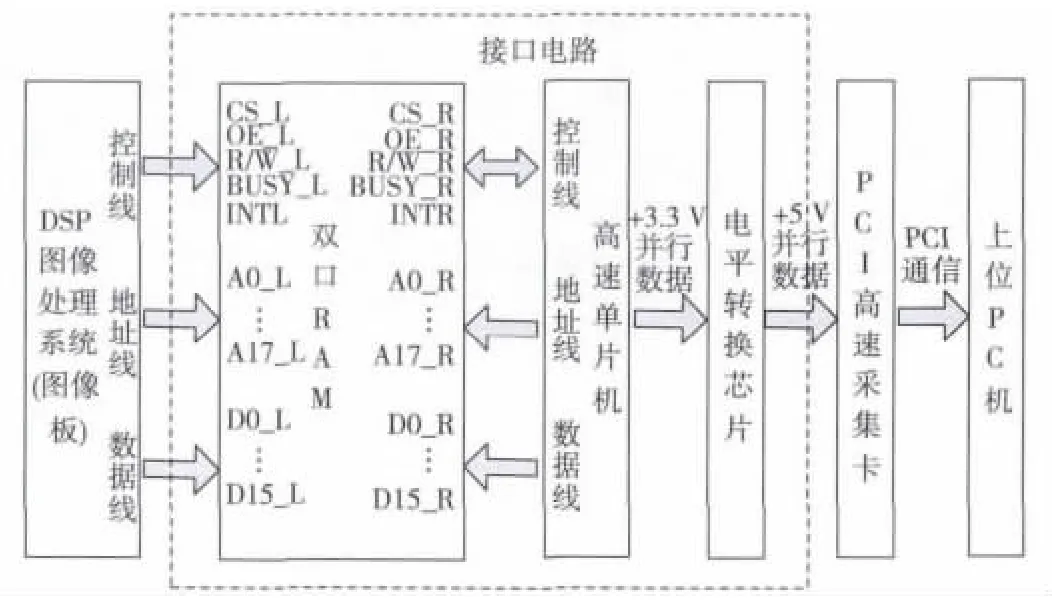

基于雙口RAM的DSP與上位PC機高速通信系統由4部分夠成:DSP系統、接口電路、高速PCI數據采集卡以及上位PC機,具體結構如圖1所示。接口電路以雙口RAM、高速單片機為核心進行設計,用于識別和控制通信起始、數據暫存和電平轉換;高速數據采集卡選用通用型PCI高速數字量卡,用于將接收到的并行數據轉換成通用PCI通信方式,便于上位PC機軟件接收。其中,為縮短線長,保證通信可靠性,可以將DSP系統與接口電路放在同一塊電路板上。

圖1 系統組成框圖

2 基于雙口RAM的接口電路設計

接口電路的功能主要有以下3點:1)由于DSP為+3.3 V供電,所選數據采集卡額定的數字高電平為+5 V,因此接口電路需要實現+3.3 V到+5 V的電平轉換。2)圖像板每次處理完數據后以中斷方式通知上位機開始上傳數據,因此接口電路需要準確識別圖像板發出的中斷信號,以便控制通信的起始。3)上位PC機軟件運行于操作系統之上,其語句延時精度不高,通過編程讓上位PC機軟件直接控制地址線、數據線端口讀取DSP存儲單元的方式,效率低,涉及方法復雜。而接口電路可以將圖像板上傳的數據進行整體暫存,然后上位PC機通過操控PCI數據采集卡,以固定的方式高效讀取數據。

2.1 接口電路硬件設計

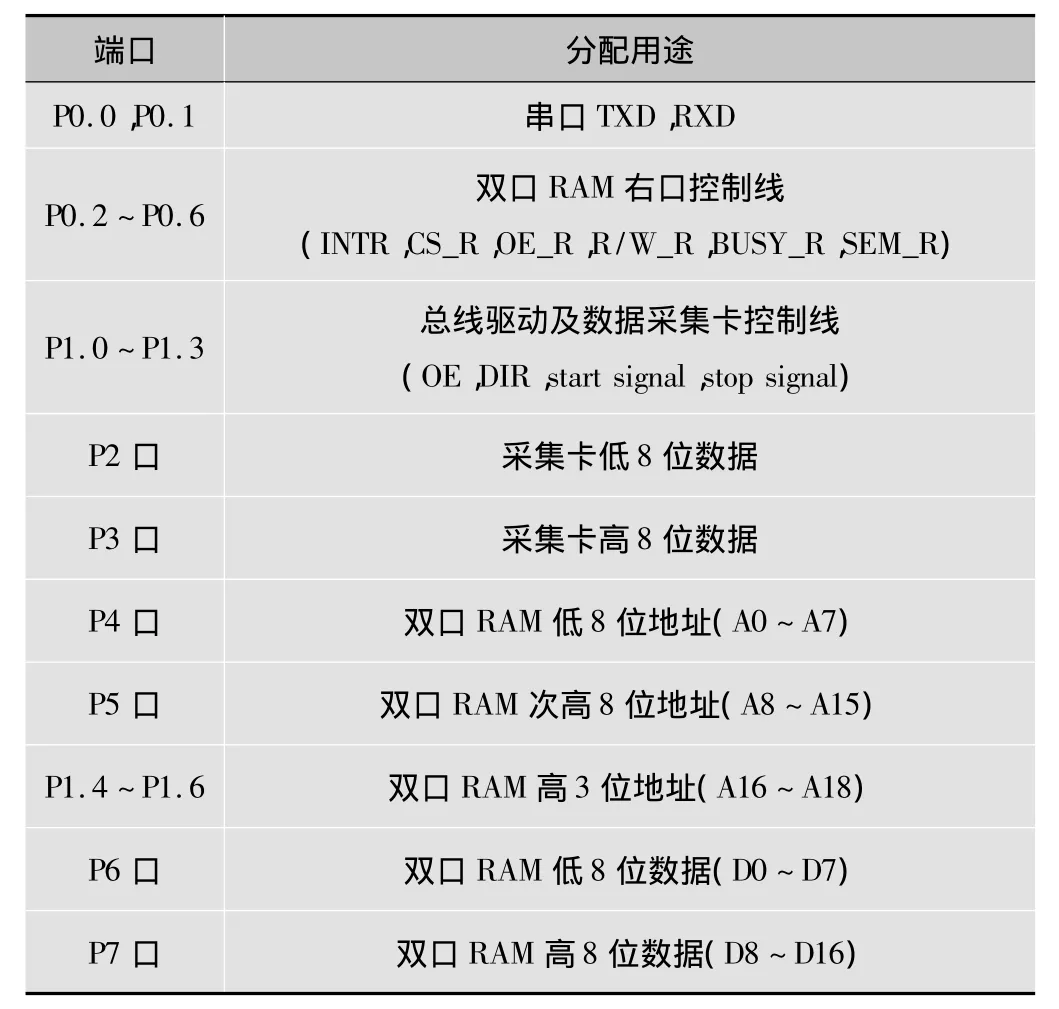

接口電路的硬件構成如圖1所示。雙口RAM用于實現DSP與后續高速單片機的數據共享,設計中選用IDT公司的IDT70T633芯片,其左口與DSP連接,右口與單片機連接。高速單片機用于控制雙口RAM識別通信起始、讀取數據,并以并行方式轉發給后續的PCI數據采集卡,設計中選用Silicon Laboratories公司的C8051F120,該單片機執行速度最高可達100 MInstruction/s(兆指令/秒),有64個通用I/O口,能夠很好滿足設計需要,其端口分配如表1所示。電平轉換芯片用于將+3.3 V的DSP數據轉換成+5 V的標準TTL電平,設計中選用16位總線驅動器SN74ALVC164245。

表1 設計中C8051F120單片機的端口分配

2.2 雙口RAM工作方式

接口電路設計的核心在于對雙口RAM芯片IDT70T633的有效控制。雙口RAM除了數據存儲功能外,還提供2套完全獨立的端口,每套端口分別有自己的控制線、地址線和數據線,允許雙端口同時讀寫數據。IDT70T633是一款高速512 k×18位的雙口RAM,存儲空間同樣為左、右兩套端口所共用,帶片內總線仲裁電路,適用于兩控制器之間大量數據的快速雙向傳遞。當IDT70T633的兩套端口同時對同一存儲單元進行讀寫時,會導致數據破壞或丟失。為了防止這種情況發生,IDT70T633有2種仲裁方式。1)使用BUSY控制線:當左右端口對同一存儲單元操作時,先發出請求信號的一端對應的BUSY線為高,允許讀寫,另一端口的BUSY線為低,處于等待狀態,禁止讀寫。插入等待狀態會降低數據傳輸速率,對于高速通信通常是不可接受的。2)中斷方式:IDT70T633左右兩端各有一條中斷信號線,7FFFEH和7FFFFH存儲單元為中斷響應單元。當左方對7FFFFH存儲單元寫入數據時,右方產生中斷信號(INTR置低);右方從7FFFFH存儲單元讀取數據時,右方的中斷信號被撤除(INTR置高)。當右方對7FFFEH存儲單元寫入數據時,左方產生中斷信號(INTL置低);左方從7FFFEH存儲單元讀取數據時,左方的中斷信號被撤除(INTL置高)。可見,可以通過中斷響應單元的讀寫操作來實現雙口RAM兩側電路單元的實時高速通信[4-5]。

2.3 接口電路軟件設計

設計中,采用雙口RAM的中斷仲裁方式,不僅能有效避免左端DSP與右端單片機對同一RAM地址的爭用問題,而且可以實現二者之間的高速通信[6]。具體通信過程如下:DSP處理完圖像信息后,將生成的數據從左口存入雙口RAM,并將最后一個字節數據存入7FFFFH存儲單元,從而在雙口RAM的右口產生中斷信號,通知單片機已寫入數據;高速單片機檢測到中斷信號后,啟動中斷程序,從約定地址讀取數據,經電平變換后上傳給上位PC機,讀取到7FFFFH存儲單元后,清除右側中斷信號,此次通信結束。因為數據的寫入與讀出均采用并行方式,通信速度完全由DSP和高速單片機的指令執行速度決定,具體軟件流程如圖2所示。

3 高速PCI數據采集卡的應用

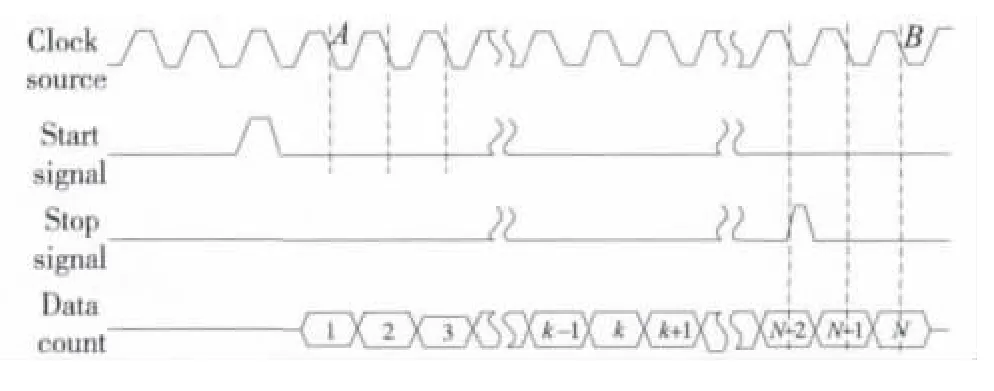

高速PCI數據采集卡選用國產阿爾泰PCI2510高速數字量輸入輸出卡。PCI總線是一種連接電子計算機主板和外部設備的總線標準,帶寬為132~264 Mbit/s,具有兼容性好、自動配置、擴展性好、中斷共享等特點。阿爾泰PCI2510卡可直接插在IBM-PC/AT或與之兼容的計算機內的任一PCI插槽中,具有32個與TTL兼容的高速通道和16 byte的板載FIFO存儲器,DMA傳輸模式,最大傳輸速率可達120 Mbit/s。該卡可通過普通模式或握手模式接收外部數據輸入,設計中選用普通模式。在該模式下,PCI2510能隨啟動信號(start signal)開始從外部設備傳輸數據到板卡,也能隨停止信號(stop signal)停止數據的輸入。當啟動信號到來時,PCI2510將在下一時鐘周期(見圖3中A點處)開始接收外部數據,當停止信號到來時,PCI2510將在下一時鐘周期(見圖3中B點處)停止接收外部數據,控制時序如圖3所示。上位PC機操作軟件界面采用NI公司的Labwindows/CVI開發平臺進行設計,具體程序代碼這里不再贅述。

圖2 接口電路程序流程

圖3 PCI2510卡控制時序(截圖)

4 結論

基于雙口RAM,配合單片機、電平轉換驅動器以及PCI數據采集卡,設計的DSP圖像處理系統與上位PC機高速通信電路,已經在某光電信息處理平臺和相應的測試設備中得到應用,完全能夠達到每1 ms傳輸200個字的通信速度要求,并且運行穩定。這種設計方案具有通用性,可以為單片機、ARM或FPGA等嵌入式系統與上位PC機之間的高速數據傳輸提供借鑒。

[1]冷佳鵬,劉文怡.基于USB總線的多通道數據采集系統設計[J].電子技術應用,2012,38(12):11-16.

[2] LIBo,LIUQingjian,QIAO Zhifeng,et al.An interface design of communication between PC104 and DSP based on dual-port RAM[J].Applied Mechanics and Materials,2012,141(1):198-202.

[3]章筱靜,陳明,瞿赟.雙口RAM在航空發動機參數采集系統中的應用[J].計算機測量與控制,2007,15(9):1250-1252.

[4] DAVE B .Dual-port RAM delivers18 Mbits And 72-bitwide ports[J].Electronic Design,2003,51(19):34.

[5] ZHOU Rigui,HU Jingchun,YE Shuisheng,etal.Application of fixedpoint DSPand 16-bit parallel output A/D and dual-port RAM[J].International Symposium on Test and Measurement,2003(1):573-576.

[6] CHEN Zhanlun,OUYANG Sen,SHIYili.Design of a power qualitymonitoring device based on dual-CPU[C]//Proc.2012 International Conference on Control Engineering and Communication Technology,2012.[S.l.]:IEEE Press,2012:192-196.