軟件無線電實現調制解調器的設計

牛耀利 張太福

(中國人民武裝警察部隊新疆總隊烏魯木齊市支隊,新疆 烏魯木齊830003)

0 引言

軟件無線電是模塊化、標準化的硬件單元,以總線方式連接構成基本平臺,并通過軟件加載實現各種無線通信功能的一種開放式體系結構。其中心思想是構造一個具有開放性、標準化、模塊化的通用硬件平臺,將各種功能,如工作頻段、調制解調類型、數據格式、加密模式、通信協議等,用可升級、可重新配置的軟件來完成,并使寬帶A/D和D/A轉換器盡可能的靠近天線,以研制出具有高度靈活性、開放性的新一代無線通信系統[1]。

1 軟件無線電的基本結構

軟件無線電強調體系結構的開放性和全面可編程性,通過軟件的更新改變硬件的配置結構,實現新的功能。

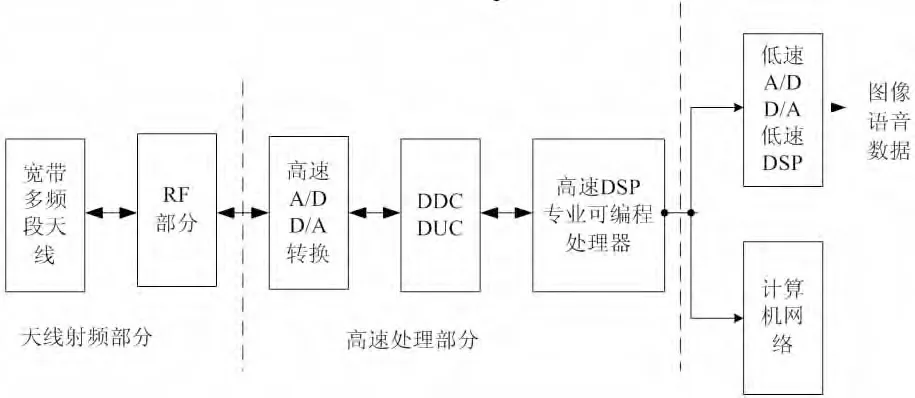

圖1 理想的軟件無線電系統結構

理想的軟件無線電結構如圖1所示。軟件無線電主要由天線、射頻前端、高速A/D/A轉換器、通用和專用數字信號處理器、低速A/D/A轉換器以及各種接口和軟件所組成。在發射時RF部分主要完成濾波、功率放大等任務,接收時實現濾波、放大等功能。理想的軟件無線電因實現射頻直接帶通采樣,要求A/D轉換器有足夠的工作帶寬,較高的采樣速率,而且要有較高的A/D轉換位數,以提高動態范圍。模擬信號進行數字化后的處理任務全由DSP和專用的可編程處理器的軟件來承擔。為了減輕通用DSP的處理壓力,通常把A/D轉換器傳來的數字信號,經過專用數字信號處理器件 (如數字下變頻器DDC)處理,降低數據流速率,并把信號變至基帶后,再把數據送給通用DSP進行處理。通用DSP主要完成各種數據率相對較低的基帶信號的處理,比如信號的調制解調,各種抗干擾、抗衰落、自適應均衡算法的實現等。還要完成經信源編碼后的前向糾錯(FEC),幀調整、比特填充和鏈路加密等算法。也有采用多DSP芯片并行處理的方法,以提高其處理的能力。

2 調制解調系統關鍵模塊的FPGA的實現

QPSK調制及解調部分由幾個關鍵模塊組成,其中包括,加法器、乘法器、載波發生器、FIR濾波器、PN序列模塊和通信中載波同步、位同步、幀同步等部分,下面就其重點部分的具體實現方法做以闡述。

2.1 加法器模塊

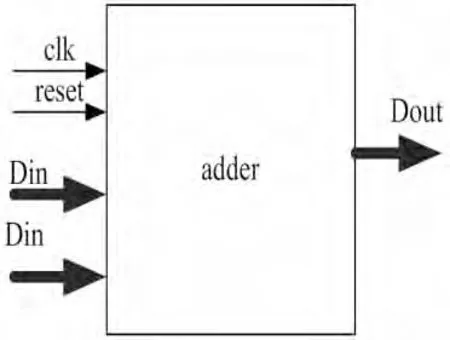

加法模塊是QPSK系統中比較重要的組成部分,目前有很多種加法器的設計。圖2所示的加法器為本系統所采用的方法,模塊和端口定義如下:

Clk——輸入信號,工作時鐘;

Rest——輸入信號,系統復位;

Din1——輸入信號,被加數輸入;

Din2——輸入信號,加數輸入;

Dout——輸出信號,相加結果輸出。

圖2 加法器模塊

這里采用的加法器屬于同步加法器,有時鐘的上升沿來臨時接數據對其做相加處理。加法器模塊的兩個輸入分別是同相支路和正交支路中信號與載波相乘后的結果,因而是有符號數,采用補碼表示。在定點運算中,補碼的最高位為符號,正數為0,負數為1,而其它的為它絕對值。這樣,正數的補碼和它的源碼相同,負數的補碼為將它的源碼逐位求反,然后在最低位上加1。這樣,計算兩數相減(即一個正數加一個負數)的運算可以通過用它們的補碼相加來完成,簡化了運算電路[2]。

2.2 乘法器的實現

在軟件無線收發信機中,乘法器的作用主要是用于混頻,在發信機中,離散的基帶I,Q采樣值與NCO輸出的離散正交載波相乘,完成上變頻過程,在收信機中,經過帶通采樣的離散接收信號與NCO輸出的離散正交載波相乘,經過低通濾,得到離散的數字I,Q信號,完成下變頻過程。乘法器起到兩個信號相乘的作用。

乘法器一般采用并行工作方式,本設計中發信機的離散基帶I,Q采樣值為8比特有符號數,NCO數字本振的輸出也為8比特有符號數,所設計的乘法器的兩個輸入應該為8比特有符號數,乘積為16比特。所以采用一種由8位加法器構成的以時序邏輯方式設計的8位乘法器。其乘法原理是:乘法通過逐項移位相加原理來實現。從被乘數的最低位開始,若為1,則乘數左移后與上一次的和相加;若為0,左移后以全0相加,直至被乘數的最高位。

2.3 NCO的FPGA實現

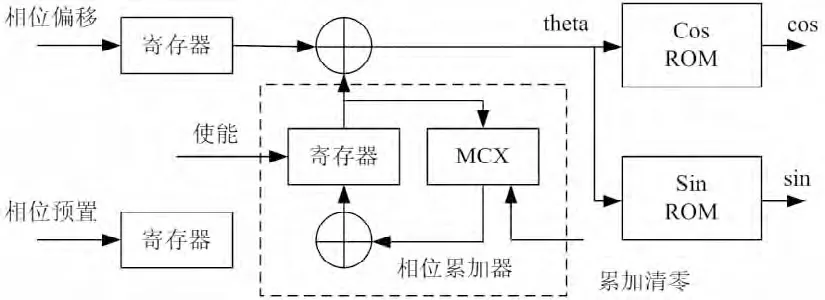

載波發生器基于數控振蕩器(NCO)產生,數控振蕩器結構如圖3所示。主要由相位累大器和SIN/COS表構成。相位累加產生的相位作為地址去查找ROM表,查到的SIN/COS值即本地載波的數字頻率送至乘法器,完成混頻。

圖3 數控振蕩器結構圖

實際的NCO由樣位累加器、波形ROM查找表組成,這樣的結構很容易用FPGA實現,兩個正弦波產生查找表,用Xilinx提供的IP核。本設計中采用了30位的相位累加器,進行相位截斷后,用相位累加大路的高10位尋址波形ROM,需要注意的是為了使設計的NCO能用于上變頻和下變頻操作,波形ROM中所存的內容必須同時提供兩路完全正交的正弦波和余弦波。由于是10位尋址ROM,并且指定ROM的字長為8比特有符號數,所以每一塊的ROM容量應為210=1K*8,故總共需2K*8的存儲量,這在FPGA實現時將耗費大量的內部CLB資源,所以應該重新考慮ROM查找表的設計,盡可能節省存儲器資源。對于正弦波和余弦波來說可以得用對稱性只存儲二分之一周期,甚至四分之一周期,對于前者需要附加一個符號求補器,后者則另需一個相位求補器和符號求補器[4]。

2.4 濾波器的實現

本設計中濾波器為低通濾波器,截止頻率是該通道的碼元速率,即2.5kHz。濾波器的采樣時鐘用此時的系統時鐘頻率(160kHz)。Xilinx的綜合軟件Core Generation給出了這種濾波器的實現。如圖四所示:

圖4 FIR模塊圖

模塊端口定義如下:

CLK——輸入信號,濾波器工作時鐘160kHz;

DIN[N-1.0]——輸入信號,濾波器的數據輸入,N為位寬,即接收機中乘法器的輸出位寬為N=24;

ND——輸入信號,高有效,為高時表示一個新的數據輸入;

RDY——輸出信號,高有效,為高時表示濾波器己處理完當前數據,可以接收新的數據輸入;

RFD——輸出信號,高有效,為高時表示濾波器輸出端口上有一個新的結果數據輸出;

DOUT——[M-1,0]-輸出信號,濾波器的數據輸出,M為輸出位寬,與發射機的基帶碼流相對應,這里取M=8。

3 小結

數字調制解調在FPGA中的實現證明了用FPGA作為軟件無線電數字信號處理器件的可行性。使用FPGA的可重構性,可以在系統中實現各種通信模式的算法,充分體現了軟件無線電的靈活性。同時,實現了嵌入FPGA的CPU核對芯片的信號處理功能控制。通過嵌入式CPU,可心用軟控制芯片的信號處理過程,為以后實現控制信號處理及系統的在線重構打下了基礎。

[1]楊小牛,樓才義,徐建良.軟件無線電原理與應用[M].北京:電子工業出版社,2001.

[2]A.Dempster,M.Macleod.Use of Minimum-Adder Multipler Blocks in FIR Digital Filters[J].IEEE Transactions on Circuits and SystemsⅡ,1995.

[3]Xilinx.The Role of Distributed Ariehmetic in FPGA-based Signal Processining[Z]//The programmable Logic Data Book,2000.

[4]董金明,FPGA在軟件無線電技術實現中的應用[D].北京:北京航空航天大學,2001:47-48.