基于CPCI總線的雙CPU計算機系統設計*

王亞波 黃 蔚 宋曉科

(武漢第二船舶設計研究所 武漢 430205)

基于CPCI總線的雙CPU計算機系統設計*

王亞波 黃 蔚 宋曉科

(武漢第二船舶設計研究所 武漢 430205)

論文從提高效費比的角度出發,提出一種基于CPCI總線的雙CPU計算機系統設計方案,并通過搭建CAN總線通信網絡對雙CPU計算機系統進行了測試與驗證;根據測試結果,明確了后續重點研究的方向。

CPCI;雙CPU計算機系統;CAN總線;測試

Class NumberTP309

1 引言

計算機總線是計算機各部件之間進行信息傳輸的公共通道,隨著系統總線技術的發展,基于CPCI總線的計算機系統已廣泛應用于工業各領域,既降低了成本,增強了擴展性,又便于維修。傳統基于CPCI總線的計算機系統為單計算機系統,最多包含1個系統板卡和7個外設板卡。為了實現冗余備份,通常采用“雙機”方案,即設置兩套獨立、完整的計算機系統,一旦其中某個計算機系統的系統模塊或外設模塊出現故障,則該計算機系統整體被另一計算機系統所替代,系統資源浪費嚴重。為此,本文提出了一種基于CPCI總線的雙CPU計算機系統設計方案。

2 方案設計

2.1 硬件方案設計

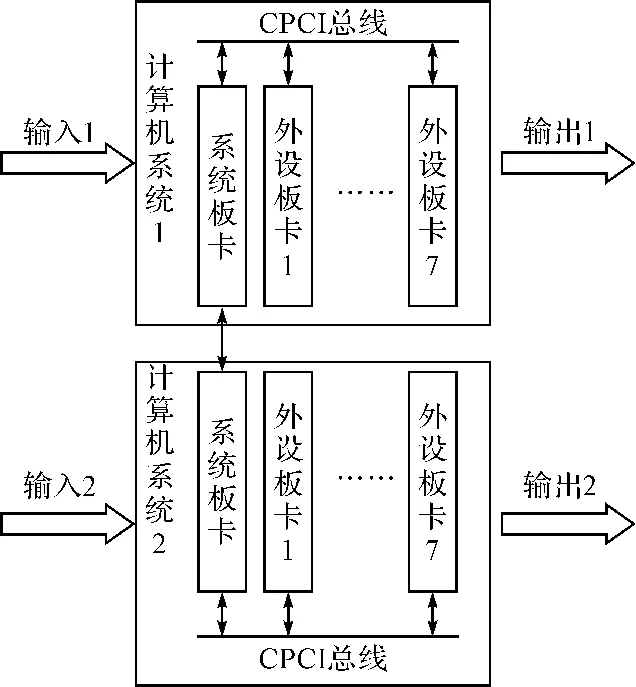

基于CPCI總線的雙冗余計算機系統原理框圖如圖1所示。

圖1 CPCI雙冗余計算機系統原理框圖

圖1 中,兩套計算機系統的組成完全相同,單套計算機系統均可獨立工作,并具有獨立的輸入輸出通道。兩套計算機系統的系統板卡通過相互連接實時傳輸關鍵信息,以實現兩套時間的協同工作及無縫切換[1~2]。

相比基于CPCI總線的雙冗余計算機系統,基于CPCI總線的雙CPU計算機系統除系統板卡雙冗余配置外,外設板卡、輸入輸出通道均配置一套,因此,在單系統槽的情況下,必須設計一個“CPCI橋”來實現兩個系統板卡對系統槽的共用與切換。基于CPCI總線的雙CPU計算機系統原理框圖如圖2所示。

圖2 CPCI雙CPU計算機系統原理框圖

圖2 中,主系統板卡和備份系統板卡同時插在“CPCI橋”上,通過“CPCI橋”實現兩塊系統板卡切換共用一個系統槽。

主/備系統板卡通過“CPCI橋”的冗余通信模塊周期性的進行狀態、數據等信息的交換并對數據進行完好性校驗,以實現主/備系統板卡在進行切換時,備份系統板卡能夠準確掌握主系統板卡的當前工作狀態,從而完成同步與穩定切換。

主/備系統板卡通過“CPCI橋”的故障檢測模塊進行實時通信,以實現相互之間的實時狀態監測,并以此作為主/備切換的依據。主/備系統板卡監測的故障類型包括采集通道故障、電源故障、CPU內部存儲器故障、CPU外部存儲器故障、外圍器件故障等[3]。

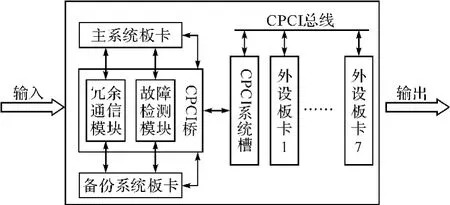

為了縮短開發周期,“CPCI橋”[4~5]硬件設計方案在研華6U工控機箱的基礎上進行修改實施。

研華工控機箱具有一個系統板插槽和七個設備板插槽,單系統槽無法實現雙CPU工作。為了解決此問題,在研華工控機箱的基礎上設計增加了一塊系統槽擴展板(即“CPCI橋”),不僅可實現系統槽的一分為二并,還可實現對雙CPU的仲裁,使得某一時刻只有一個CPU占用CPCI總線,而另一個CPU實時備份。“CPCI橋”結構框圖如圖3所示。

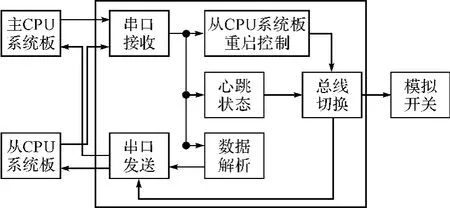

圖3中,CPU的仲裁是通過“CPCI橋”上的CPLD來實現的。CPLD通過串口與雙CPU系統板進行通信,每個CPU系統板正常工作時以100Hz的頻率定期向CPLD發送心跳包,當CPLD在10ms周期內沒有接收到主CPU系統板發送的心跳包時,將總線切換至從CPU系統板(這時主、從CPU系統板將進行交換,即主變為從、從變為主),從而實現雙CPU系統板的熱切換。

圖3 “CPCI橋”結構框圖

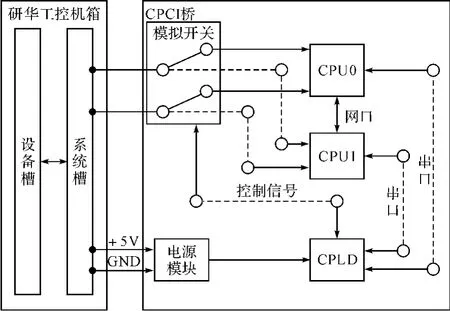

CPLD功能框圖如圖4所示,主要包括以下幾個模塊:

1)串口接收模塊:接收CPU系統板發送的心跳包和數據包等信息。

2)串口發送模塊:讀取CPLD當前狀態信息并發送給CPU系統板。

3)串口數據解析模塊:解析CPU系統板發送的數據并將信息傳遞給相應的任務模塊。

4)心跳狀態模塊:接收CPU系統板發送的心跳包,當在10ms周期內沒有接收到心跳包時發出CPU故障信號。

5)從CPU重啟控制模塊:當接收到從CPU重啟信息后,在從CPU重啟檢測CPCI外設過程中發出總線切換控制信號,并對從CPU重啟標志位進行設置。

6)系統復位模塊:實現對整個計算機系統的初始化。

7)時鐘生成模塊:生成系統所需的多個時鐘,如串口波特率、定時時鐘等。

8)總線切換模塊:依據心跳狀態模塊和從CPU重啟控制模塊的信息對總線是否切換進行裁決。

圖4 CPLD功能框圖

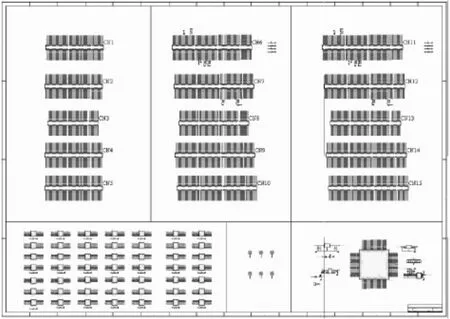

“CPCI橋”電路設計圖如圖5所示。

2.2 軟件方案設計

在雙CPU計算機系統正常運行時,外設板卡只與主CPU進行通信,外設板卡的驅動只在主CPU的操作系統上進行加載,從CPU的操作系統上默認是沒有加載外設板卡的。當主CPU發生故障時,從CPU需在不掉電的情況下按照主CPU當前的工作狀態繼續運行,由于從CPU的操作系統上默認是沒有加載外設板卡的,因此,雙CPU計算機系統軟件主要是要解決從CPU的操作系統在不掉電的情況下動態加載外設板卡驅動的問題。

圖5 “CPCI橋”電路設計圖

2.2.1 VxWorks管理PCI外設的分析

缺省情況下,VxWorks系統在啟動時會查找所有掛在PCI總線上的外設,初始化其配置空間,并在Host上為其分配Memory/IO映射地址。VxWorks系統中的PCI自動配置模式存在如下問題:

1)由于整個PCI初始化是在BIOS階段完成,初始化時沒有插入的外設如果在系統運行中插入,將無法得到識別。

2)對板卡中斷的ISR無法動態增加,新插入板卡產生的中斷無法得到響應,PCI中斷只能掛到鏈中而不能從鏈中移走。

3)初始化時在PCI地址段內連續分配映射地址,板卡拔出留下的空閑地址段不一定能夠適用于后面插入的新板卡,可能形成地址漏洞。

因此,實現驅動的動態加載要處理好地址映射和中斷的問題。

2.2.2 PCI設備地址映射[6]

在PCI規范中,每一個PCI外設都有一個配置空間,容量最大為256字節,稱為配置寄存器。配置空間的256個字節分為頭標區和設備關聯區。頭標區的布局如表1所示。

VxWorks系統上電后,BIOS中的POST軟件首先要把PCI總線上所有外設的存儲器地址和I/O地址映射到系統的內存區域中,并為其預留IO地址空間,以便在熱拔插時能將該預留空間分配給相應外設,從而實現外設驅動的動態加載。若在BIOS階段系統未檢測到某外設,待系統啟動后再插入則必須調用BIOS中的IO地址空間分配,目前VxWorks系統無法實現。

為解決上述問題,雙CPU計算機系統軟件設計采用如下方案:

對總線上所有外設進行定時掃描,對比記錄的原板卡插入狀態和掃描時讀取的外設ID、廠商ID等固化信息,以及時判斷槽位上發生的事件。若發現新插入的外設,則把預留的IO空間地址寫入PCI配置空間頭標區基地址寄存器中,以完成地址映射,地址映射完成后驅動程序就可根據分配的基地址訪問外設板卡。

2.2.3 中斷的響應與處理

根據PCI規范,所有PCI外設都可復用4個中斷級別,即A、B、C、D中斷。若要實現復用中斷,不但要在硬件上使用電平觸發機制,在軟件上也要做相應處理。

軟件處理單一外設的中斷復用主要由中斷服務程序完成。單一外設復用中斷時,驅動程序將掛接在指定的中斷號上,此時,在該中斷號上所出現的中斷一定是屬于該類外設的,用戶可在中斷服務程序中檢查所有該類外設,以確認中斷的來源并對產生中斷的外設進行服務。

在VxWorks系統內部,對應PCI的四個中斷源有四個保存復用中斷服務程序入口地址的中斷服務鏈表,對于這些中斷源,VxWorks系統會用intConnect()函數為系統連接一個中斷服務管理程序,在中斷到來時,中斷管理程序會依次從中斷服務鏈表中調用服務程序,檢查設備的狀態。同時,VxWorks系統為用戶提供了pciIntConnect()函數,使用該函數可將中斷服務程序掛接到對應的中斷服務鏈中。

雙CPU計算機系統同樣通過動態檢測外設板卡的拔插情況,當檢測到外設板卡插入時,把中斷號寫入到PCI配置空間頭標區的PCI_CFG_DEV_INT_LINE寄存器中,通過pciIntConnect()函數將中斷號和中斷服務函數進行連接。同理,當檢測到外設板卡拔出時,使用pciIntDisconnect()函數將中斷服務器函數和中斷號斷開,并使該中斷號空閑,以被其它外設板卡所使用。其中,中斷的相應操作在外設板卡驅動程序的加載和卸載函數中實現。

2.2.4 驅動動態加載的實現[7~8]

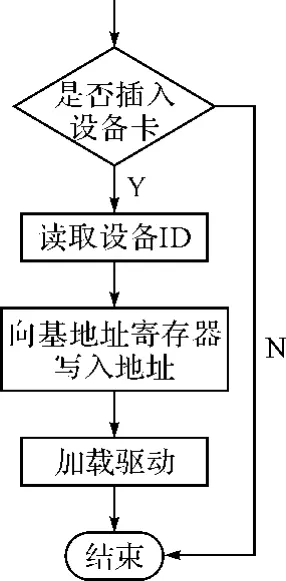

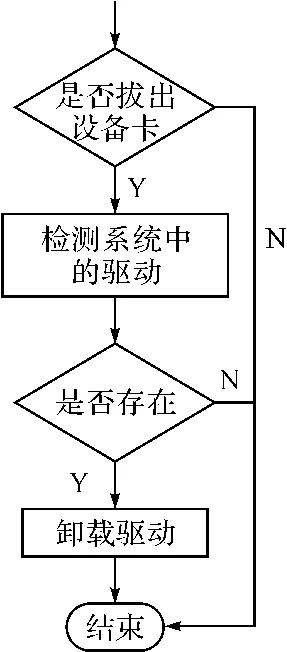

外設驅動動態加載流程圖如圖6所示。外設驅動動態卸載流程圖如圖7所示。

圖6 外設驅動動態加載流程圖

圖7 外設驅動動態卸載流程圖

2.2.5 CPU故障檢測

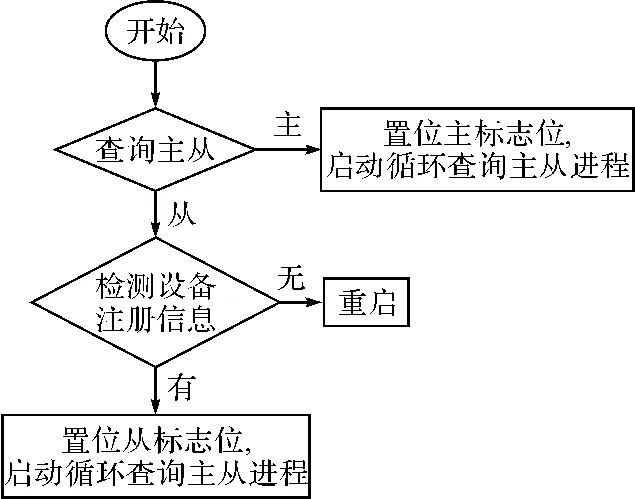

此程序主要功能是檢測CPU工作是否正常;判斷當前CPU工作狀態;檢測系統硬件注冊表中是否有相應外設。程序流程圖如圖8所示。

圖8 CPU故障檢測程序流程圖

圖8 中,主從查詢進程是定時查詢CPU狀態并設置標志位,其它進程根據主從標志信息決定程序執行方向。

3 通信穩定性測試

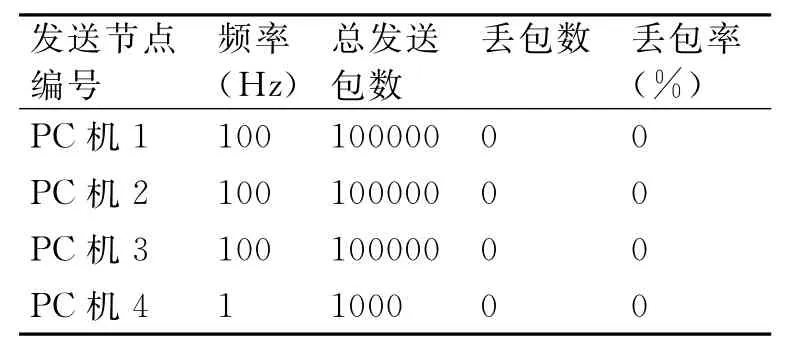

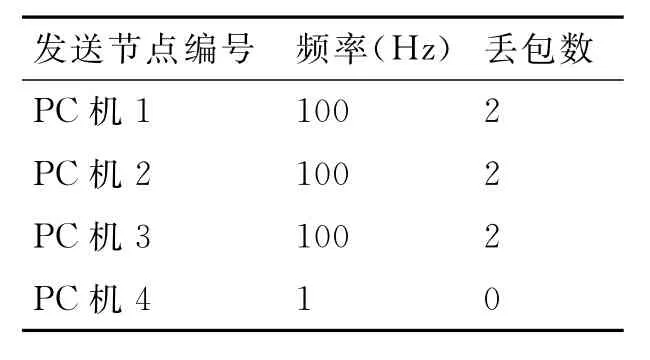

對雙CPU計算機系統進行CAN總線組網測試,其中四臺PC機作為發送節點,以固定頻率發送規定大小的數據;雙CPU計算機系統作為接收節點。四臺發送節點按照設定的優先級寫數據至CAN總線網絡,接收節點讀取各路數據[9~10]。組網測試結果如表2所示。

表2 樣機正常接收丟包測試表

從表2可以看出,雙CPU計算機系統在測試過程工作穩定,未出現任何丟包現象。

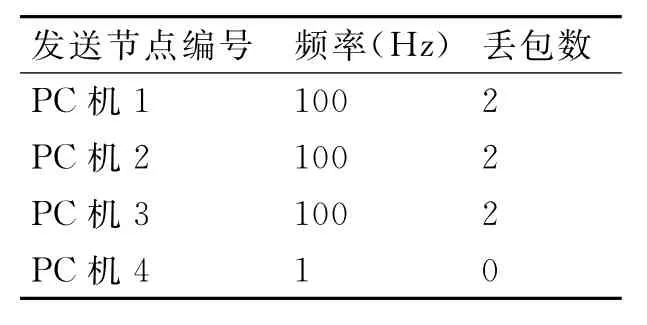

人為對雙CPU計算機系統進行主/從切換,測試結果如表3所示。

表3 雙CPU計算機系統主/從系統板卡切換一次接收丟包測試表

從表3可以看出,在雙CPU計算機系統運行時進行主/從系統板卡切換會發生丟包現象。分析認為,出現丟包現象主要有兩方面原因,一是切換時CAN通信板卡緩沖隊列里數據未被及時讀取導致數據丟失;二是切換時主/從系統板卡需要一定的時間周期才能完成卸載、查找可用外設等操作,因而導致數據丟失。

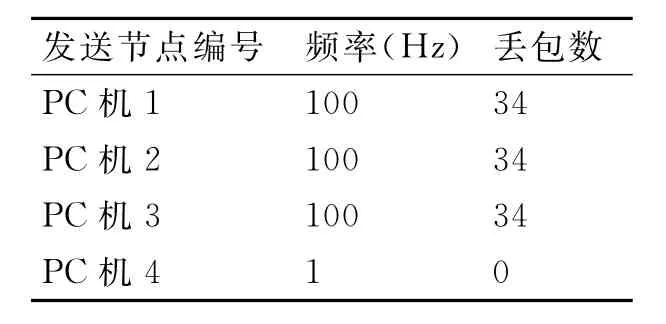

人為對雙CPU計算機系統進行從/主切換,測試結果如表4所示。

表4 雙CPU計算機系統從/主系統板卡切換一次接收丟包測試表

從表4可以看出,在雙CPU計算機系統運行時進行從/主系統板卡切換也會發生丟包現象,且丟包現象較主/從系統板卡切換時嚴重。分析認為,雙系統板卡熱備份時,主系統板卡出現故障,從系統板卡會接管外設成為主系統板卡;對原故障系統板卡進行更換后,原故障系統板卡會成為新的從系統板卡。為在下一輪熱切換中實現新的從系統板卡在主系統板卡出現故障時順利接管外設,從系統板卡需對BIOS內存進行分配,且BIOS內存分配時間至少需200ms,從而導致更嚴重的丟包。

人為對雙CPU計算機系統CAN通信板卡進行熱插拔,測試結果如表5所示。

表5 雙CPU計算機系統CAN通信板卡熱插拔一次接收丟包測試表

4 結語

上述測試結果表明,主/從系統板卡在切換時需一定的時間周期才能完成相應操作,否則會導致數據丟失,且切換時間≥200ms。因此,在后續研究中,可重點從加、卸載驅動、外設查找、BIOS內存分配等方面進行優化設計,進一步減少切換時間,使雙CPU計算機系統適應高更新率信息的傳輸。

[1]程剛,李明.基于CPCI總線的多DSP共享總線系統的設計與實現[J].現代電子技術,2007,6:151-153.

[2]包志強,吳順君,李明.基于CPCI總線的多DSP系統的接口設計[J].電子技術,2004,2:55-58.

[3]尚長興,俞定玖,季新生.雙機通信在CPCI總線上的實現[J].電子技術應用,2005,6:4-6.

[4]楊國先,陶霞,王子菡,等.基于雙CPU的切換及控制系統設計[J].微計算機信息,2006,22(10-2):268-269.

[5]侯伯亨,顧新.VHDL硬件描述語言與數字邏輯電路設計[M].西安:西安電子科技大學出版社,2001:6-15.

[6]李貴山,陳金鵬.PCI局部總線及其應用[M].西安:西安電子科技大學出版社,2002:5-21.

[7]魯菁,夏貴毅,黃國政.基于VxWorks的實時雙冗余系統設計[J].長春大學學報,2009,19(10):52-54.

[8]王學龍.嵌入式VxWorks系統開發和應用[M].北京:人民郵電出版社,2003:8-16.

[9]康郁爽.基于VxWorks的冗余通信控制系統研究與實現[D].西安:西安電子科技大學,2012:17-27,41-63.

[10]姜開.基于CAN總線的測試系統研究與設計[D].南京:南京航空航天大學,2004:32-59.

Design of Computer System of Double CPU Based on the CPCI

WANG Yabo HUANG Wei SONG Xiaoke

(Wuhan Second Ship Research and Design Insititute,Wuhan 430205)

Considering enhancing the effiency,a design proposal of computer system of double CPU based on the CPCI is demonstrated in this paper,and a prototype is made and tested by the means of communication web of CAN lines.Based on the testing result,the key research direction in next work is demonstrated.

CPCI,computer system of double CPU,CAN Bus,testing

TP309DOI:10.3969/j.issn.1672-9730.2015.11.030

2015年5月8日,

2015年6月24日

王亞波,男,碩士,工程師,研究方向:導航制導與控制。黃蔚,男,碩士,工程師,研究方向:導航制導與控制。宋曉科,男,博士,工程師,研究方向:電磁場與微波。