三極管并聯(lián)使用的分析

胡作平 李超

(珠海格力電器股份有限公司 廣東珠海 519070)

三極管并聯(lián)使用的分析

胡作平 李超

(珠海格力電器股份有限公司 廣東珠海 519070)

從目前空調(diào)實際應用的角度,分析了ULN2003驅(qū)動電路兩路并聯(lián)運行時可能造成電流不均衡的各種因素。介紹了選擇三極管并聯(lián)運行的思路和原則,提出了保證三極管并聯(lián)可靠運行的設(shè)計方法。

三極管并聯(lián);均流

目前空調(diào)控制器上的負載驅(qū)動電流較大時(如:電子膨脹閥等),考慮設(shè)計余量的要求,無法使用ULN2003單路驅(qū)動電路來驅(qū)動,此時會考慮用兩路或多路晶體管并聯(lián)來驅(qū)動,多管并聯(lián)會帶來管子之間電流均衡的問題,稱之為均流。若均流做得不好會導致驅(qū)動電路因晶體管無法飽和而失效,極限情況下甚至可能會燒壞ULN2003芯片。

1 影響三極管均流的主要因素

采用晶體管并聯(lián)主要為提高驅(qū)動電路驅(qū)動電流的定額,這就要求并聯(lián)的兩個或多個晶體管要盡量均勻地分擔電流,但是由于各晶體管的特性和參數(shù)不可能完全一致,這必將影響到并聯(lián)晶體管的均流。

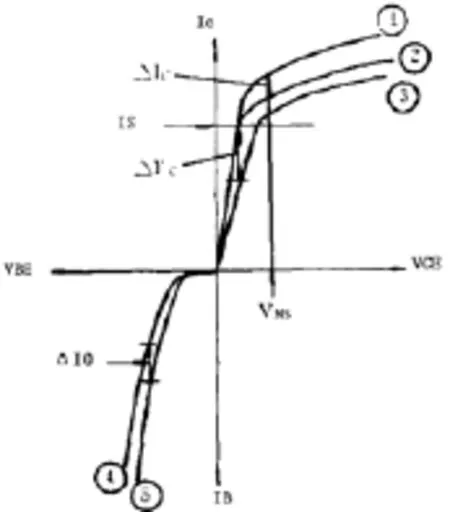

1.1 靜態(tài)特性的離散性

晶體管靜態(tài)特性參數(shù)hFE、Ube(sat)、Uce(sat)和主回路布線電阻是影響靜態(tài)均流的主要原因。如圖1,曲線①和②表示不同hFE的兩條特性曲線,可以看出,當晶體管進入準飽和態(tài)后,取相同的VNS值時,集電極電流IC將相差△IC。可見對不同hFE的晶體管來說,只要深飽和態(tài)的特性相同,當IC低于某個電流值IS時,就可以實現(xiàn)均流。因而較為深度的飽和有益于均流,當然這會影響關(guān)斷特性。

④和⑤為VBE與IB的關(guān)系曲線,由于VBE特性的不同,會造成基極驅(qū)動電流分配不均,從而引起IC的差異。同理比較②和④可知,當VCE特性不同時,即使在深飽和態(tài),IC也會相差△IC。

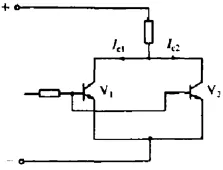

晶體管集電極和發(fā)射極側(cè)的布線電阻也會對靜態(tài)均流有較大的影響,尤其當集電極電流較大時。但因布線的差異性布線電阻不同,且在三極管使用場合本身布線電阻較小,因此直接并聯(lián)時會受集射結(jié)的電阻影響較大。如圖2,當兩只晶體管并聯(lián)連接時,具有相等的集射極電壓VCE。假如兩管電流分配不均衡,V1的集電極電流增加而提前進入飽和,此時V1將有一個較小的集射結(jié)電阻。當然由于集射結(jié)電阻具有正的溫度系數(shù)(當IC1大于IC2時,V1的結(jié)溫將升高,其集射結(jié)電阻將增大,從而自動減小V1的集電極電流),對電流分配不勻會起到一定自動補償?shù)淖饔茫@種調(diào)節(jié)是非常弱的,尤其在PWM控制場合。

同樣,這樣并聯(lián)晶體管的基射結(jié)也能對電流的分配起自動均流作用。基射結(jié)的等值電路可以看成是一個二極管和一個結(jié)電阻串聯(lián)。二極管正向電壓降的溫度系數(shù)是負的,結(jié)電阻的溫度系數(shù)則是正的。基射結(jié)的總溫度系數(shù)視基流的大小而定。當基流較小時,結(jié)電阻上的壓降小于二極管上的壓降,故溫度系數(shù)是負的。相反,基流增大后,基射結(jié)的溫度系數(shù)變正。在這種并聯(lián)條件下,所有管子的基射極電壓相等,如果集電極電流較大會具有較高的結(jié)溫,此時基射結(jié)的正溫度系數(shù)會使基流減小,從而迫使它分擔較小的負載電流。

圖1 晶體管靜態(tài)綜合曲線

圖2 晶體管并聯(lián)電路

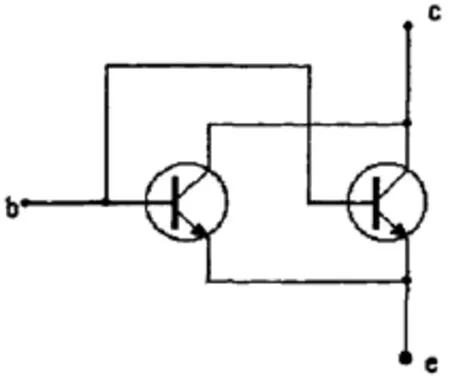

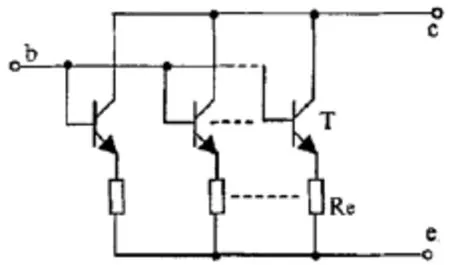

圖3 三極管并聯(lián)運行基極直接相連圖

上述這兩種均流效應僅對穩(wěn)態(tài)而言,為穩(wěn)態(tài)均流效應,但其均流作用較弱,而且對PWM控制使用的場合調(diào)整非常有限,為達到滿意的均流效果,仍需采取必要的均流措施。

1.2 開關(guān)特性的離散性

晶體管開關(guān)特性(ton、tstg、tf)和主回路連線的分布電感是影響并聯(lián)時動態(tài)均流的主要因素。其中存儲時間tstg長的關(guān)斷時電流不均衡幅值最大,這是因為tstg越長,晶體管關(guān)斷得越慢,電流大部分從該管流過,造成電流分配不均。當然,tstg短的元件,關(guān)斷時的基極反抽電流會迅速減少,使tstg長的元件基極反抽電流增大,從而縮短tstg加快其關(guān)斷過程,有一定改善均流作用。

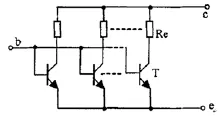

圖4 三極管并聯(lián)射極接均流電阻示意圖

主回路接線的分布電感對動態(tài)均流的影響也不容忽視。發(fā)射極側(cè)連線的分布電感會影響到基極和集電極側(cè)的電流分配,因而在接線時使這些連線應盡可能短,且保證一致。而基極分布電感的存在,對晶體管關(guān)斷時均流的自調(diào)整會有一定作用。

以上分析了影響晶體管并聯(lián)運行均流的各種可能因素,下面討論三極管并聯(lián)使用時的具體設(shè)計方法。

2 并聯(lián)用三極管的設(shè)計

由上面的分析可知,引起電流不均衡的因素是hFE、Ube(sat)、Uce(sat)和ton、tstg、tf的離散性以及連接導線電阻和電感的不同。現(xiàn)實應用中參數(shù)完全相同的晶體管是不存在的,只能針對其中某一特性(如hFE)進行選擇,然后找出折衷方案并從設(shè)計上采取措施,使并聯(lián)運行時IC盡可能一致。

2.1 獨立的基極電阻

按圖3方式連接時,一個控制口給兩個NPN管子的基極供電,由于每個管子VBE和HFE的初始值不相同,且隨著溫度變化相差更大,由此引發(fā)的問題是可能在極限條件下其中一個管子不能正確的偏置,VBE比較低的管子偏置電阻的電流非常大,而另一個管子的偏置電流就顯得非常小。如果IB太小,假定IC一定的話H=IC/IB,在溫度低的情況下,很容進入放大區(qū),導致VCE較大,從而使管子無法進入飽和而失效。

因此即使驅(qū)動口可以偏置幾個NPN的管子,每個管子也要有獨立的基極電阻,這樣可實現(xiàn)在VBE存在差別的情況下,通過此電阻實現(xiàn)一定的均流,確保電流的獨立。

圖5 三極管集電極接均流電阻示意圖

2.2 接均流電阻

從2.1的分析我們知道,晶體管集電極和發(fā)射極側(cè)的布線電阻會對靜態(tài)均流有較大的影響,有一定自動均流的作用,但效果較差,因此在實際使用中會人為在集電極或發(fā)射極增加均流電阻,使晶體管的均流主要受此電阻調(diào)節(jié)。

2.2.1 發(fā)射極回路里串入均流電阻

如圖4,其工作原理是利用射極電阻的負反饋作用,使并聯(lián)晶體管達到均流目的。顯然,均流精度與所串聯(lián)的均流電阻阻值有關(guān),阻值越大均流效果會越好,但是阻值大能量消耗也大。采用這種方法的優(yōu)點是均流效果好,缺點是均流電阻上要消耗能量,均流電阻要選擇較大功率的電阻,多路并聯(lián)時串入電阻數(shù)量較多。電阻的取值既要考慮均流效果,又不能使其損耗太大,通常取射極電阻壓降UReax<lV。

2.2.2 集電極回路里串入均流電阻

目前空調(diào)外機控制器一般驅(qū)動場合大部分是使用ULN2003來驅(qū)動的,像2003這種達林頓結(jié)構(gòu),晶體管特性參數(shù)的離散性比單管還要大。但因2003芯片電路限制,無法在晶體管射極接入負反饋電阻,如圖5所示。我們通常采取的方法是在ULN2003的輸出口即集電極接入均流電阻,均流電阻阻值要大于集射結(jié)電阻,這樣并聯(lián)晶體管的集射極電壓將主要由均流電阻決定,從而改善ULN2003兩路并聯(lián)使用時晶體管的均流性。同時為保證電路的可靠性,三極管使用時應留有一定余量,取最大工作電流為額定電流的70%左右,并聯(lián)時留取的余量一般為50%~60%,余量的大小要大于不均電流成分△IC,這樣即使在IC略有不均的情況下三極管仍然能夠安全地工作。

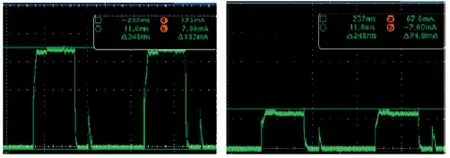

圖6 ULN2003兩路并聯(lián)使用時最大電流偏差

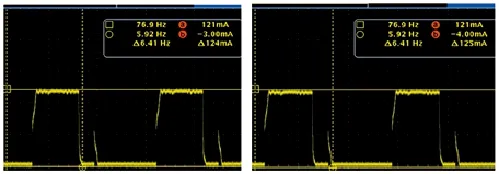

圖7 ULN2003輸出接入1Ω均流電阻后兩路輸出電流

3 實驗結(jié)果與結(jié)論

根據(jù)ULN2003參數(shù)偏差模擬2003輸出電流IC最大偏差測試結(jié)果如圖6所示,晶體管飽和壓降UCE(sat)偏小的一路輸出電流為182m A,偏大的一路輸出電流為74mA,兩路相差108mA,我們可以看到由于晶體管靜態(tài)參數(shù)差異導致的輸出不均流是非常大。根據(jù)前面的分析方法,我們在2003輸出集電極接入1Ω的均流電阻后測試兩路輸出電流如圖7所示,我們可以看到接入均流電阻后對2003兩路輸出的均流改善是非常大的。

本文對晶體管的并聯(lián)使用進行了較為深入的分析和討論,介紹了晶體管并聯(lián)的設(shè)計方法,通過測試可以確認按此方法使用三極管并聯(lián)時是安全可行的。

[1]華成英.模擬電子技術(shù)基礎(chǔ).清華大學出版社,2006年

[2]劉宏,黃錦恩,王離九.大功率晶體管并聯(lián)研究.電力電子技術(shù),1994

[3]童福堯.大功率晶體管GTR的并聯(lián)技術(shù).電力電子技術(shù),1993

Analysis of transistor used in parallel

HU Zuoping LI Chao

(GREE Electric Appliances, Inc. of Zhuhai Zhuhai 519070)

From the perspective of the current actual air-conditioning applications, and analyzes the current may cause uneven ULN2003 driver circuit when two parallel variety of factors. Select transistor parallel operation introduced ideas and principles of design method to ensure reliable operation of the transistor in parallel.

Transistors in parallel; Current uniformity