DDR2硬件設計中反射的消除

賀 敬

(內蒙古機電職業技術學院電氣工程系,呼和浩特 010070)

1 引言

隨著技術的進步,電路設計中對于DDR信號傳輸速度有了更高要求,當下800 Mbps 的DDR已成為主流,且逐漸向更高速度邁進。信號傳輸速度越高,PCB設計中就需要考慮更多因素如:PCB疊層結構、串擾、阻抗、電源完整性等。從而達到時序的嚴格匹配,波形的完整與準確。

在DDR2的設計時, 互聯通道的一個重要參數為阻抗,為了做到阻抗匹配,信號線必須是均勻傳輸線,以保證走線阻抗恒定。單端走線時,信號傳輸速度為6in/ns,阻抗匹配電阻為487hms且必須被用到所有的單端信號上,但其缺點會導致信號占空比不平衡。

2 PCB中的反射

反射是信號源端與負載端阻抗不匹配,信號在傳輸時受到瞬態阻抗產生的回波,信號功率經過信號線A傳送到信號線B時,由于阻抗不匹配未被B完全吸收,返回到了信號源端形成了發射。也就是說,傳輸線上的阻抗不相等就會導致信號出現反射現象(可能在傳輸過程中遇到的過孔,PCB轉角等)如圖1所示。

在阻抗相等的匹配情況下,當信號在從特性阻抗Zo1向特性阻抗Zo2傳輸過程中,信號功率被吸收而無溢出因此不會產生反射。在阻抗不匹配情況下即Zo1≠Zo2時,則會產生信號反射,這種情況在電路硬件設計中是不可避免的。設輸入信號的幅度為V1,按原來方向傳輸的信號幅度為V3,如果阻抗相等,則有V1=V3,不會有反射產生,如果Zo1≠Zo2,會有反射信號V2,這樣在兩段導線交界面上觀察到的信號幅度應為V1+V2。因此在傳輸信號的邊緣尖端抖動。

數據線在信號傳輸中可以看作是單端網絡,終端連接是單一負載,可以考慮單電阻端接的方法,在串行端接串行匹配,可有效消除二次反射且無需直流電源。更加有利于高密度布線。但這里的局限是不適合太高的傳輸速度。

3 信號完整性分析

3.1 確定多層PCB板的層疊結構

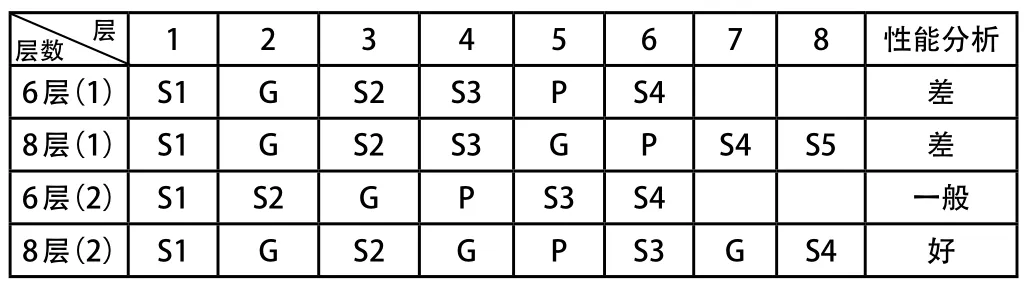

從設計者的角度來說,電路板層數越多越易于布線,但是電路板制作成本和難度也會隨之增加。因此,在考慮具有特殊布線要求的信號線如差分線、敏感信號線等的數量和種類的同時,應當分析電路板的布線密度,從而確定信號層的層數;然后根據隔離、抗干擾和電源的種類的要求來確定內電源層的數目。這樣就可以確定電路板的板層結構。其中對多層PCB板層分析比較如表1所示:

表1 PCB板層分析

在8層電路板設計中,信號層S1、S2、S3、S4都必須找到電源層與底層作為標準參考平面,因此我們選擇8層(2)的設計機構。如果電源層與底層不相鄰,會影響其耦合度,無法形成寄生小電流。

八層電路板具體設計中各層使用不同材質,信號層、電源層、地層的排列順序,以及各層厚度各不相同。PCB的表層,即第一層(TOP層)和第八層(BOTTEM)層直接采用銅箔,而內層采用Core銅箔,Core之間用PP填充。

3.2 DDR2布線

本設計的DDR2布線中,數據線采用ODT(核心整合終結器)技術,ODT相當于戴維南并行接法,起到終端阻抗匹配的作用。靈活使用上下拉電阻,使輸出電平平衡,減小因占空比失調。系統使用圖2所示的雙向源端端接方案,利用IBIS模型仿真確定端接電阻的數值分別為 : RS(B0)=47 ohms,RS(A0)=10 ohms。

從仿真圖形對比可以看出,加入匹配電阻后使原來信號的尖端毛刺消失,上升與下降波形更加陡峭,信號質量提升。

4 結論

經過對信號反射的分析和仿真,可得到以下結論:

(1)為了防止數據線終端反射信號我們增加大量的終端電阻。但這樣增大了靜態直流功率。

(2)信號存在反射是因為ZL≠Z0,即阻抗不匹配。為了減小反射信號的干擾盡量使阻抗達到理想狀況,ZL=Z0使輸線上的能量能完全被負載吸收。

(3)終端電阻的大小是由信號線的信號比和反射率決定的,阻值太小會減弱匹配效果,阻值太大會吸收較大的電流增加電源消耗。

[1]Brennan C,Tudor C,Schroeter E,et al.Signal Integrity and PCB layout considerations for DDR2-800Mbps and DDR3Memories.CDNLIVE Silicon Valley:Cadence .2007.

[2]趙天云,王洪迅,郭雷,畢篤彥.DDR2 SDRAM控制器的設計與實現[J].微電子學與計算機,2005(03).

[3]劉瑰,朱鴻宇.通用DDR SDRAM控制器的設計[J].微型機與應用,2004(08).